Semiconductor device and manufacturing method therefor

A manufacturing method and semiconductor technology, applied in the direction of semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of not fully considering SCSOA, etc., and achieve the effect of improving RBSOA and preventing the reduction of reverse withstand voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach 1

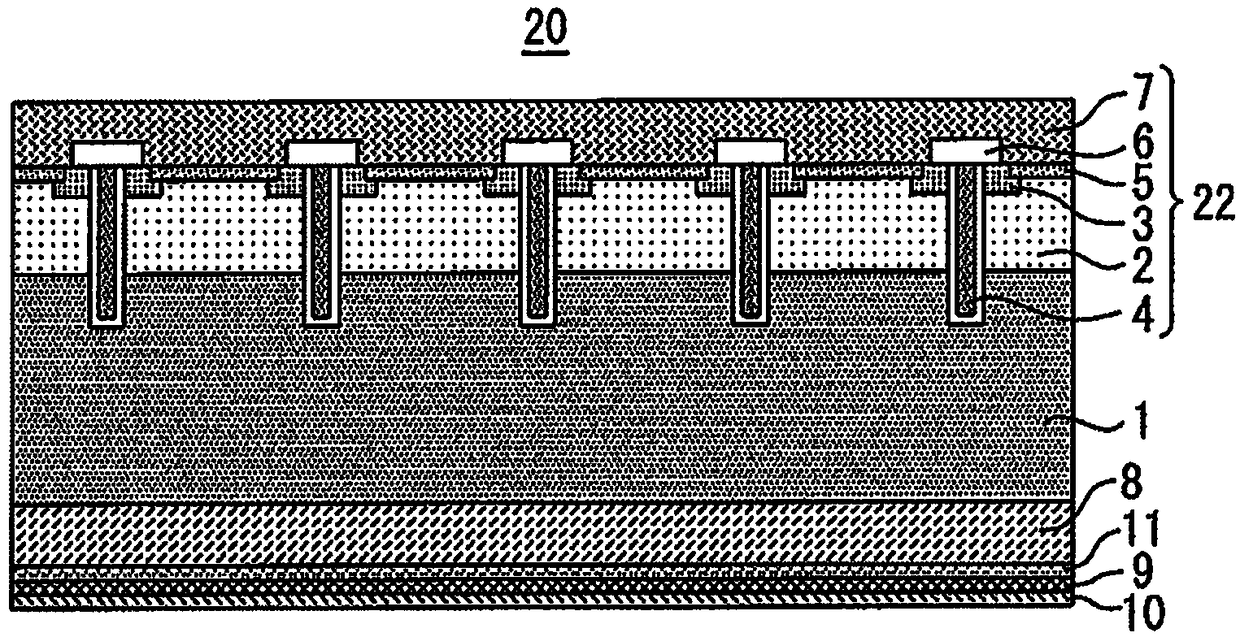

[0062] figure 1 It is a figure which shows the semiconductor device 20 which concerns on Embodiment 1 of this invention. The semiconductor device 20 according to Embodiment 1 is an insulated gate bipolar transistor (IGBT) including a trench gate. exist figure 1 Among them, a semiconductor device 20 includes a substrate 1 . Substrate 1 is made of silicon and has n-type conductivity. Since the substrate 1 functions as the drift layer 1 of the IGBT, the substrate 1 is also referred to as the drift layer 1 below.

[0063] On the drift layer 1, the MOSFET part 22 is provided by surface process. MOSFET portion 22 includes p-type base layer 2 , n + -type emitter layer 3 , trench gate 4 , p + -type layer 5 , interlayer insulating film 6 , and emitter electrode 7 . The p-type base layer 2 is disposed on the surface of the drift layer 1 . The p-type base layer 2 is pn-junctioned with the drift layer 1 to form a depletion layer. A plurality of n + -type emitter layers 3 are formed...

Embodiment approach 2

[0117] Figure 25 It is a figure which shows the semiconductor device 50 which concerns on Embodiment 2 of this invention. In Embodiment 1, the collector layer 9 is formed over the entire back side of the drift layer 1 . On the other hand, in Embodiment 2, the p-type collector layer 9 is formed directly under the cell portion 62 , and the p-type collector layer 9 is formed directly under the gate wiring portion 64 and the withstand voltage holding portion 66 . A p-type collector layer 14 having a low impurity concentration. Except for this point, the semiconductor device 50 according to the second embodiment has the same structure as the semiconductor device 20 according to the first embodiment. Therefore, the following description will focus on the differences from Embodiment 1, and the same or corresponding elements between Embodiment 1 and Embodiment 2 will be assigned the same reference numerals, and the description will be simplified or omitted.

[0118] Such as Figu...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Resistivity | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More