Radar digital pulse compression direct current removing method based on FPGA

A digital pulse and direct current removal technology, which is applied in the radar field, can solve problems such as the difficulty of cleaning the light window of a large area array CCD, achieve the effect of occupying less memory, less hardware resources, and ensuring computing efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] Preferred embodiments of the present invention will be specifically described below in conjunction with the accompanying drawings, wherein the accompanying drawings constitute a part of the application and are used together with the embodiments of the present invention to explain the principle of the present invention.

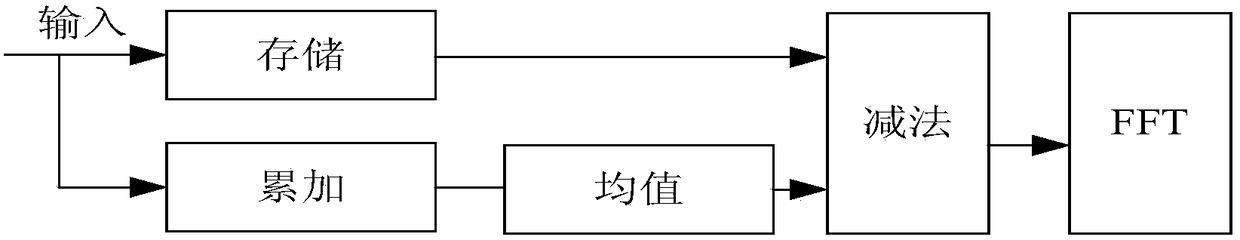

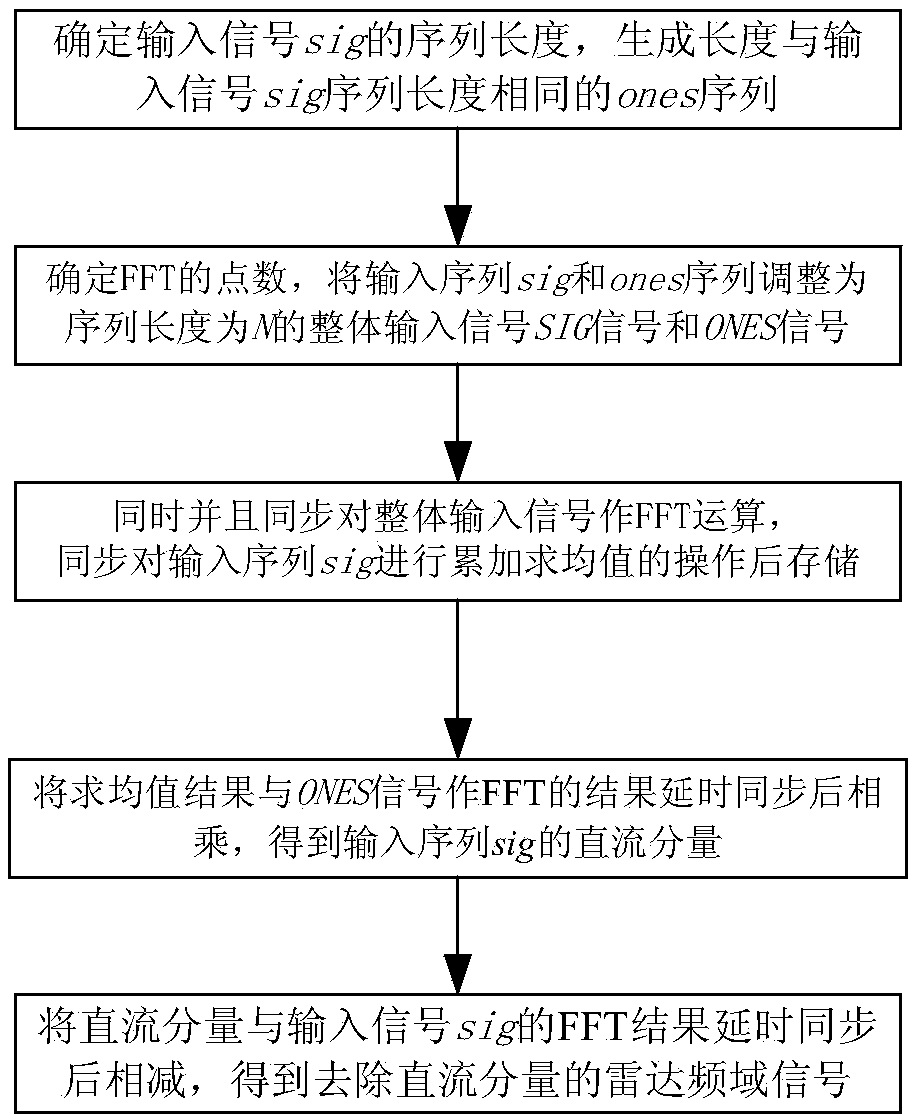

[0034] A specific embodiment of the present invention discloses a method for removing direct current by compressing radar digital pulses based on FPGA, such as figure 2 shown, including the following steps:

[0035] Step S1, determine the sequence length of the input signal sig, and generate a ones signal of a sequence length equal to the input signal sequence, all of which are 1s;

[0036] The input signal is the sig signal before pulse compression, which contains a DC component, expressed as the sum of the DC component and the AC component, that is: where X(n) is expressed as a DC component, Expressed as the AC component, f i Indicates the frequ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More