Double-FPGA cooperative work method for deep neural network

A deep neural network and collaborative work technology, applied in the field of airborne intelligent computing, can solve problems such as limited hardware resources, and achieve the effect of improving computing speed and parallelism

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018] The present invention is described in further detail.

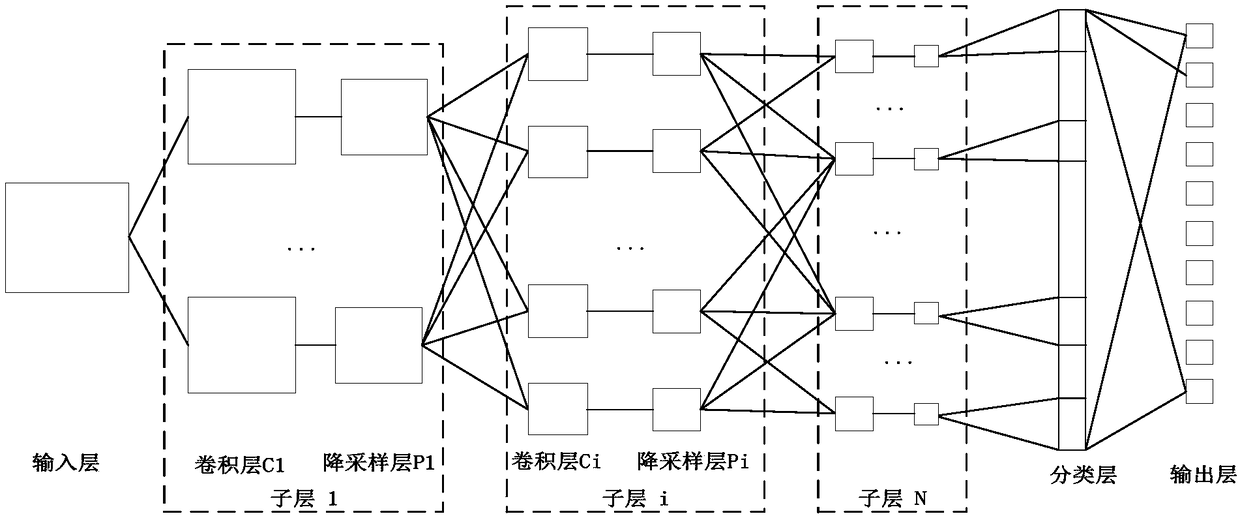

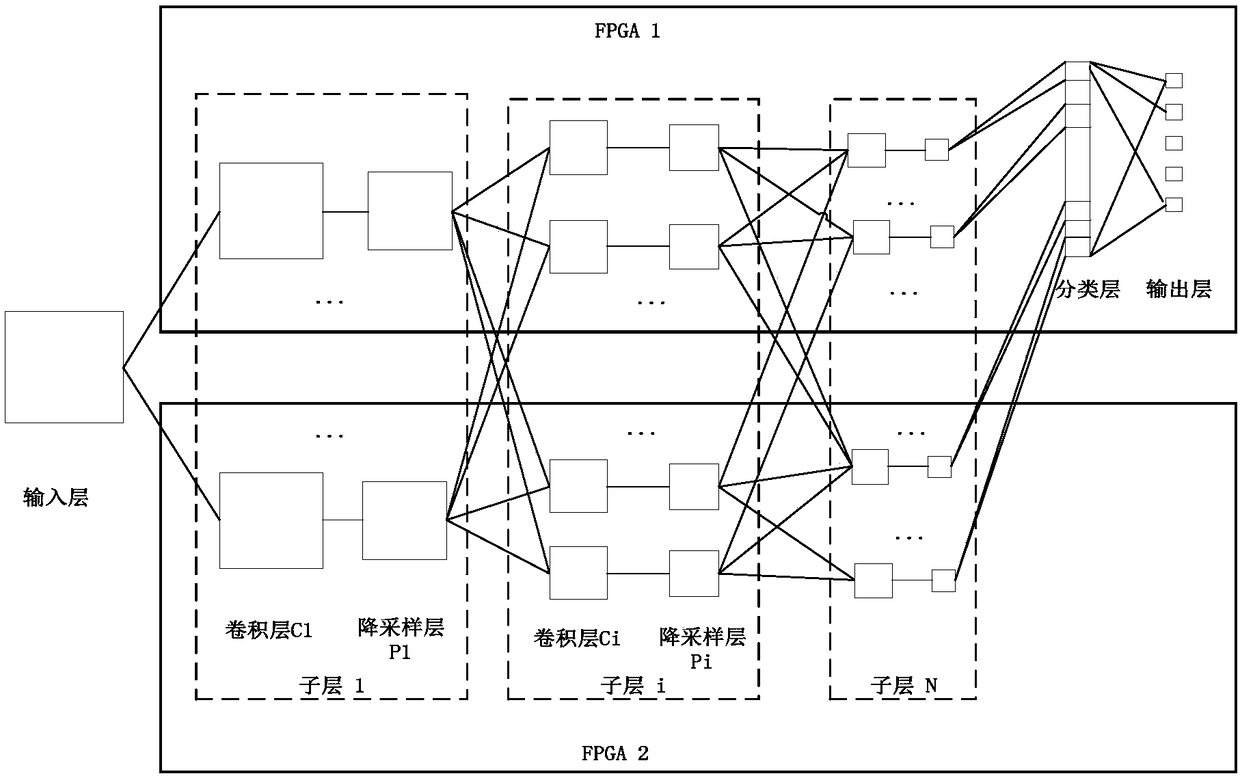

[0019] When the present invention is implemented, it mainly considers the requirements of the neural network model for hardware resources and data interaction. Compared with a single FPGA, it can support parallel computing of a larger-scale neural network without dynamic reconfiguration. . Taking LeNet5 as an example, the network includes an input layer, a convolutional layer C1, a downsampling layer P1, a convolutional layer C2, a downsampling layer P2, a fully connected layer F1, a fully connected layer F2, and an output layer.

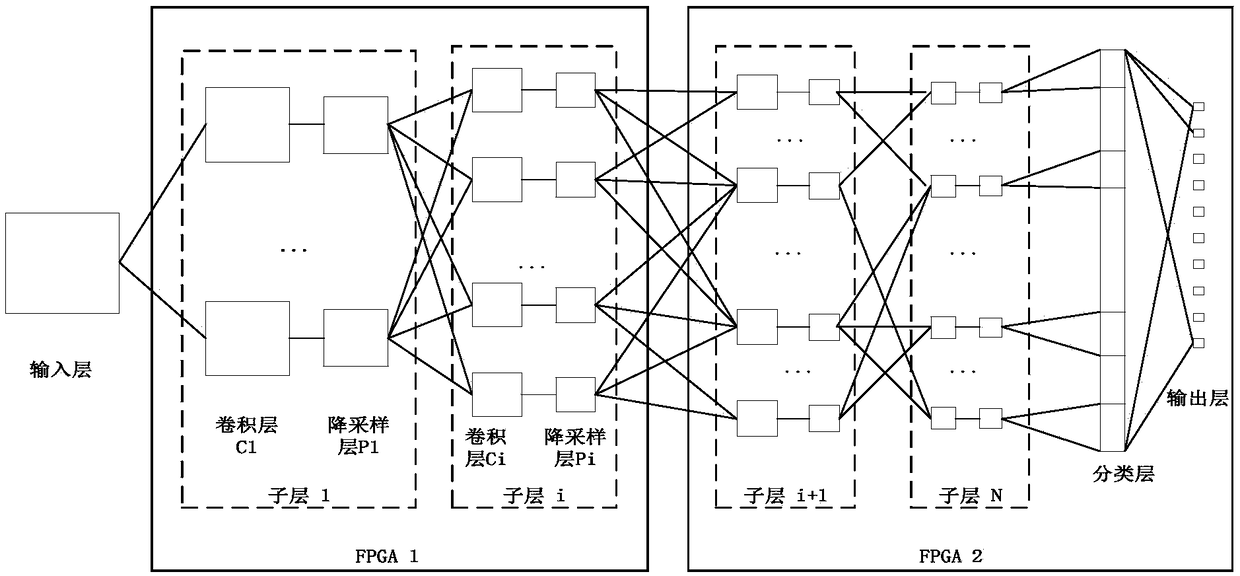

[0020] Serial division method: According to the calculation amount of the network, the convolutional layer C1 and the downsampling layer P1 are implemented on the first chip, and the convolutional layer C2, the downsampling layer P2 and two fully connected layers are implemented on the second chip , the number of network layers implemented on the second chip is more, but the calculation...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More