DGS filter, printed circuit board, and filtering device

A printed circuit board and filter device technology, applied in the field of communication, can solve the problems of unsuitable multilayer printed circuit boards and reduced filtering ability of DGS filters, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

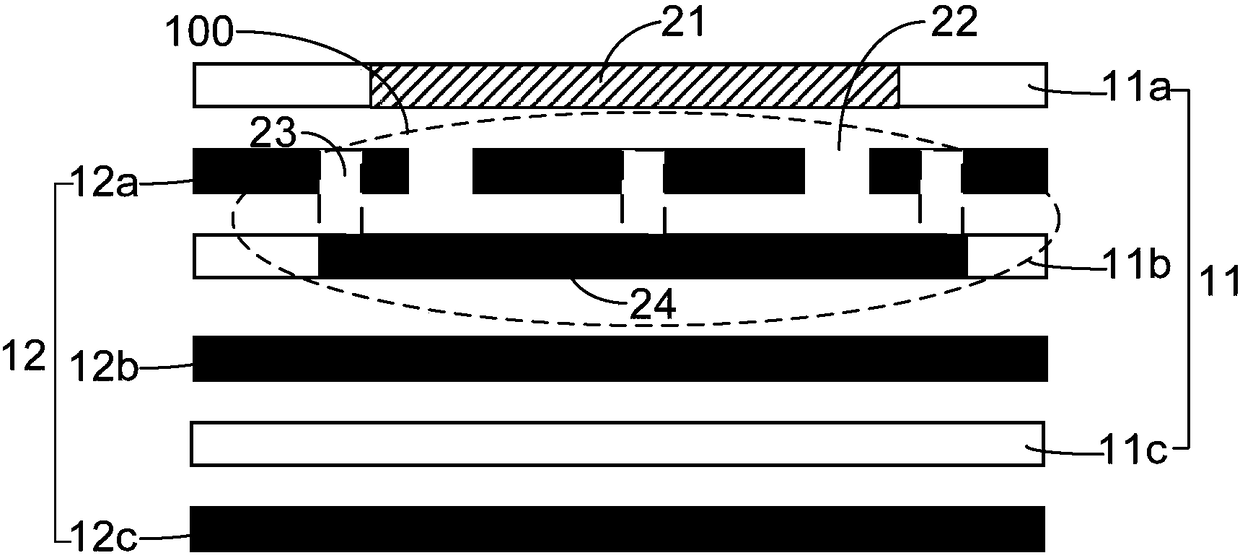

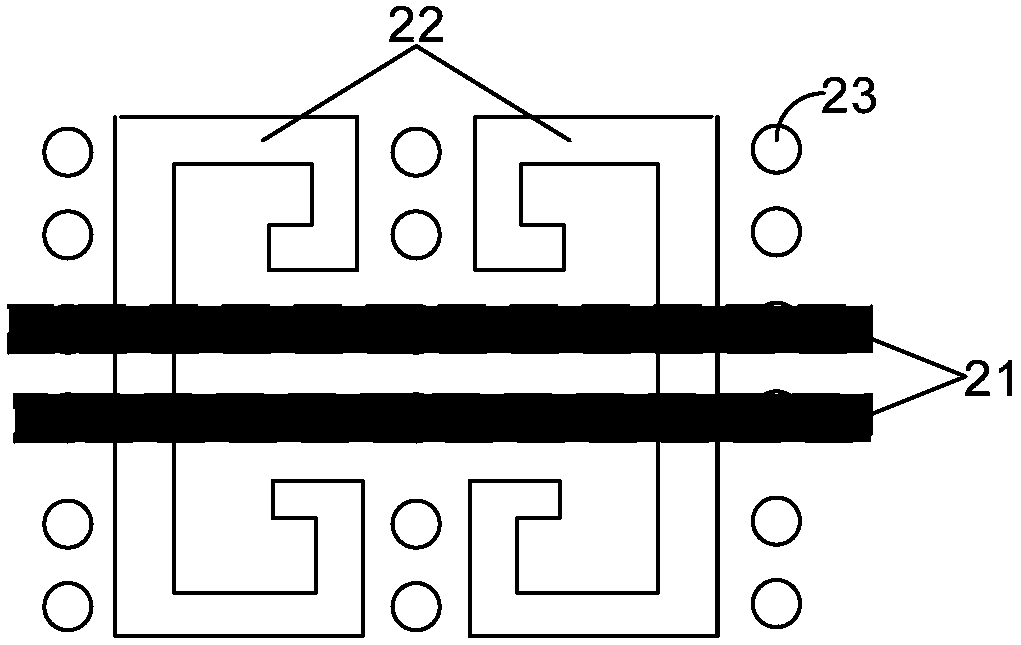

[0038] The technical solutions in the embodiments of the present invention will be described in detail below with reference to the drawings in the embodiments of the present invention.

[0039] In addition, the terms "first" and "second" are used for descriptive purposes only, and cannot be understood as indicating or implying relative importance or implicitly specifying the quantity of indicated technical features. Thus, a feature defined as "first" and "second" may explicitly or implicitly include one or more of these features. In the description of the present invention, unless otherwise specified, "plurality" means two or more.

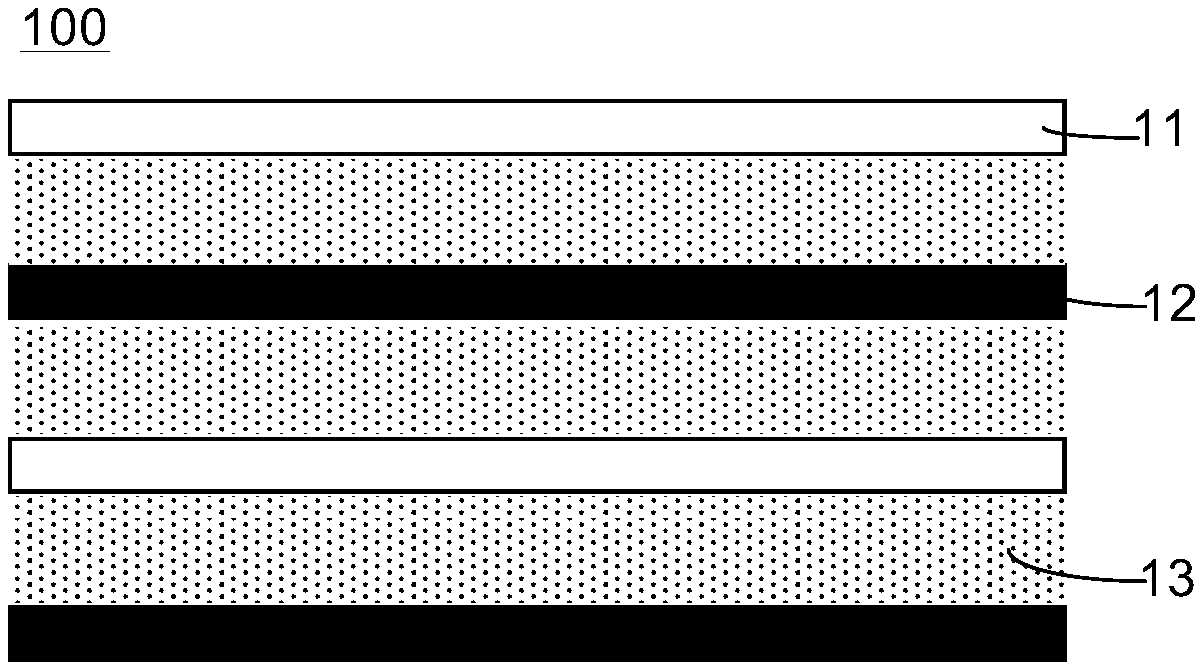

[0040] The DGS filter provided by the embodiments of the present invention can be applied to a multilayer printed circuit board, and the multilayer printed circuit board includes at least two reference layers and at least two wiring layers, and each wiring layer corresponds to a A reference layer (or multiple wiring layers may correspond to the s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com