Multi-valued quantizer output design and assignment method

A quantizer and output technology, applied in the computer field, can solve problems such as slow development and achieve the effect of reliable implementation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

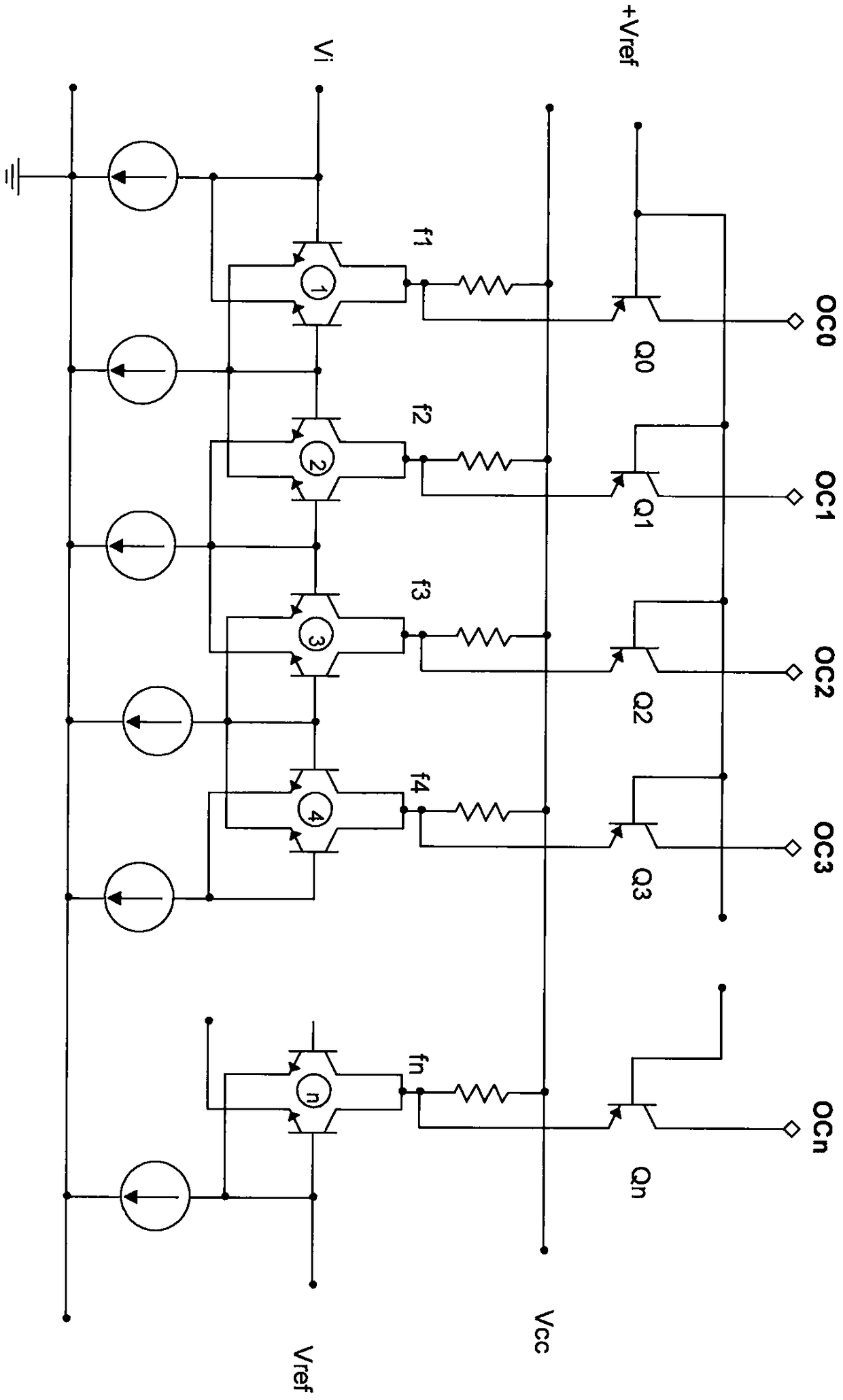

[0035] refer to figure 1, using several PNP transistors Q0, Q1, Q2,...Qn as output drive tubes, Q0, Q1, Q2,...Qn drive tube emitters and patent 00105165.2 Figure 8 F1, F2, F3, ..... Fn are connected, the bases of Q0, Q1, Q2, ... Qn drive tubes are connected to each other and connected to the positive pole +ref of the reference power supply, Q0, Q1, Q2, Each collector of ...Qn forms an open-collector output, which in turn forms OC0, OC1, OC2...OCn output.

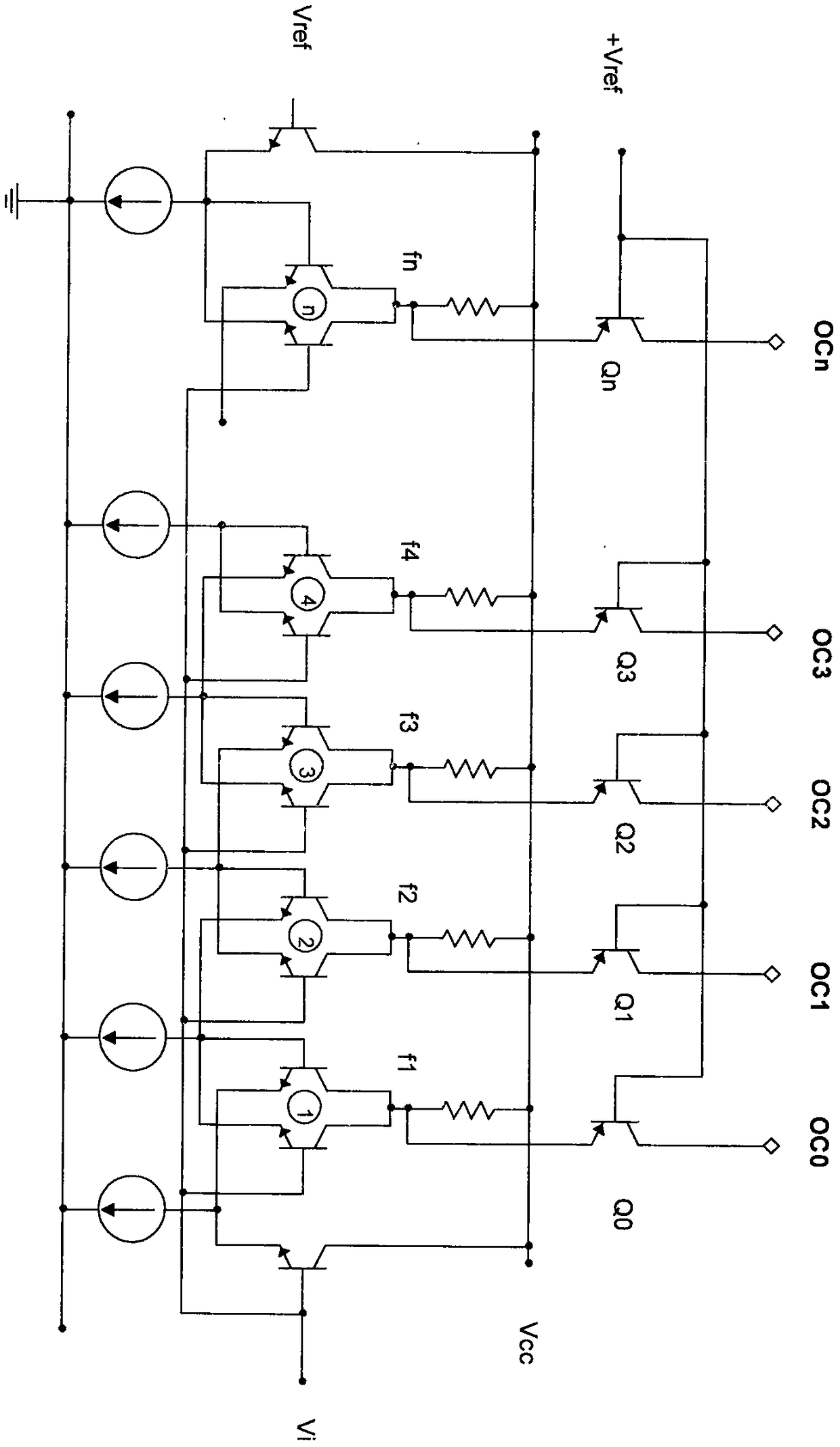

[0036] refer to figure 2 , using a number of PNP transistors Q0, Q1, Q2,...Qn as output drive tubes, Q0, Q1, Q2,...Qn drive tube emitters and patent 00105162.8 Figure 8 F1, F2, F3, ..... Fn are connected, the bases of Q0, Q1, Q2, ... Qn drive tubes are connected to each other and connected to the positive pole +ref of the reference power supply, Q0, Q1, Q2, Each collector of ...Qn forms an open-collector output, which in turn forms OC0, OC1, OC2...OCn output.

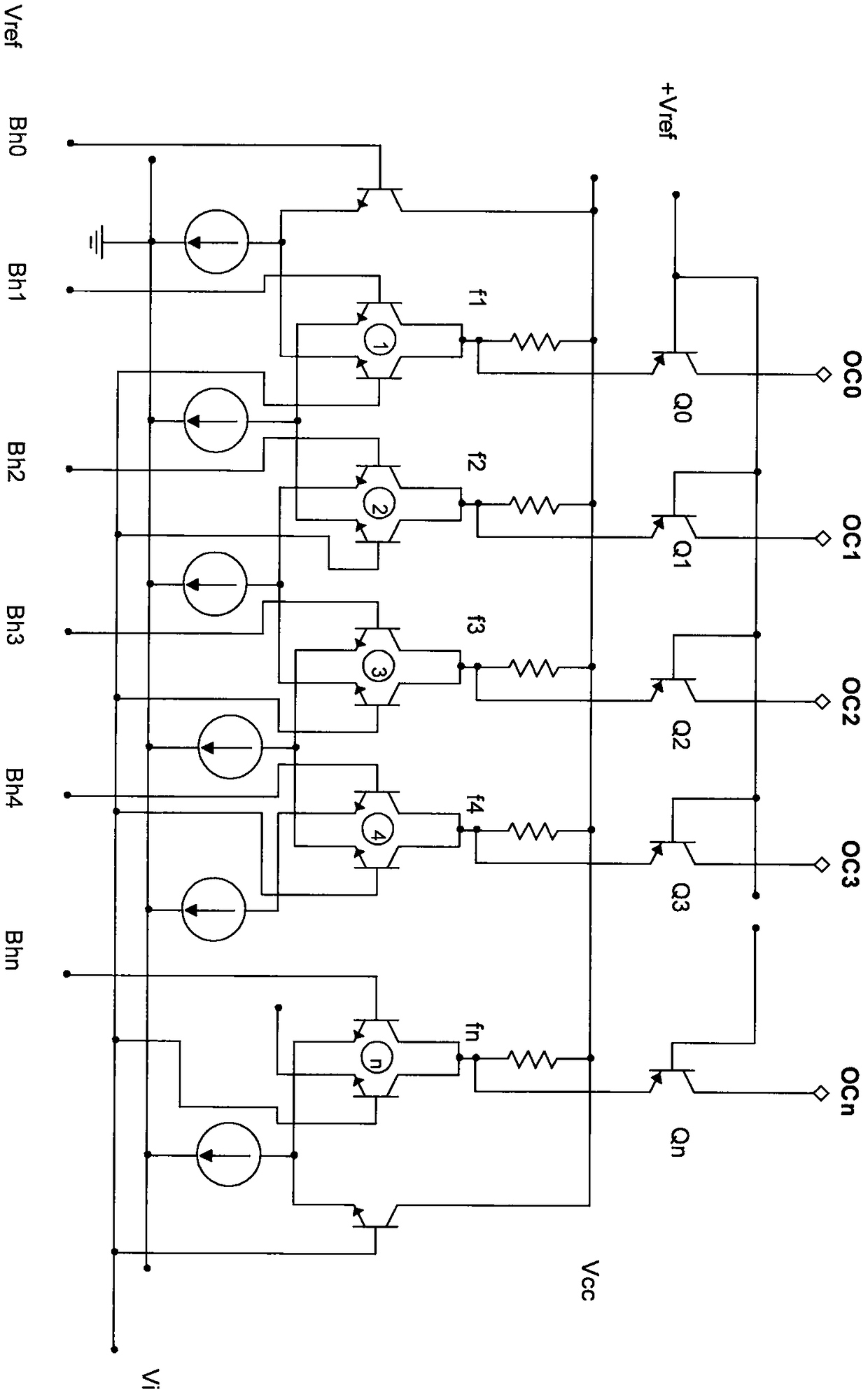

[0037] refer to image 3 , using several PNP transistors...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More