Memory structure and forming method thereof

A technology of memory and storage area, applied in the direction of electric solid-state devices, semiconductor devices, electrical components, etc., can solve the problems of poor read and write ability, low read noise capacity, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0037] The memory structure of the prior art has many problems, for example, the static noise capacity of the static memory is small, and the anti-interference ability is poor.

[0038] Combining with the memory of the existing technology, the reasons for the small static noise capacity and poor anti-interference ability of the memory are analyzed:

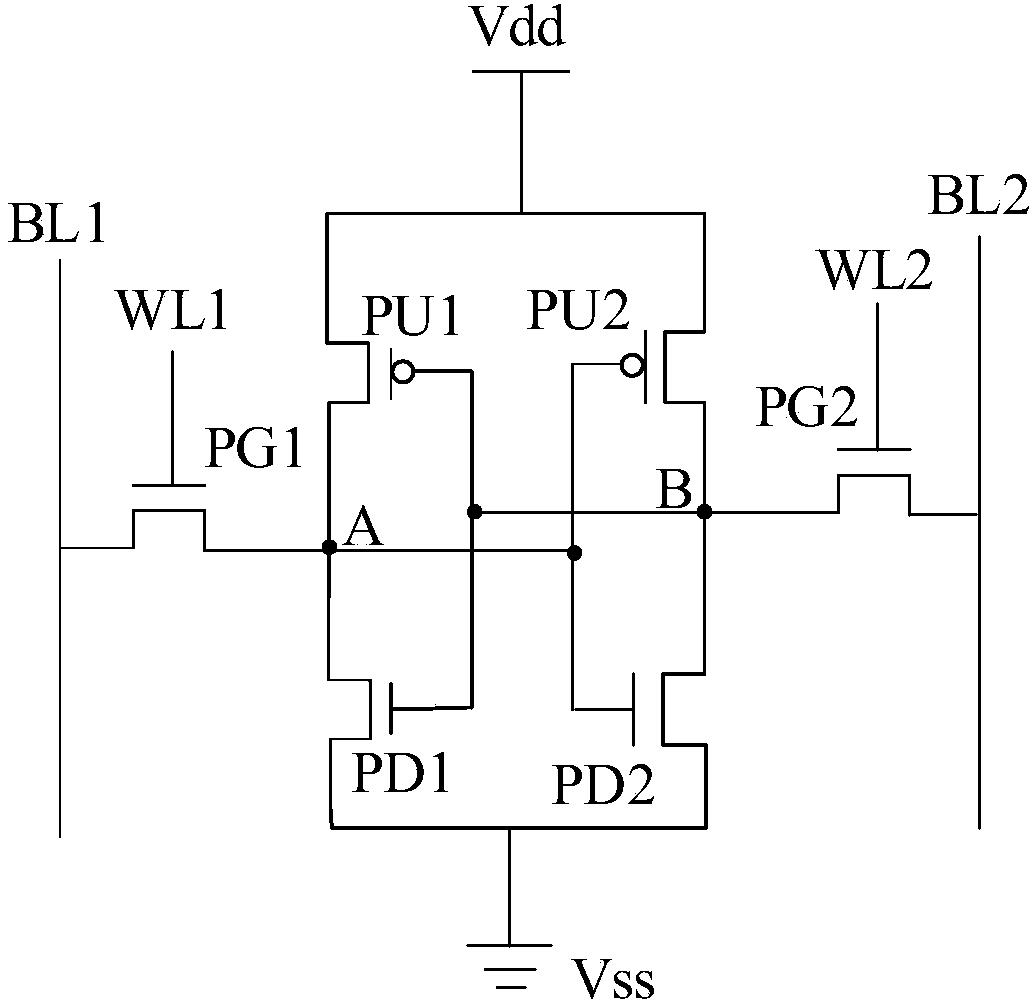

[0039] figure 1 It is a structural diagram of a static memory structure.

[0040] Please refer to figure 1 , the static memory includes: a first pull-up transistor PU1, a first pull-down transistor PD1, a first pass transistor PG1, a second pull-up transistor PU2, a second pull-down transistor PD2 and a second pass transistor PG2. The source of the first pull-up transistor PU2 is connected to the drain of the first pull-down transistor PD1 to form a first storage node A, and the source of the second pull-up transistor PU2 is connected to the drain of the second pull-down transistor PD2 The drains are connected to form a second ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More