Stacked silicon package assembly with stiffener

A reinforcement and component technology, applied in semiconductor/solid-state device parts, electrical components, semiconductor devices, etc., can solve problems such as welding connection failure, impact, damage, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

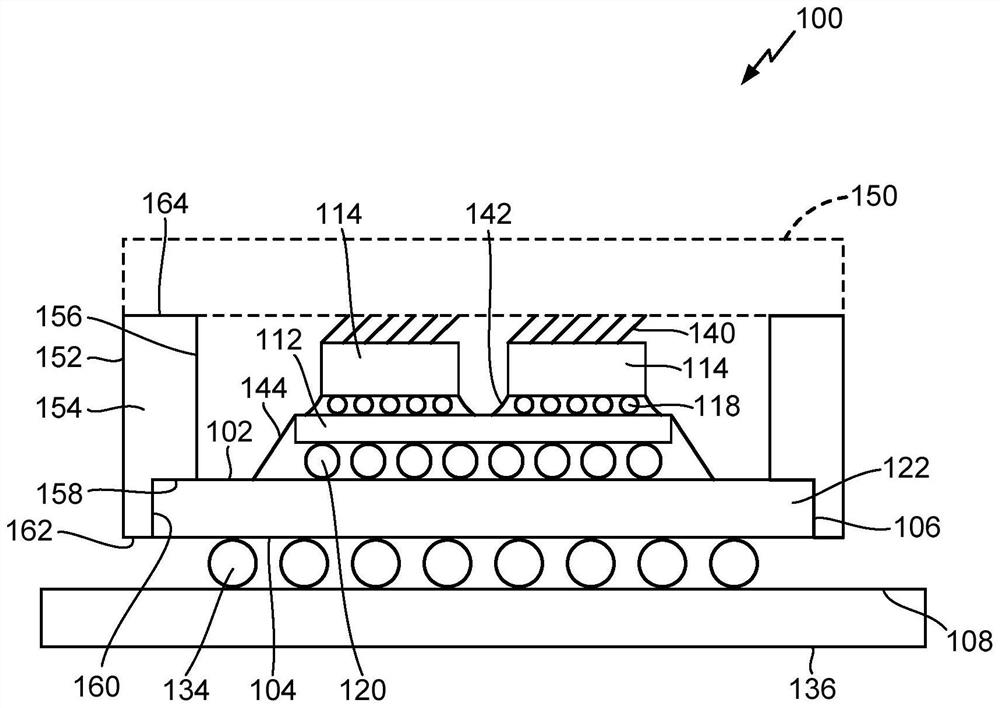

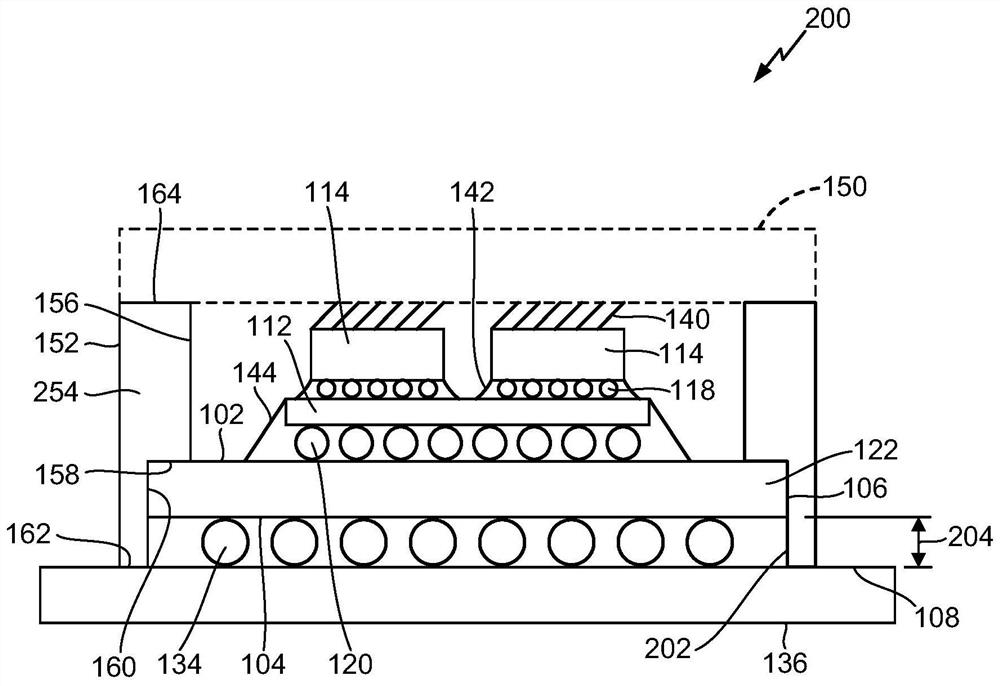

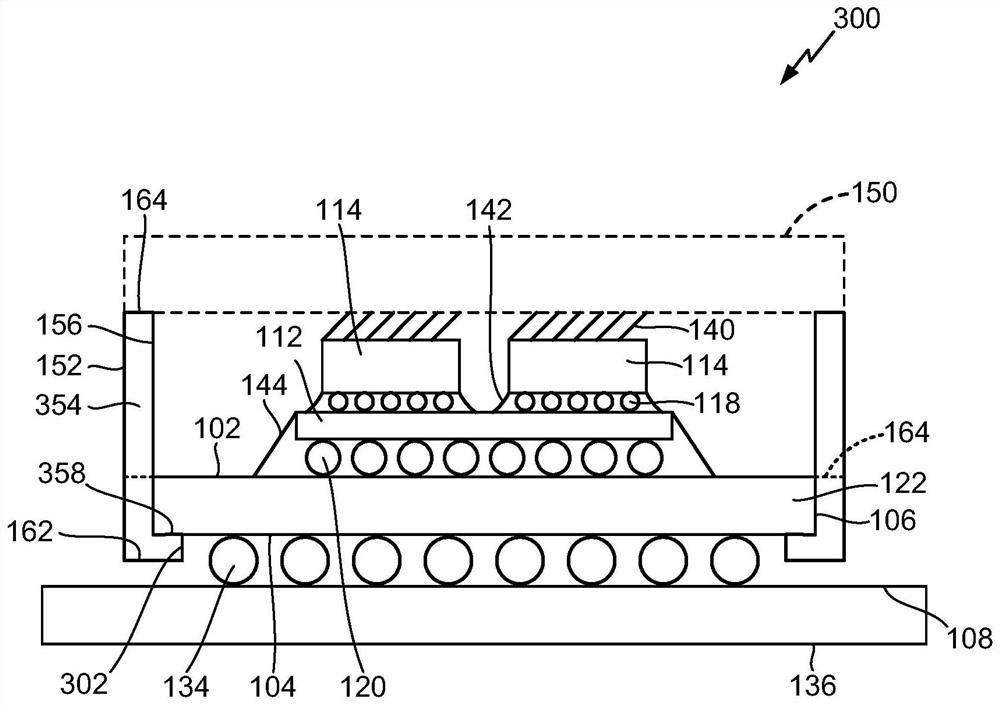

[0035] Chip package assemblies utilizing improved stiffeners and methods of manufacturing the same are provided. A chip package assembly as described herein includes at least one integrated circuit (IC) die and a stiffener disposed on a package substrate. The stiffener is configured to increase the package substrate's resistance to out-of-plane deformation during manufacture and use of the chip package assembly. Advantageously, the increased stiffness of the chip package assembly improves reliability and performance. In various examples described herein, one or more advantages may be realized, including stiffening the package substrate in both the horizontal and vertical axes, a larger adhesive attachment area to reduce delamination, Advantages such as more space for circuit components for chip capacitors, thinner package outlines, and ball grid array (BGA) standoff height control.

[0036] Watch now figure 1 , which schematically shows the integrated chip package assembly...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com