Memory access method and device

A memory access and cache queue technology, applied in the computer field, can solve problems such as different BGs and unbalanced access

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

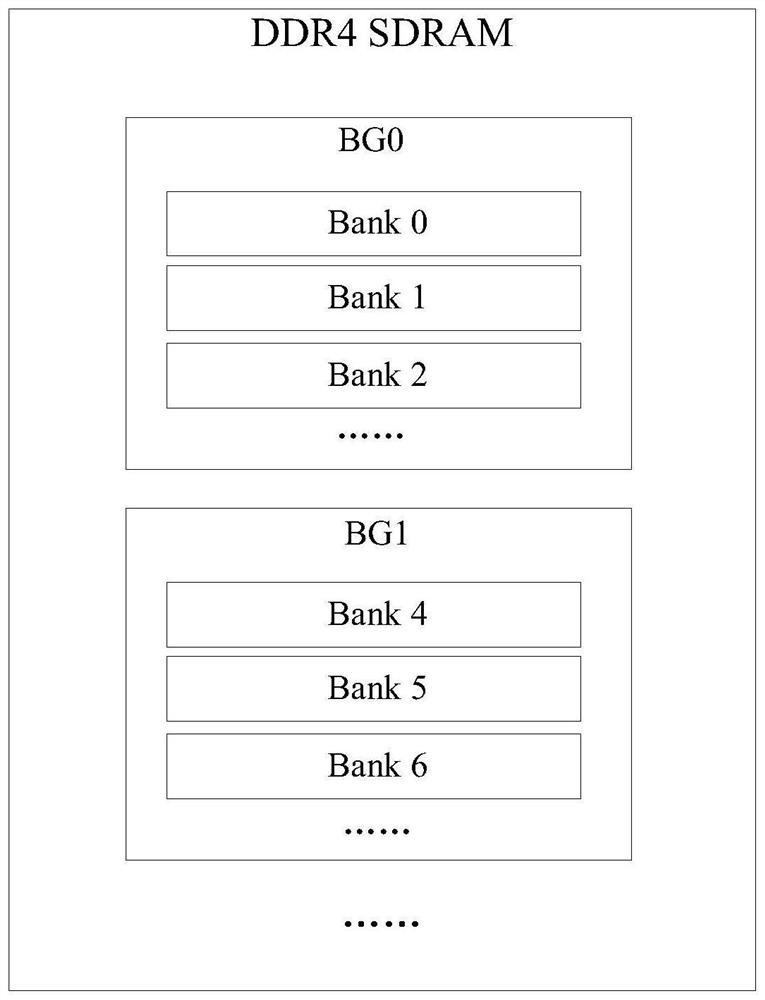

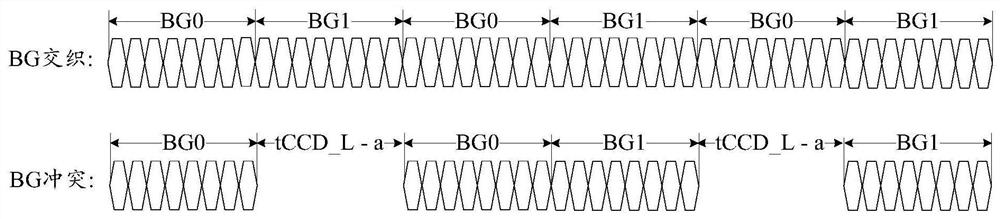

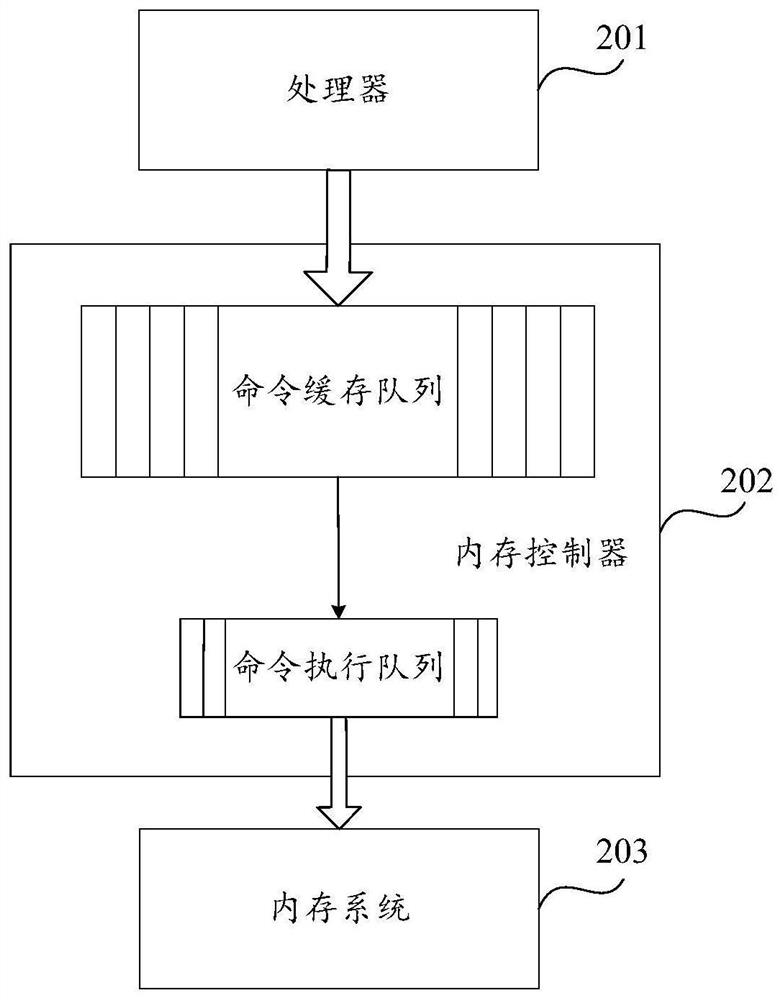

[0052] Figure 2A It is a schematic diagram of an implementation environment involved in a memory access method provided by an embodiment of the present invention. see Figure 2A , the implementation environment may include: a processor 201 , an MC 202 and a memory system 203 . Wherein, the processor 201 may be a CPU, a GPU, or the like. MC202 may include a command buffer queue and a command execution queue. The memory system 203 may include multiple BGs. Among them, the processor 201 can send the command to be executed to the MC202; when the MC202 receives the command sent by the processor 201, it can cache the command in the command cache queue, and then the MC202 can continuously select from the command cache queue The command is added to the command execution queue, and the commands included in the command execution queue are continuously executed to access the BG in the memory system 203 .

[0053] Wherein, when the MC202 executes the commands included in the command...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More