Patents

Literature

110results about How to "Reduce the number of erasures" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

High-performance reliable solid-state disk realizing method

ActiveCN103488583AImprove performanceImprove reliabilityInput/output to record carriersMemory adressing/allocation/relocationRAIDData error

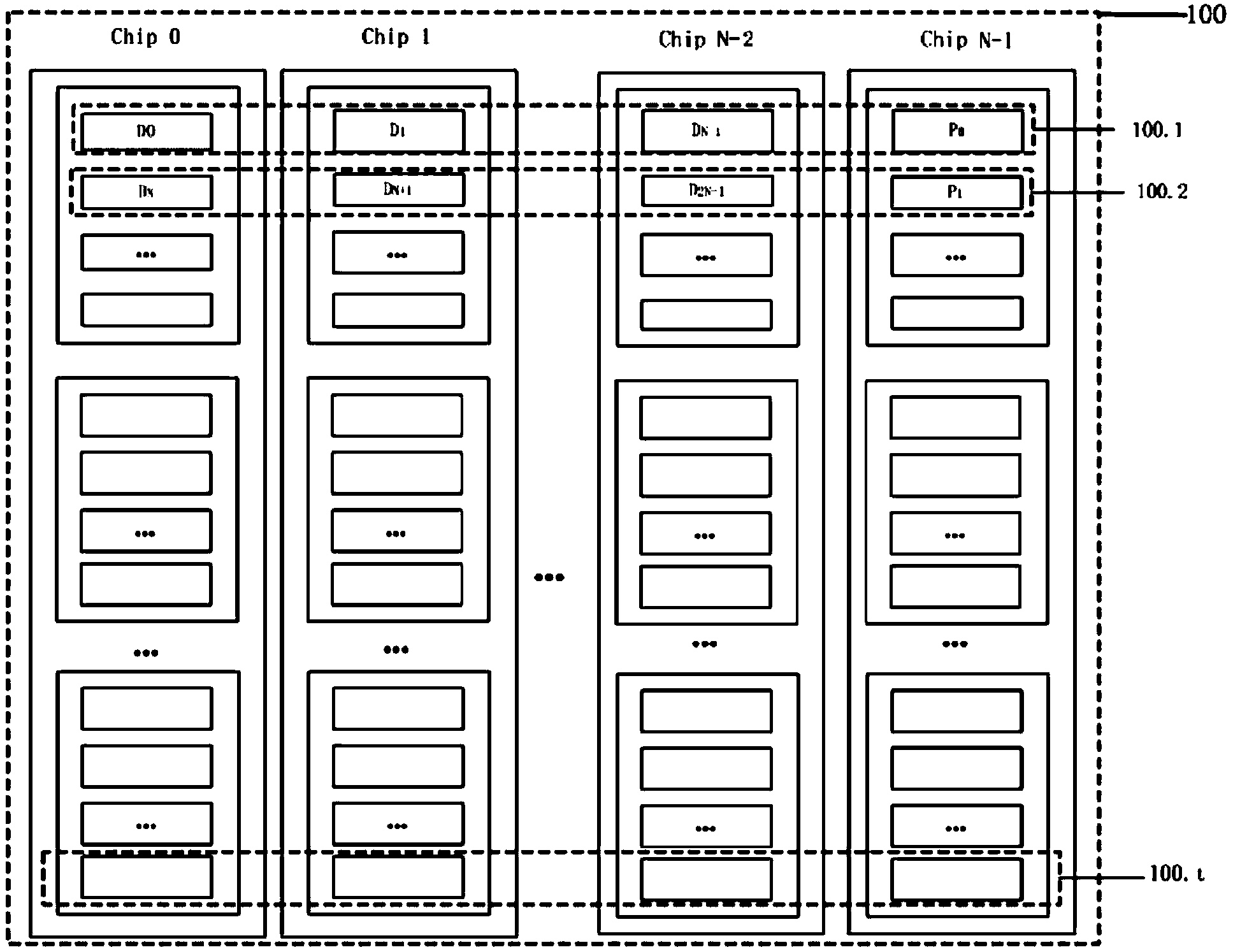

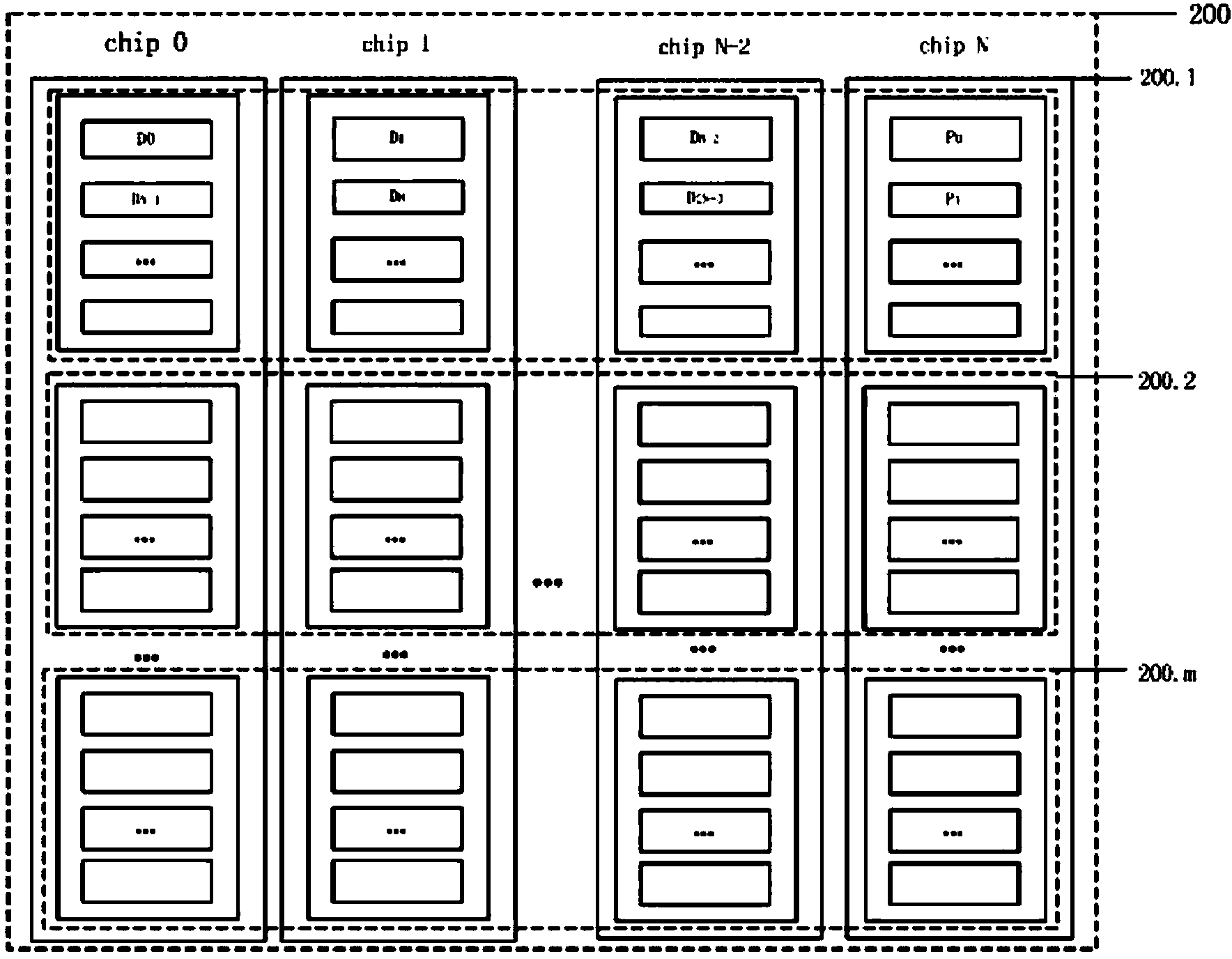

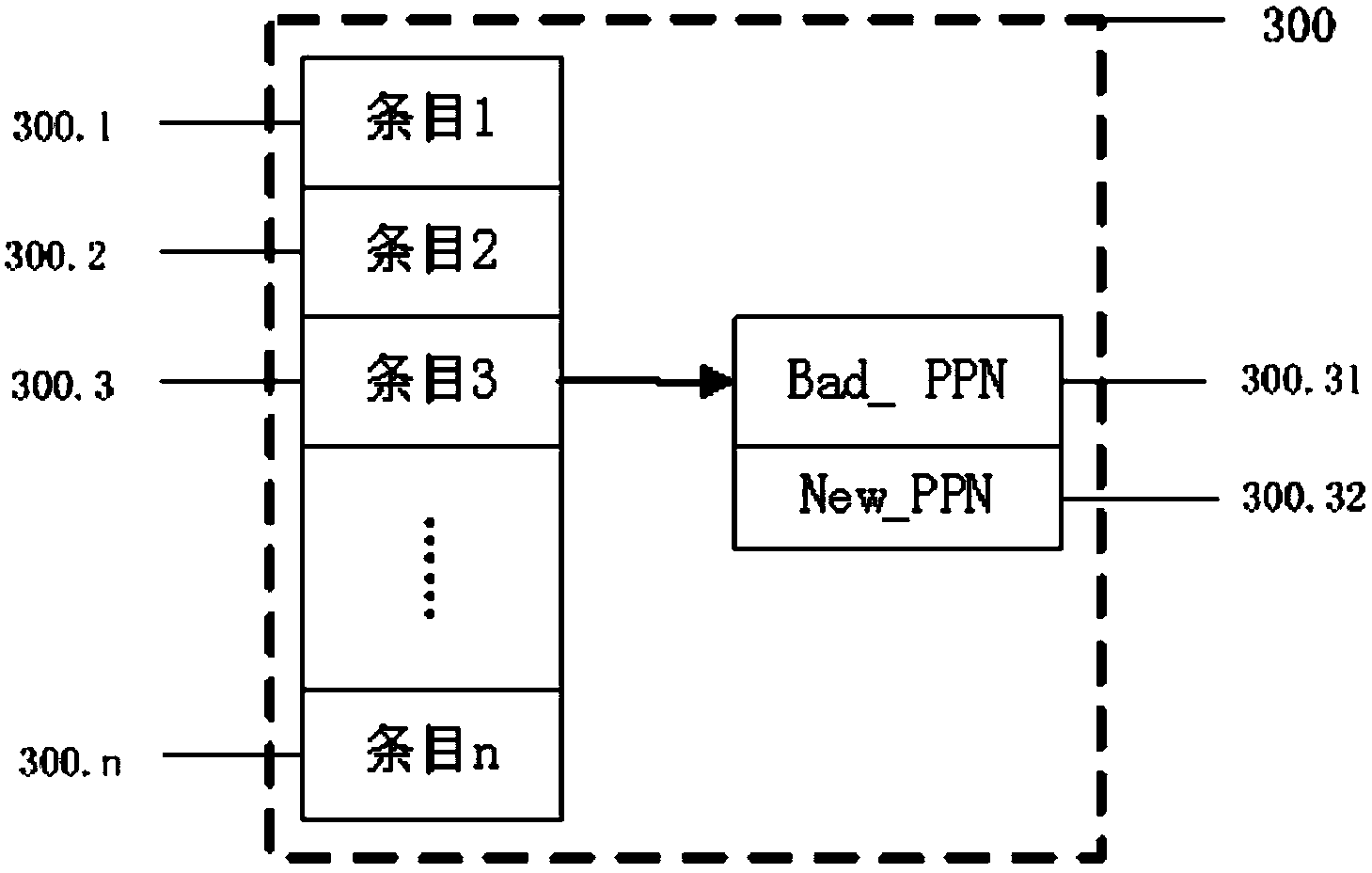

The invention provides a high-performance reliable solid-state disk realizing method. The method includes: (1), dividing all flash memory chips in a solid-state disk into groups and forming an RAID (redundant array of independent disks) 4-level flash array in each group by N successive flash chips; (2), receiving and storing data through a cache; (3), judging whether the cache is filled up or not, if yes, entering the step (4), and if not, returning to the step (2); (4), extracting N-1 data blocks from the cache and computing check values of the N-1 data blocks; making up the N-1 data blocks and the check values into filled stripe data and writing back the flash array; returning to the step (2). The flash chips in the solid-state disk are used for establishing the RAID4-level physical array to assure data reliability. Faults at different levels including page level, block level, or even chip level can be processed. Besides, writing-in performance is improved by writing of filled stripes and sequence, and spatial and performance loss resulted from data errors can be reduced to the utmost.

Owner:HUAZHONG UNIV OF SCI & TECH

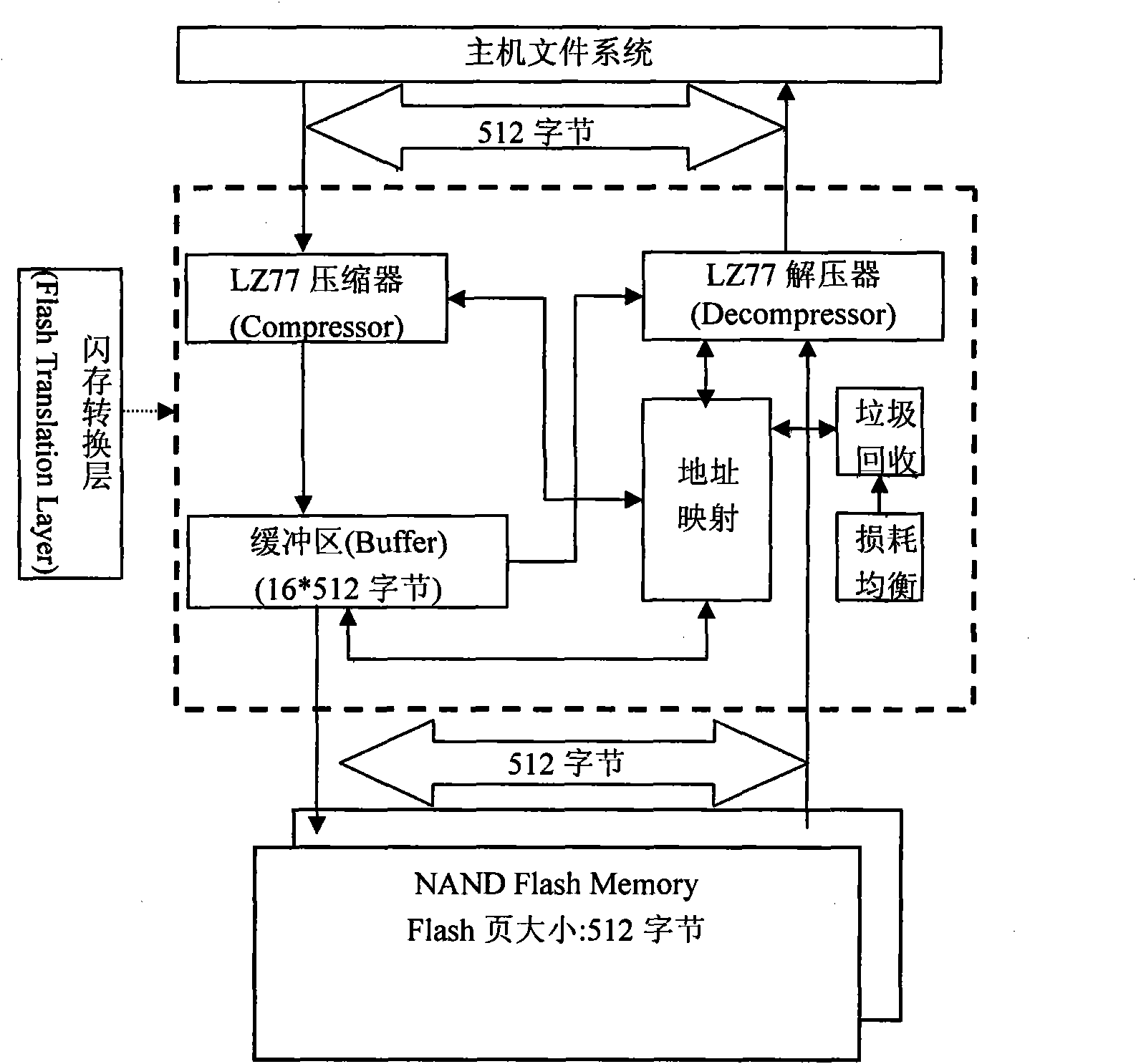

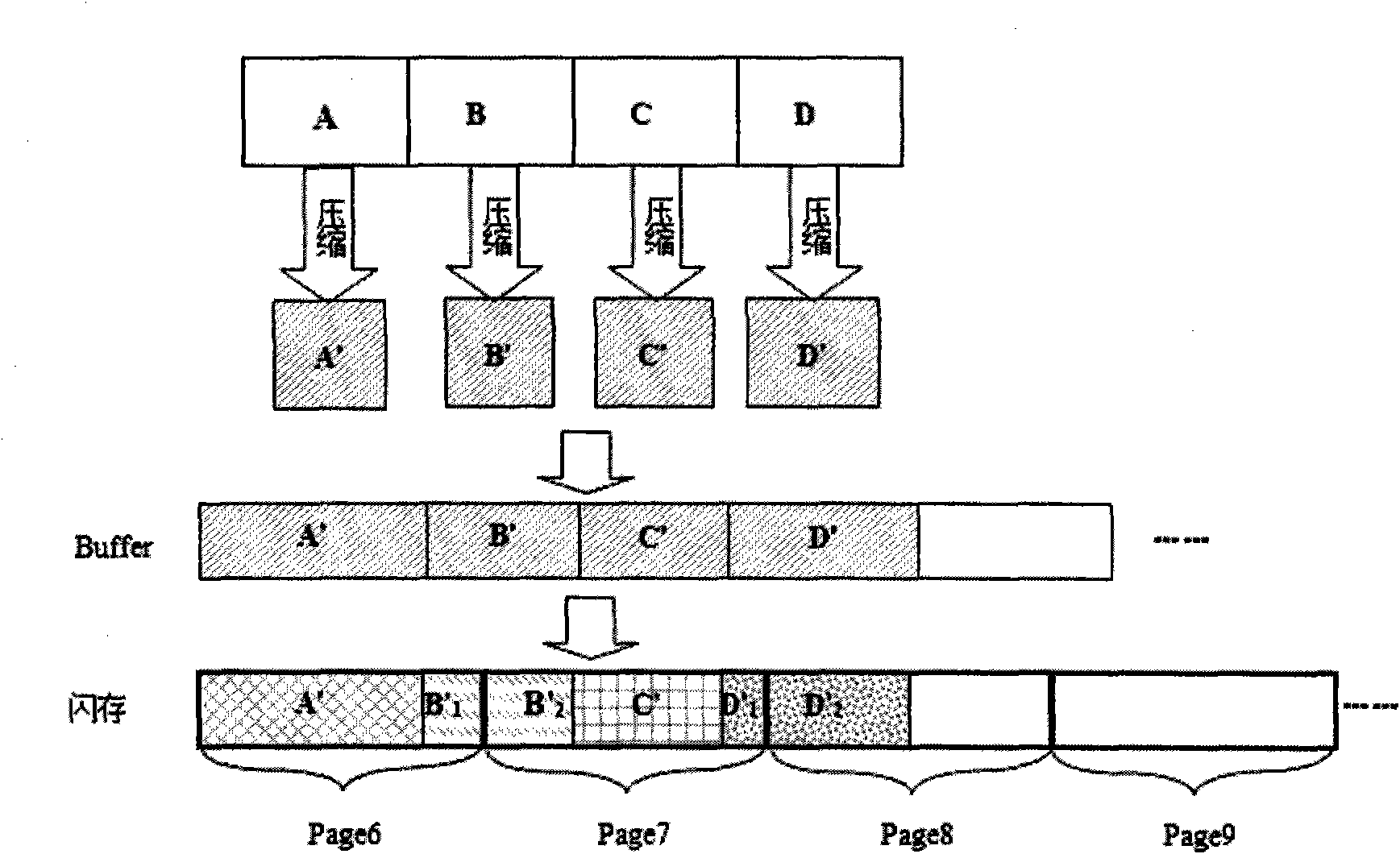

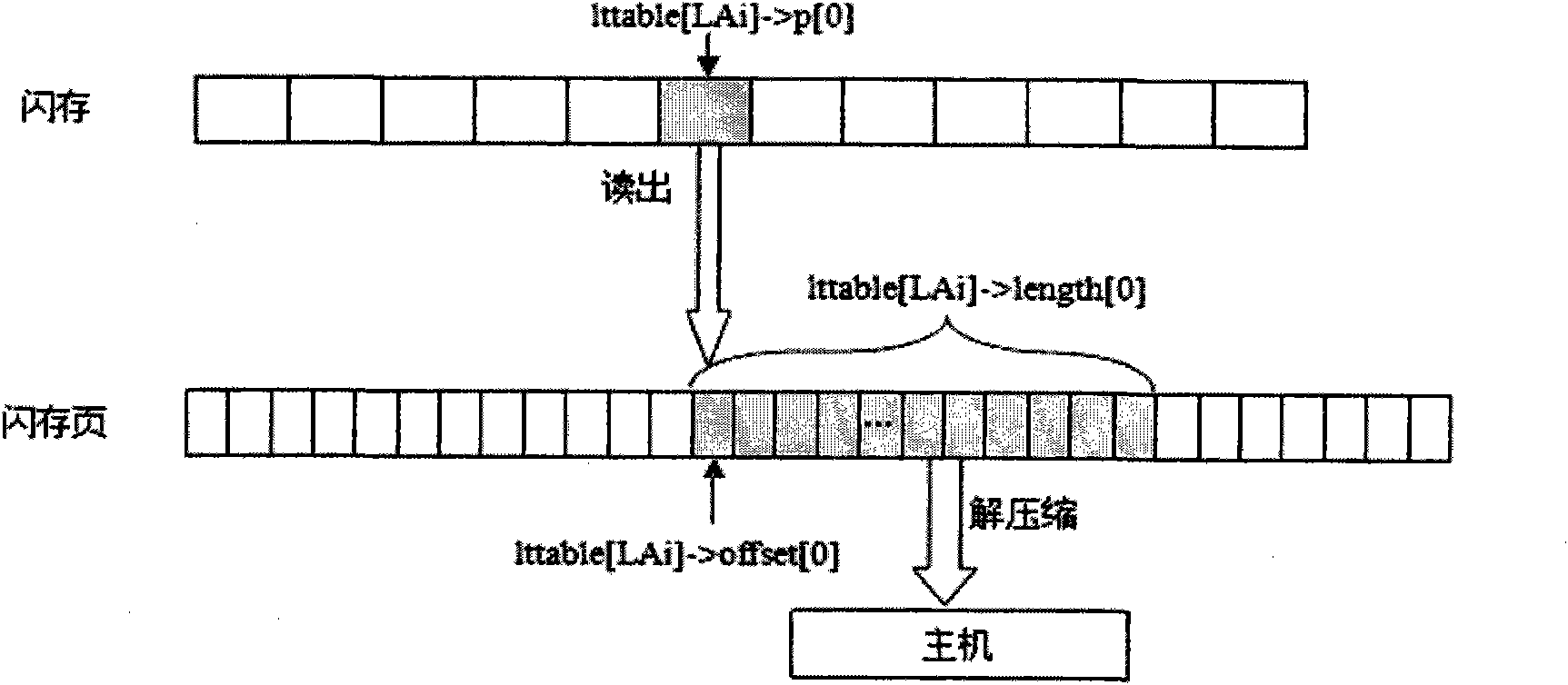

Flash translation layer (FTL) with data compression function and implementation method

InactiveCN101916228AReduce data volumeImprove read and write performanceMemory architecture accessing/allocationMemory adressing/allocation/relocationData compressionLoss balance

The invention discloses a flash translation layer (FTL) with a data compression function and an implementation method. The FTL with the data compression function mainly comprises a compressor, a decompressor, a buffer, an address mapping management module, a trash recycling module and a loss balancing module. An LZ77 (Lempel-Ziv 77) algorithm based single-page compression strategy is adopted for the compression of written-in data and the decompression of readout data. A data compression technology is used for decompressing / compressing the readout / written-in data, a soft buffer is implemented in the FTL, and the data volume written-in and read-out from a flash memory solid state disk each time is reduced, thereby improving the integral reading and writing performance of the flash memory solid state disk.

Owner:NAT UNIV OF DEFENSE TECH

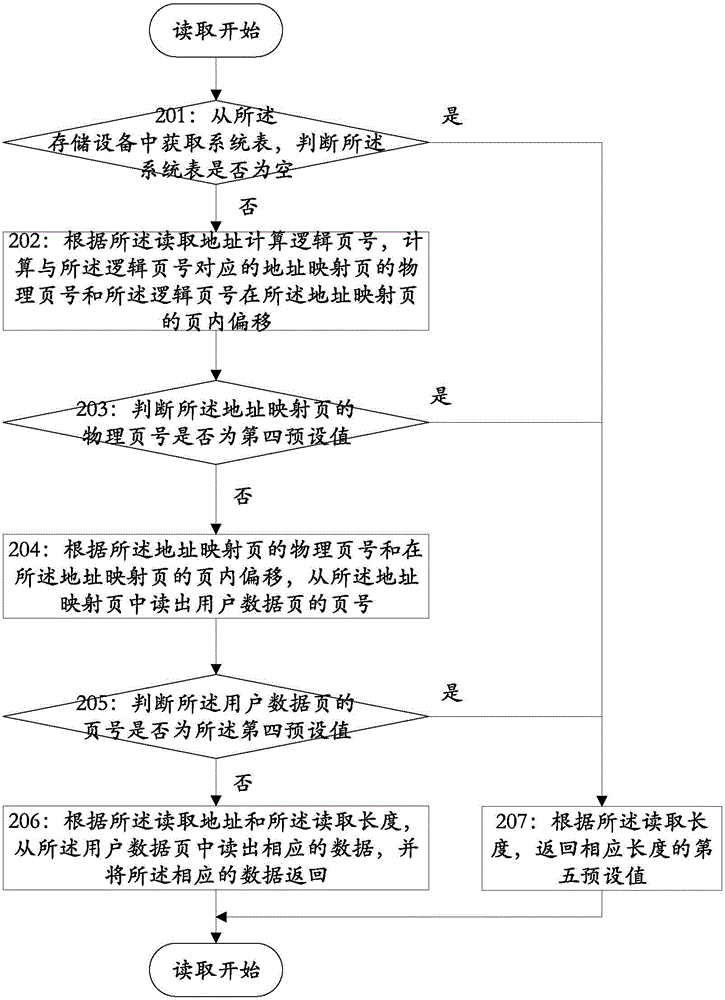

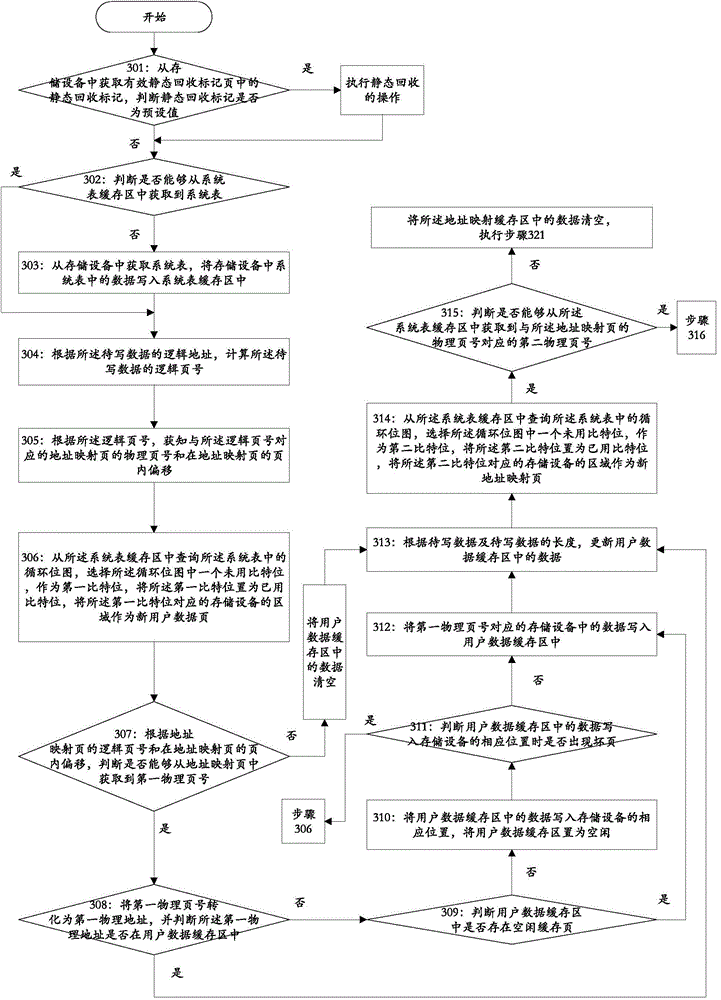

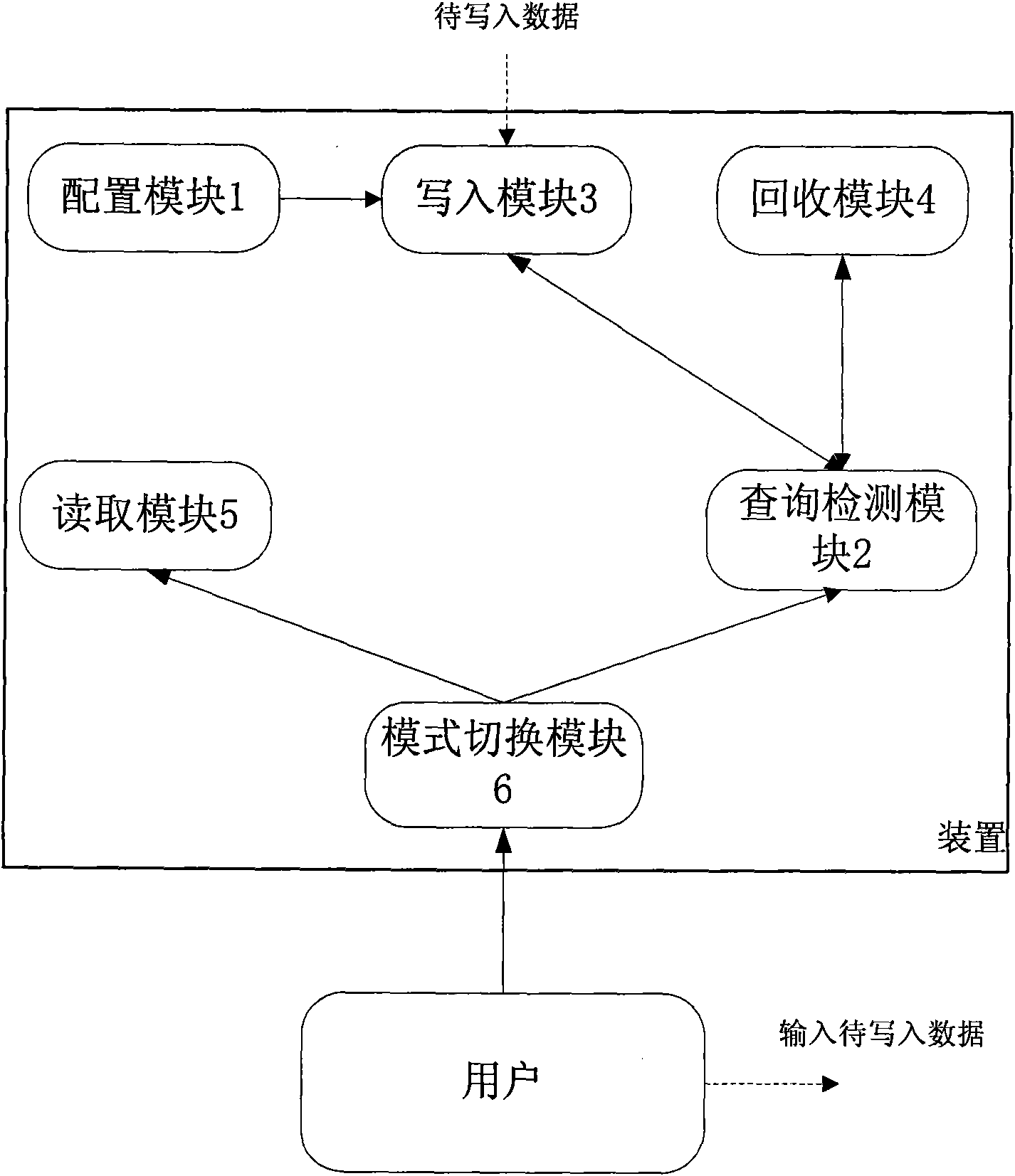

Method and device for conducting data reading and writing on storage device

ActiveCN104090730AReduce the number of erasuresExtended service lifeInput/output to record carriersMemory loss protectionData needsSelection system

Owner:FEITIAN TECHNOLOGIES

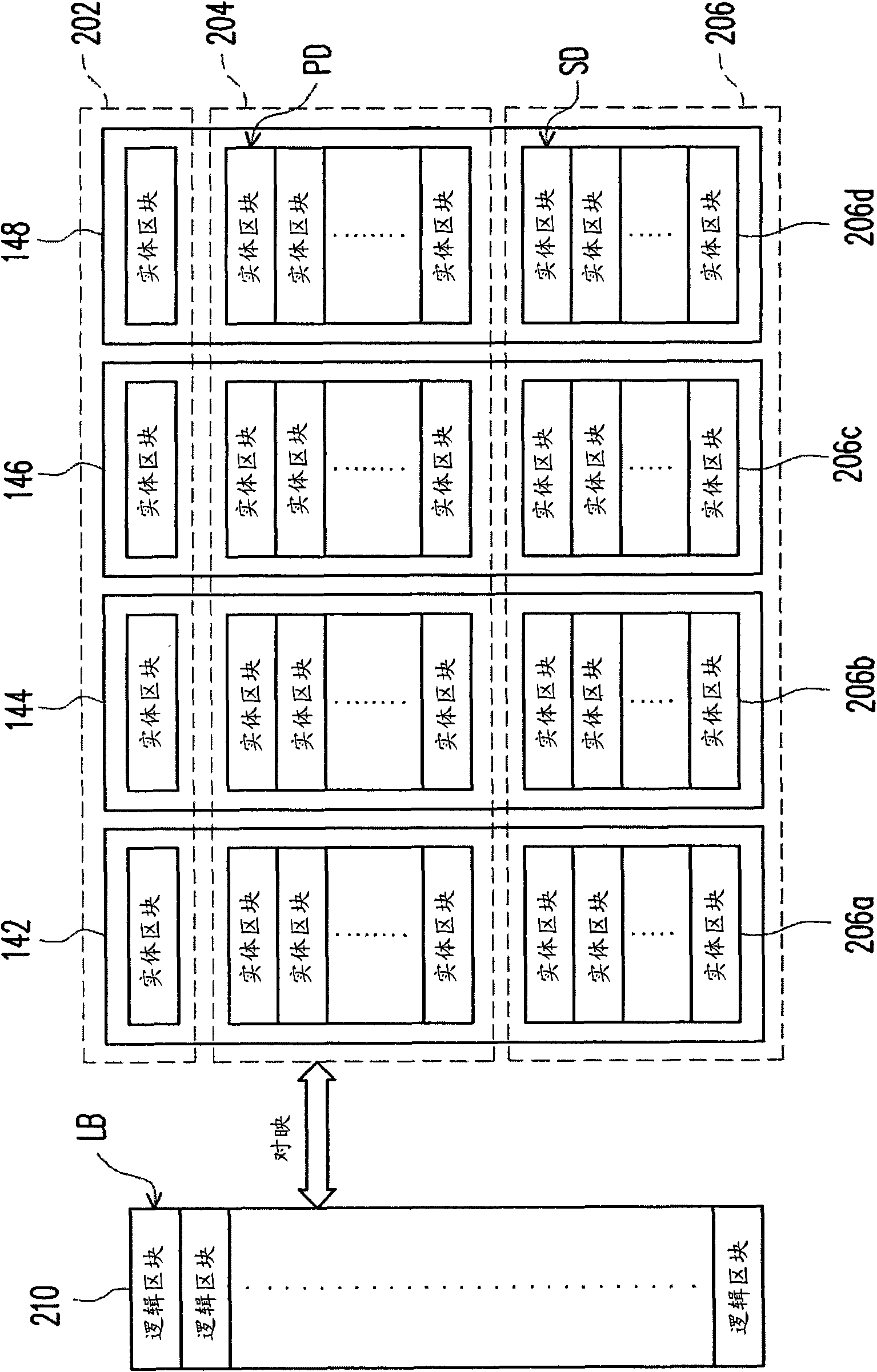

Flash memory data transmission method, flash memory storage system and controller

InactiveCN101667157AReduce the number of erasuresIncrease write speedMemory adressing/allocation/relocationData transmissionLogical address

The invention discloses a flash memory data transmission method, a flash memory storage system and a controller. The data transmission method is applied to data transmission from a cache memory to a plurality of flash memory groups through a single data bus in the flash memory storage system. The data transmission method comprises the step of: taking a logic block as a unit, and orderly arrangingand grouping data which are stored in the cache memory and belongs to continuous logical addresses; and the data transmission method also comprises the step of: transmitting sector data to each flashmemory group respectively through the single data bus according to the grouping in a staggering way, wherein the data belonging to the same logical block are to be transmitted and written into entityblocks of the same flash memory group. On the basis, the data are prevented from being dispersed into a plurality of entity blocks so as to reduce the abrasion of the entity blocks.

Owner:PHISON ELECTRONICS

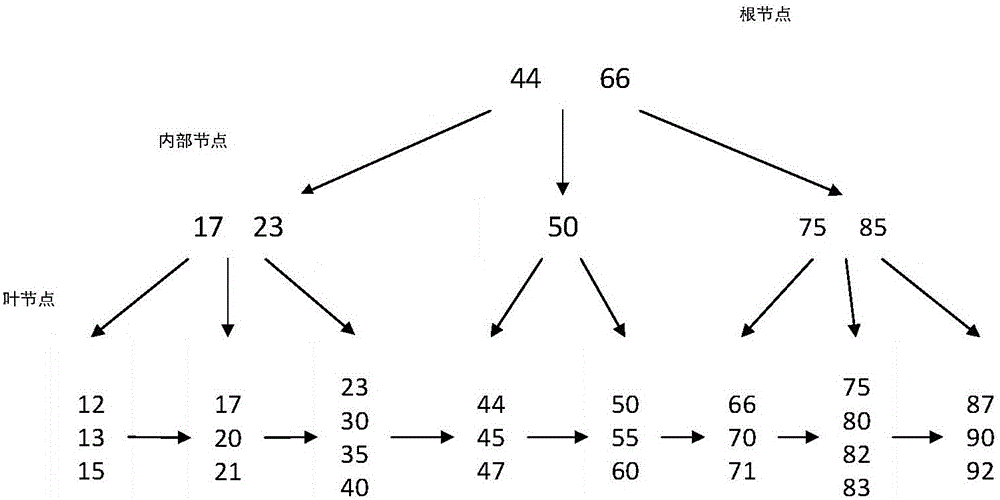

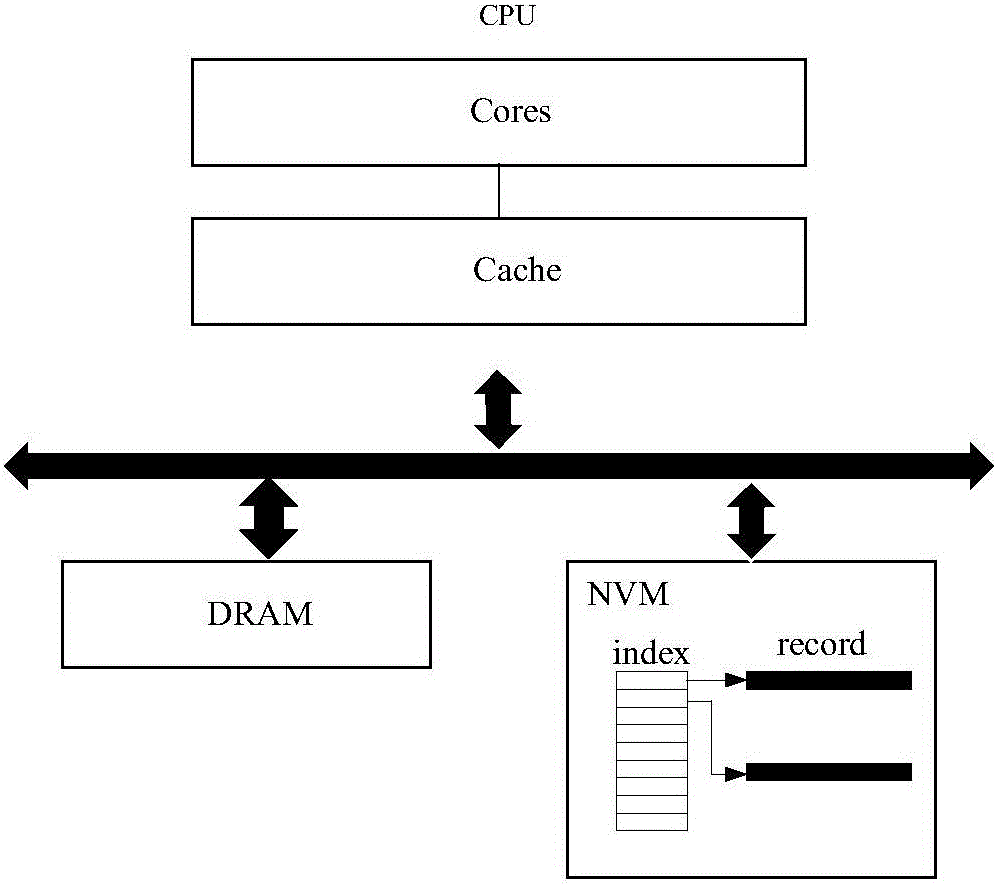

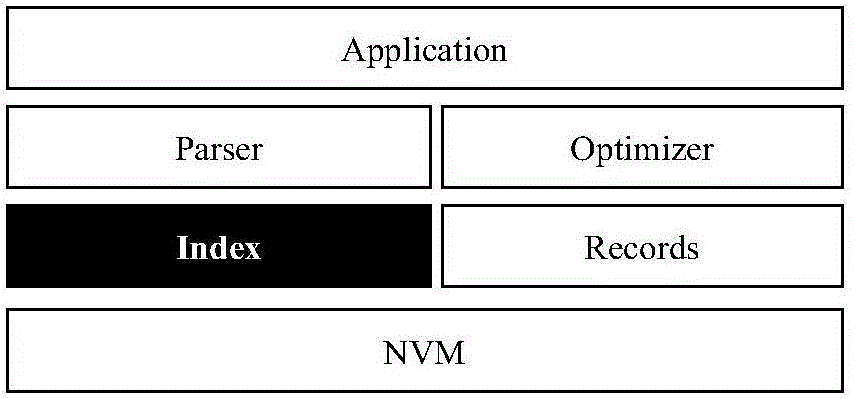

Method for organizing and accessing memory database index with high performance

ActiveCN105975587AReduce the number of erasuresReduce the number of timesSpecial data processing applicationsMemory systemsIn-memory databaseAccess method

The invention discloses a method for organizing and accessing memory database indexes with high performance. The method comprises the following steps of: firstly, organizing an overall index table structure in stages; then, distributing a continuous virtual address space for each stage of bucket chain table in the virtual address space of a system; mapping each bucket chain table to a corresponding virtual address space; finally, organizing indexes and data in each stage of index structure by using a chain table manner, wherein each item in the chain table is a bucket organization, attribute information of the bucket organization, a pointer pointing to a next bucket organization and index entry information are stored in each bucket organization. According to a structure for organizing the database indexes provided by the invention, data are not needed to sort when being inserted or deleted; elements in a VAB (Virtual Address Bucket) are stored disorderly, data can be identified through a bitmap; different from the mode of a tree structure, the elements are not needed to sort when a datum is inserted or deleted once in order to keep the orderliness of inner elements, thus the times of frequently writing a NVM (Non-Volatile Memory) is reduced.

Owner:诸葛晴凤

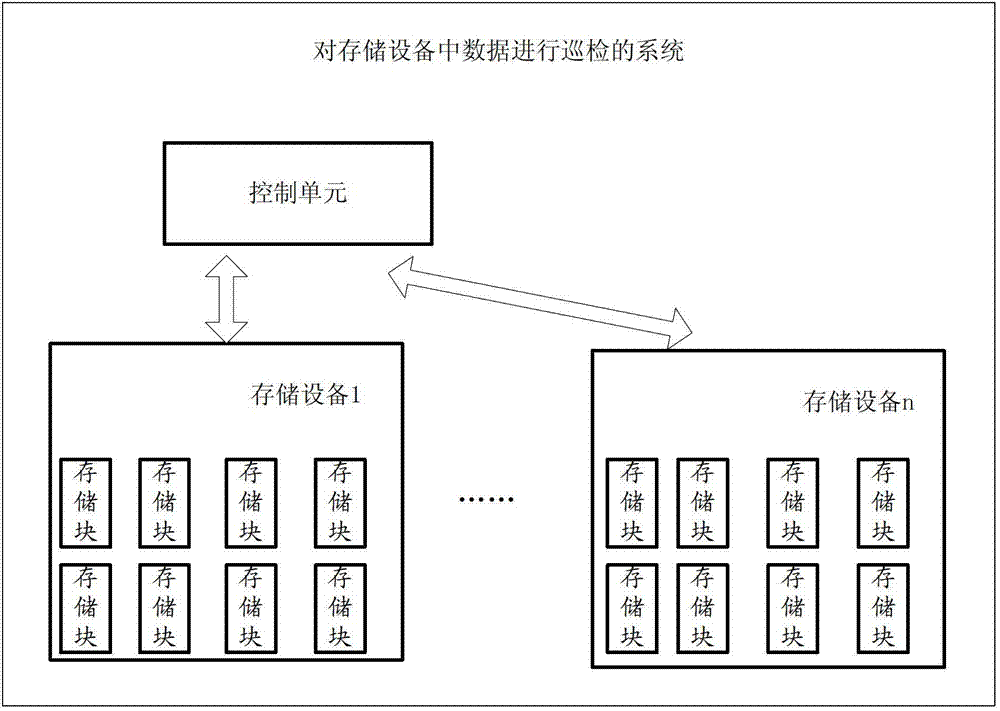

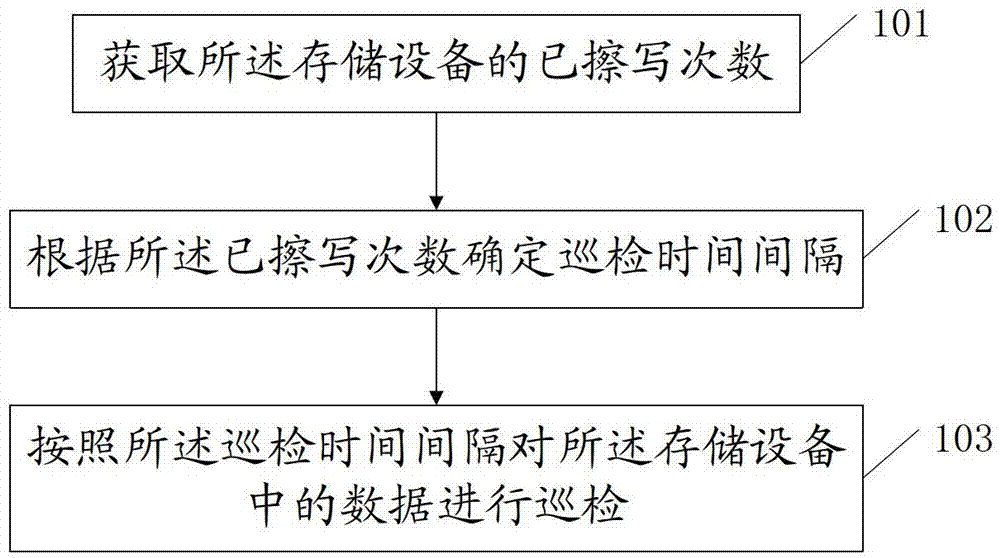

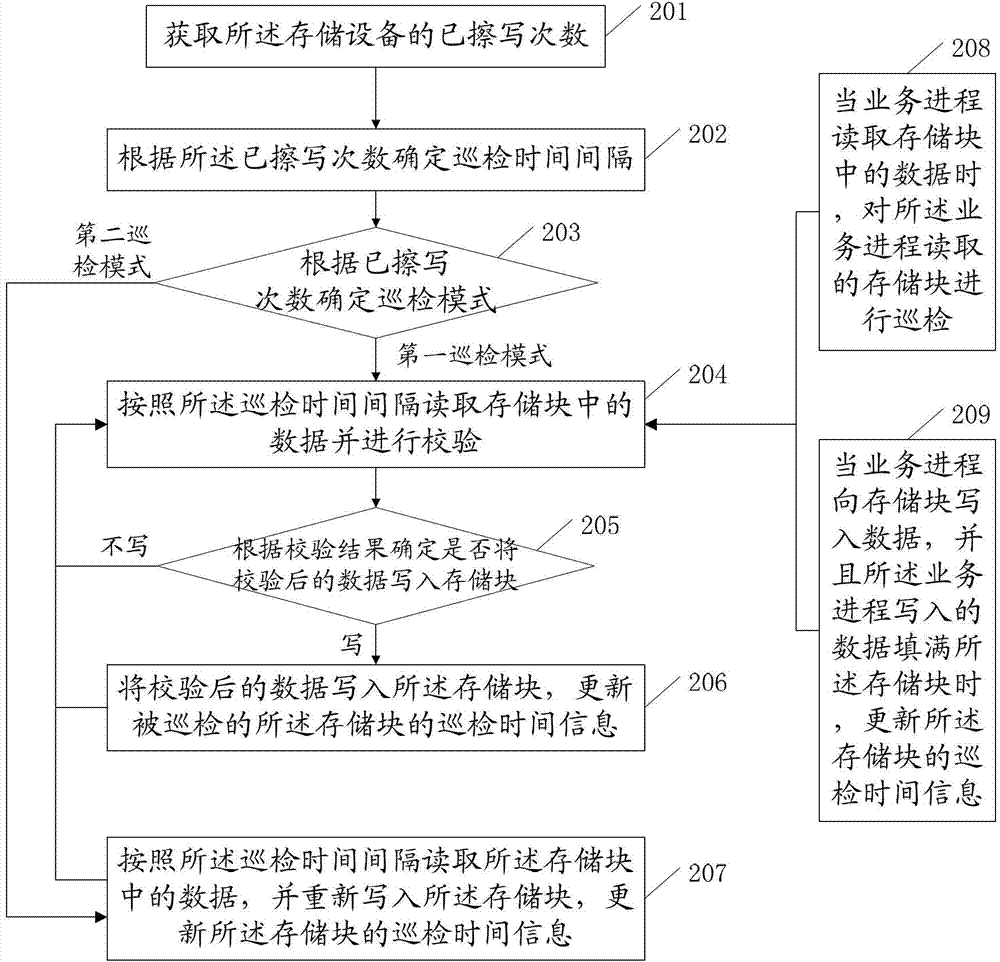

Method, device and system for inspecting data in storage device

ActiveCN103049713AReduce the number of erasuresAvoid lossInternal/peripheral component protectionEmbedded systemElectronic equipment

The invention discloses a method, a device, and a system for inspecting data in a storage device, which relate to the field of electronic equipment and are capable of adjusting inspection period reasonably, so that the performance of the storage device cannot be influenced excessively and the effectiveness of data in the storage device also can be ensured. The method disclosed by the invention mainly comprises the following steps: obtaining the erased time of the storage device; determining the time interval of inspection according to the erased time; and inspecting the data in the storage device according to the time interval of inspection. The embodiment of the invention is mainly used in the process of inspecting data in the storage device.

Owner:HUAWEI TECH CO LTD

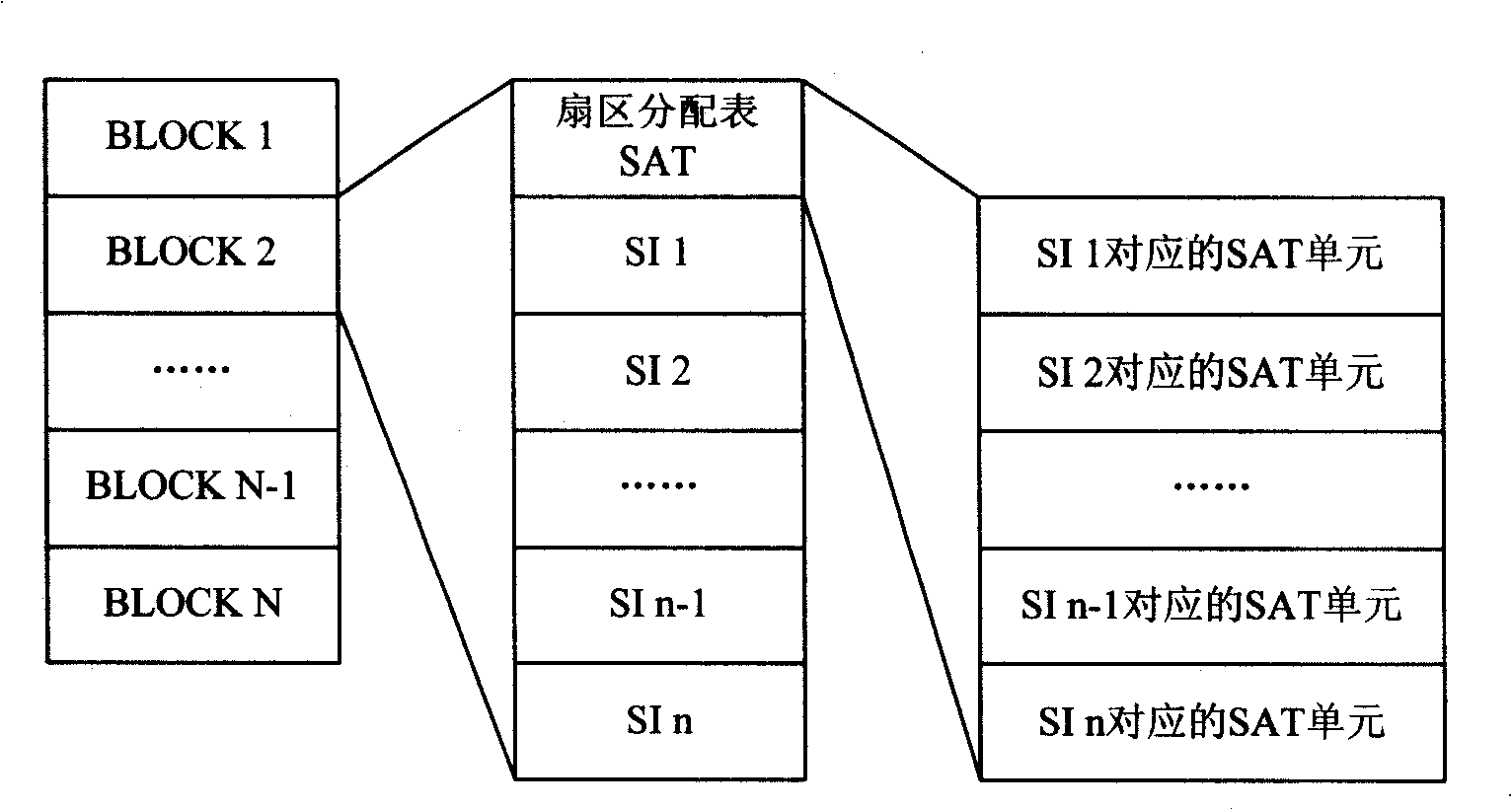

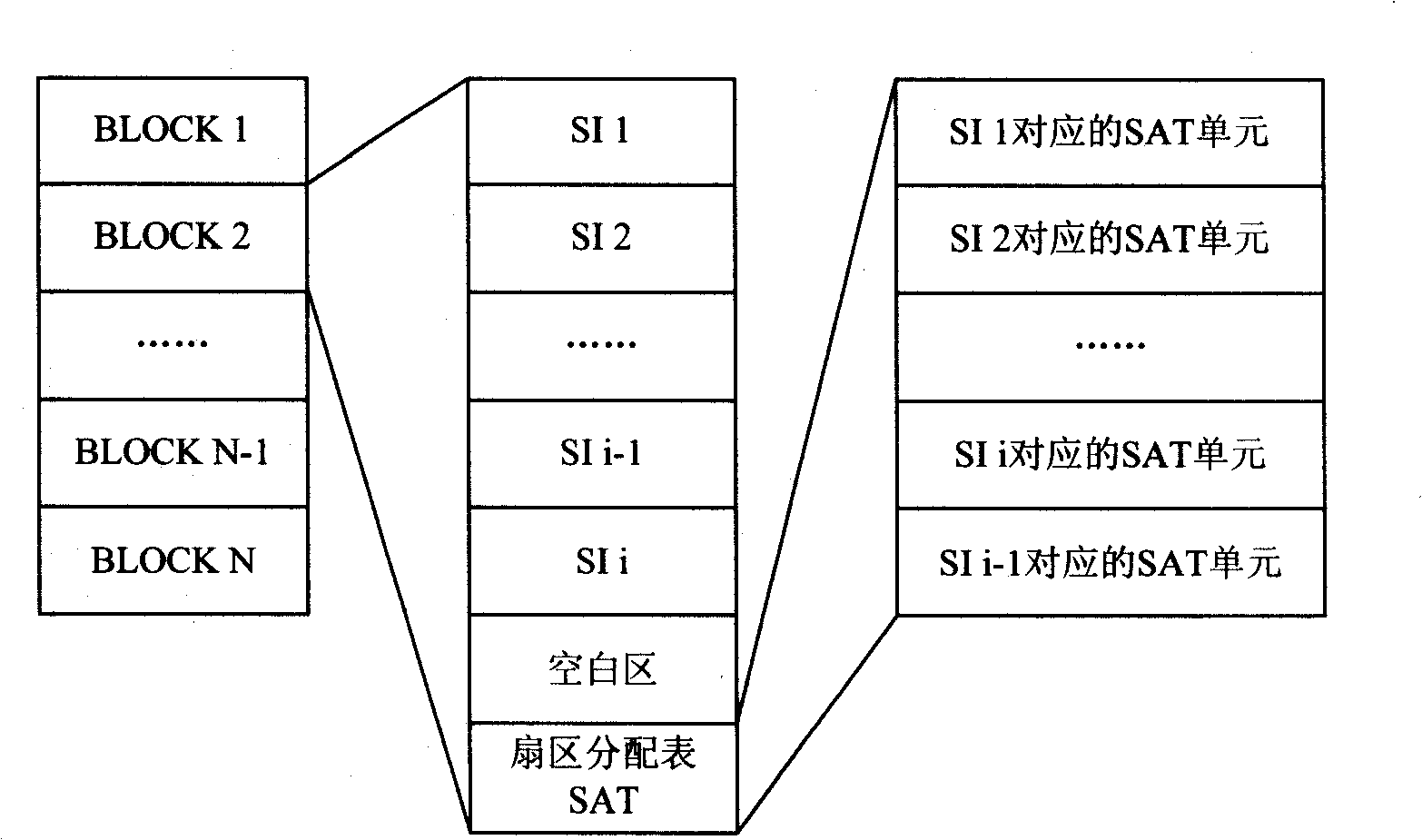

Flash memory storage management method

ActiveCN101324862AImprove Flash read and write speedImprove system performanceMemory adressing/allocation/relocationRedundant data error correctionData recordsOperation time

The invention provides a flash memory management method. By adopting the dynamic virtual sector technology, virtual sectors with different sizes can be assigned to the identical Block according to the application requirements, and are respectively used for storing different types of data records. The flash memory management method comprises the following steps: the flash memory is divided into at least two blocks, each block comprises a data area and a sector allocation table, wherein the data area is divided into at least two virtual sectors, the sector allocation table also comprises the attribute and the ID logical number of each virtual sector. The flash memory management method has the advantages that the Flash read-write speed and the system performance can be effectively improved, the read-write operation times can be greatly reduced, and the service life of the Flash can be prolonged; and compared with the prior solution, the Flash storage space can be fully utilized, and the security of the data can be guaranteed.

Owner:HISENSE VISUAL TECH CO LTD

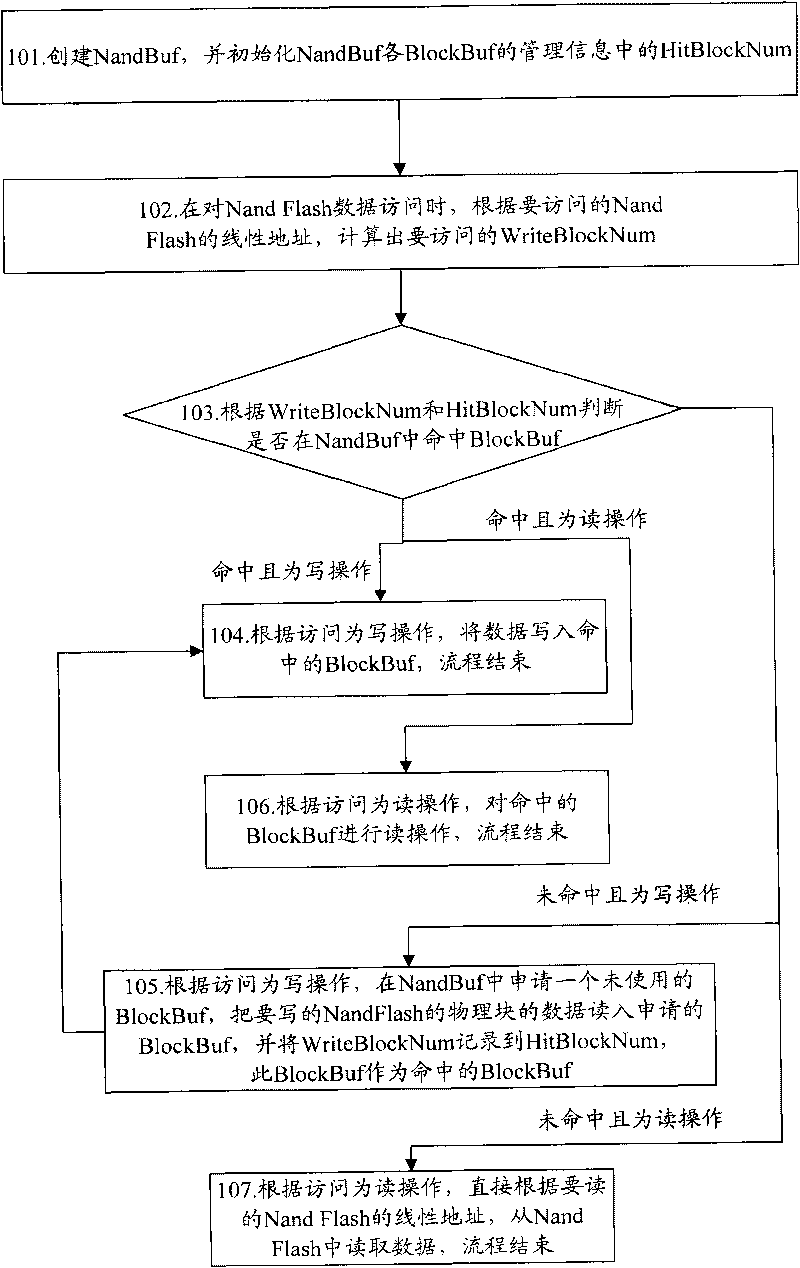

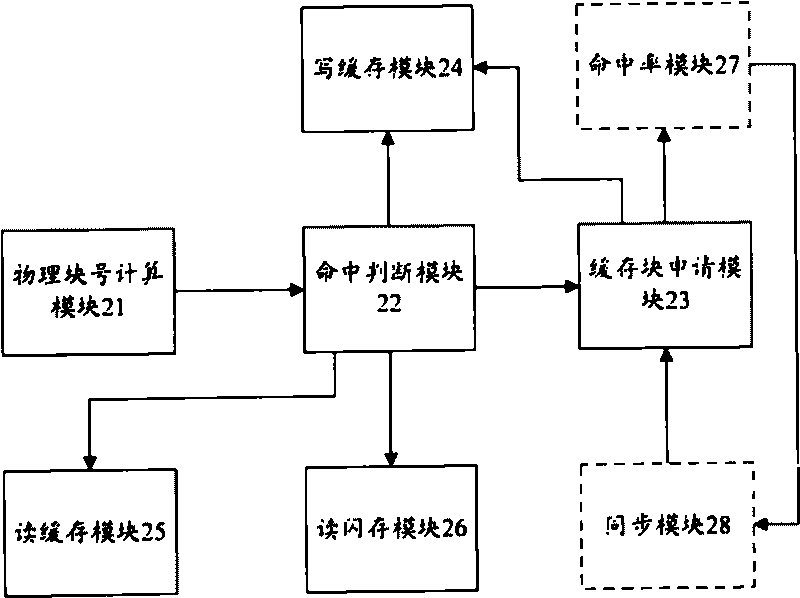

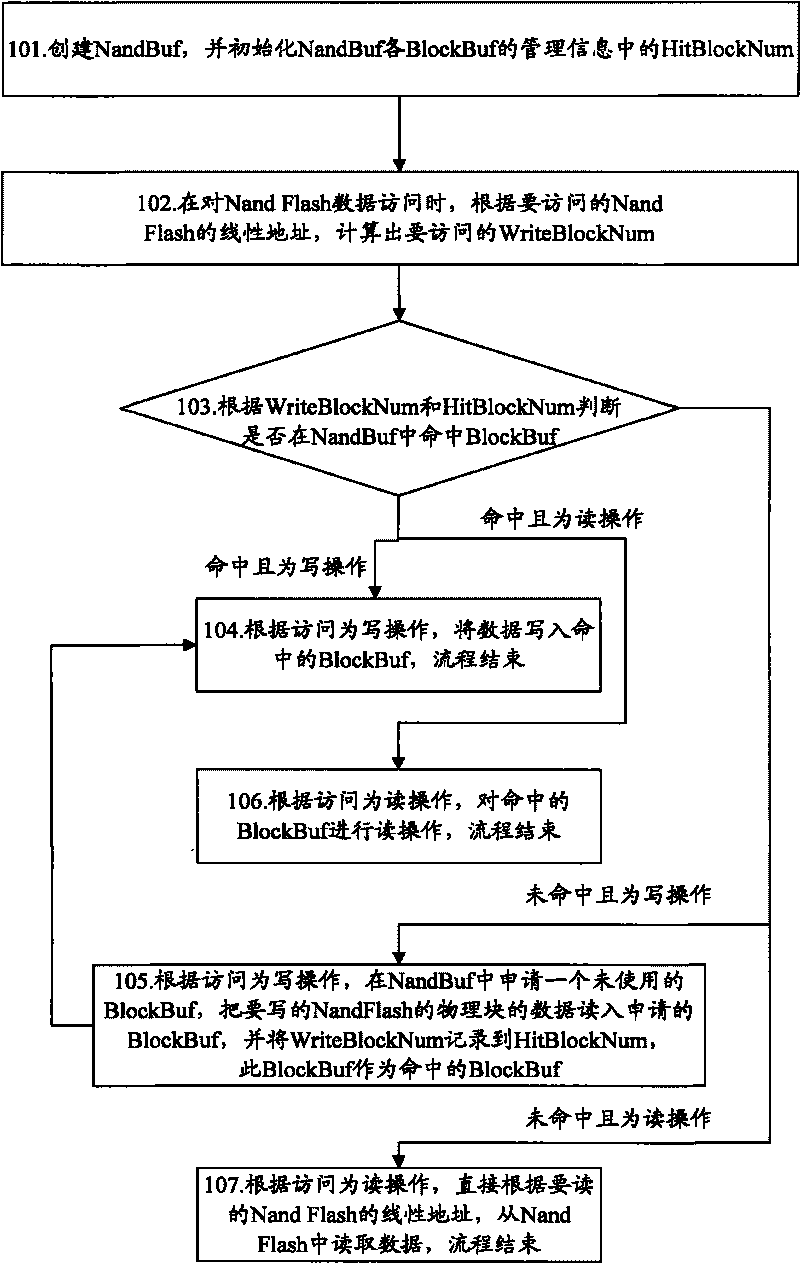

Method and device for accessing data of Nand flash memory

InactiveCN101702139AImprove read and write speedReduce the number of erasuresMemory architecture accessing/allocationMemory adressing/allocation/relocationBlock numberNand flash memory

The invention discloses a method for accessing data of a Nand flash memory, which comprises the following steps: creating a Nand cache; when accessing data of the Nand flash memory, firstly calculating the Write Block Num of the Nand flash memory to be accessed according to the linear address of the Nand flash memory, then judging whether a cache block is hit in the Nand cache or not according to the Write Block Num and the hit block number in management information of all cache blocks, if so, accessing the hit cache block; if not, applying for the cache block and recording the Write Block Num in the hit block number when the access is the write operation, and further carrying out the write operation on the cache block; and directly reading the data from the Nand flash memory when the access is the write operation. The invention simultaneously discloses a device for accessing the data of the Nand flash memory. The adoption of the scheme of the invention can greatly improve the reading speed and the writing speed of the Nand flash memory.

Owner:张翠茹 +4

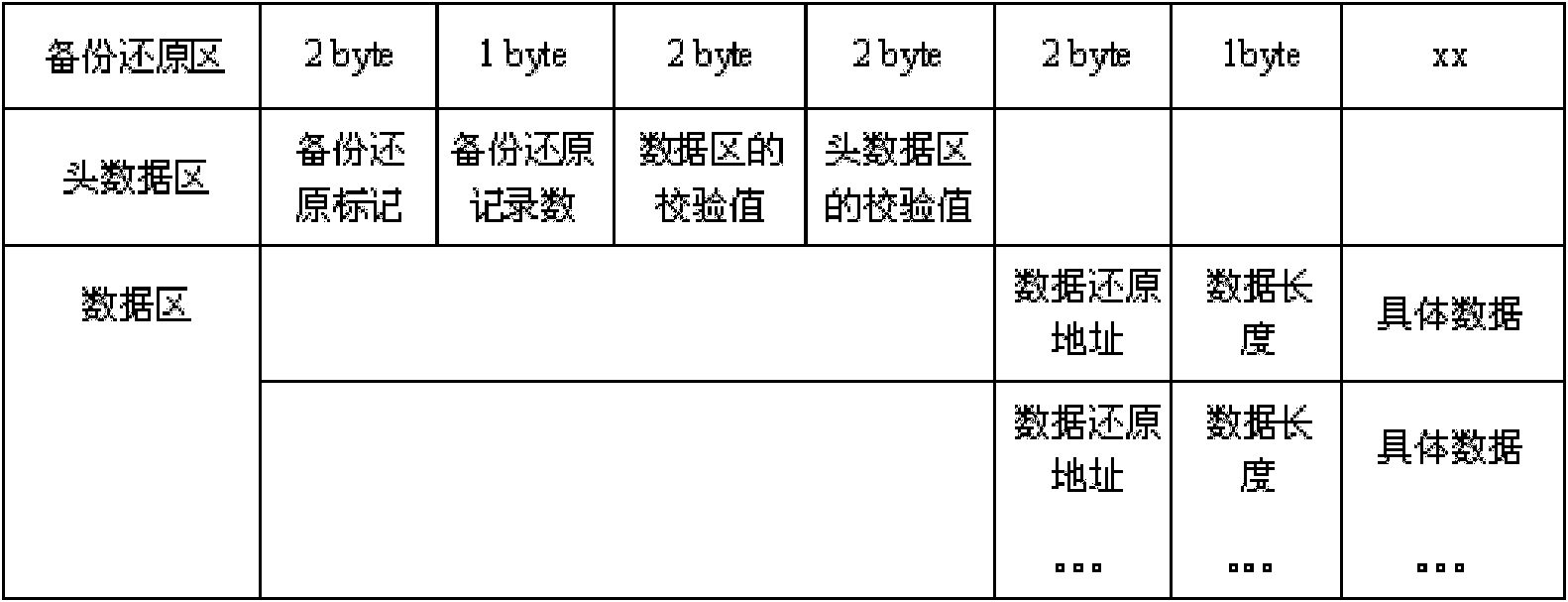

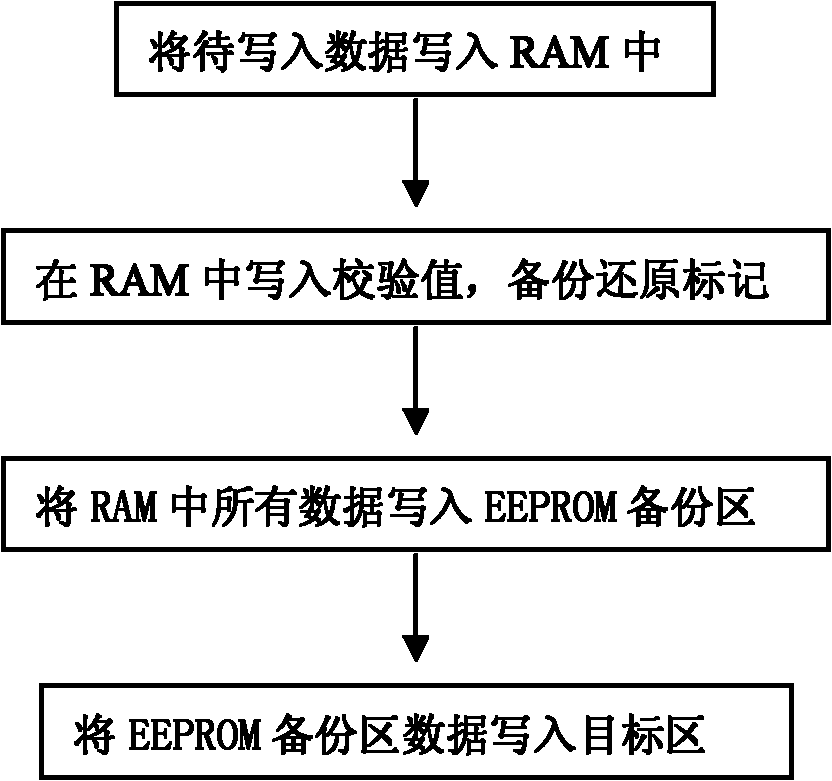

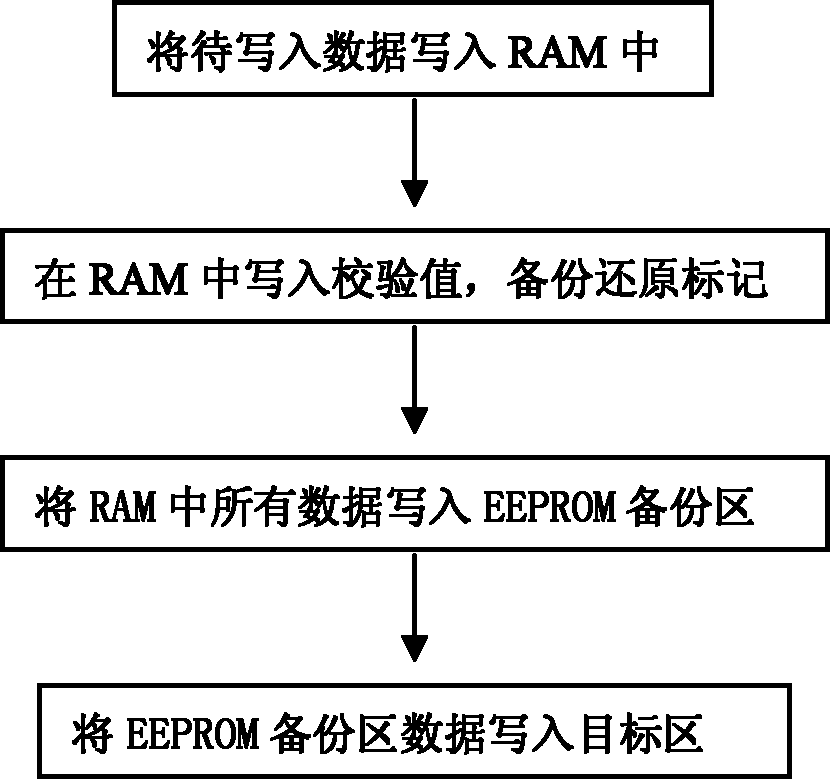

Power failure protection method for intelligent IC (integrated circuit) card data

InactiveCN102609332AEnsure correctnessEnsure integrityRecord carriers used with machinesRedundant operation error correctionElectricityProgrammable read-only memory

The invention discloses a power failure protection method for intelligent IC (integrated circuit) card data. When an IC card is applied, data in the card are frequently modified, and if power fails after the data are erased in the process of modification, data to be written are not normally written while the original data are erased, and important data are lost. When the data in the card are modified, information to be written is firstly backed up to an RAM (random access memory), backup checking information is then computed, a backup and restore mark is set in a restore state, the information is written into the RAM together, all data are organized in the RAM and then written into an EEPROM (electrically erasable programmable read-only memory) backup area, the data are restored, effective data are written into a target data area, and then the backup and restore mark in the backup area is modified into a backup state. Data backup time is shortened by the aid of rapid access features of the RAM, the data are organized in the RAM and then written into the EEPROM backup area once, the frequency of writing the data into an EEPROM is effectively decreased, and the service life of the IC card is prolonged.

Owner:SHANGHAI HUAHONG INTEGRATED CIRCUIT

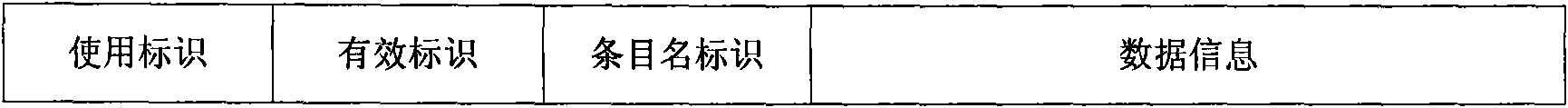

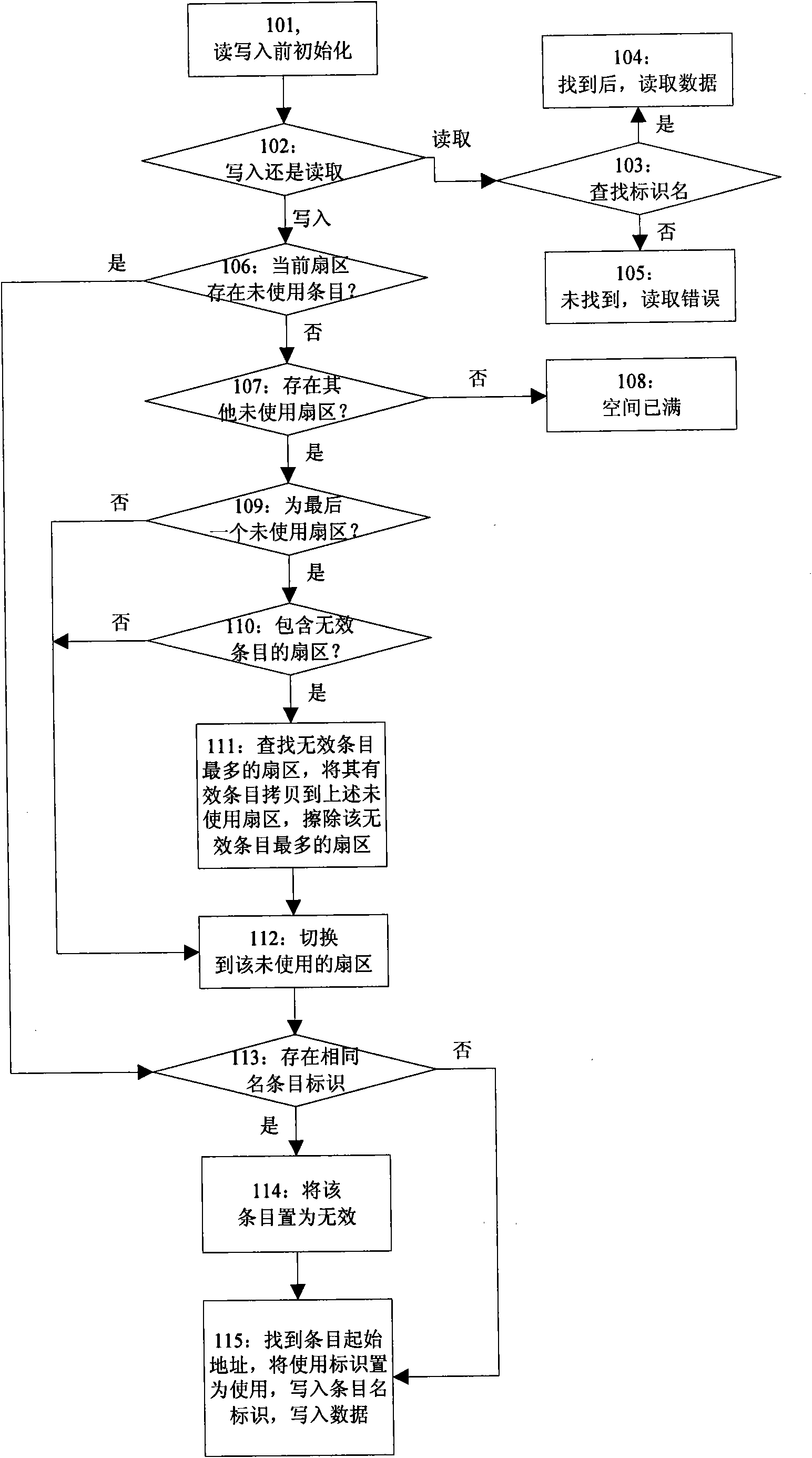

Quick read-write method and device for flash memory

ActiveCN102073592ABalanced accessReduce the number of erasuresMemory adressing/allocation/relocationInvalid DataStorage cell

The invention discloses a quick read-write method and a quick read-write device for a flash memory. The method comprises the following steps of: dividing entries into each sector in the flash memory, and dividing to-be-written data for storage according to the length of the entries, wherein each entry is used for bearing data; when the data are written, querying the unused entries in the current sector, and writing the data into the unused entries; when only one unused sector is queried, if the entries of invalid data are stored in other sectors is detected, reclaiming the space occupied by the entries; otherwise, directly writing the data into the unused data. The data are organized and stored according to a form of entries of fixed formats. When the data are modified, the original entries are not modified, but the original entries are set to be invalid, and new entries are written, so the erasing frequency is reduced, the average writing speed is quickened, and balanced access of different storage units of the FLASH is ensured.

Owner:ZTE INTELLIGENT IOT TECH

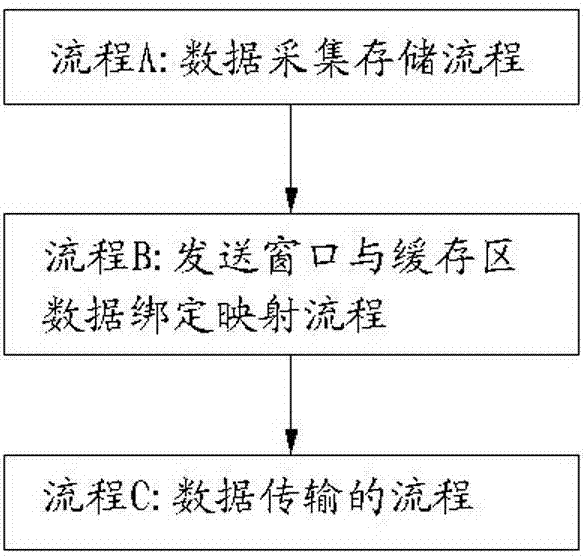

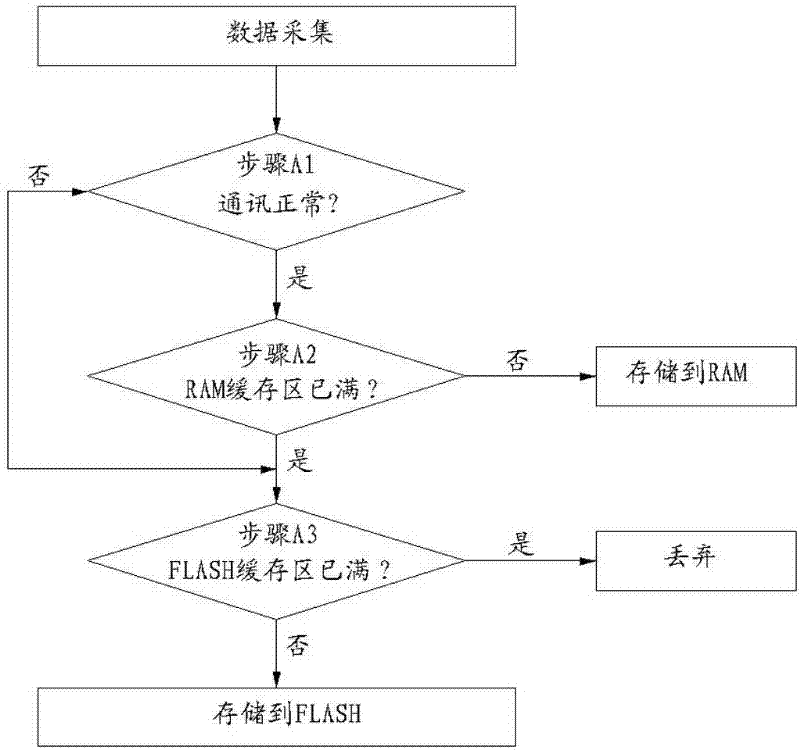

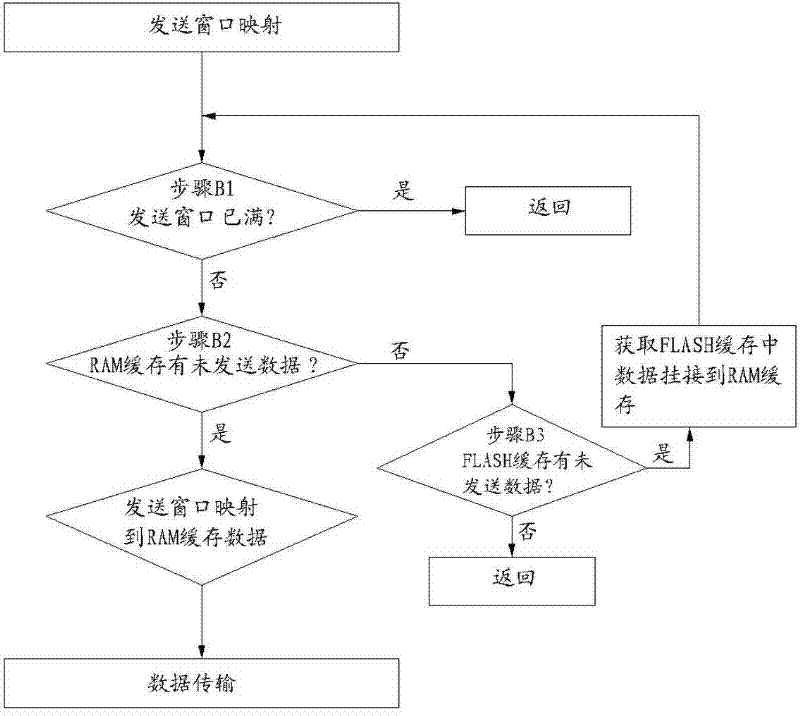

Method for data acquisition, storage and transmission

ActiveCN102521174AReduce the number of erasuresEasy to implementMemory adressing/allocation/relocationData transmissionEngineering

The invention relates to the field of data acquisition, storage and transmission, particularly relates to a method for data acquisition, storage and transmission in an embedded system. The invention provides a method for data acquisition, storage and transmission, which comprises the following flows of: flow A, a data acquisition and storage flow; flow B, data binding and mapping between a transmitting window and a cache region; flow C: a data transmission flow. The method for data acquisition, storage and transmission is simple to realize, steady and reliable, has high efficiency, quick transmission speed and high transmission efficiency, cannot influence the real-time property of the system, and can prolong the service life of products and reduce communication traffic, thereby reducing communication traffic cost.

Owner:XIAMEN YAXON NETWORKS CO LTD

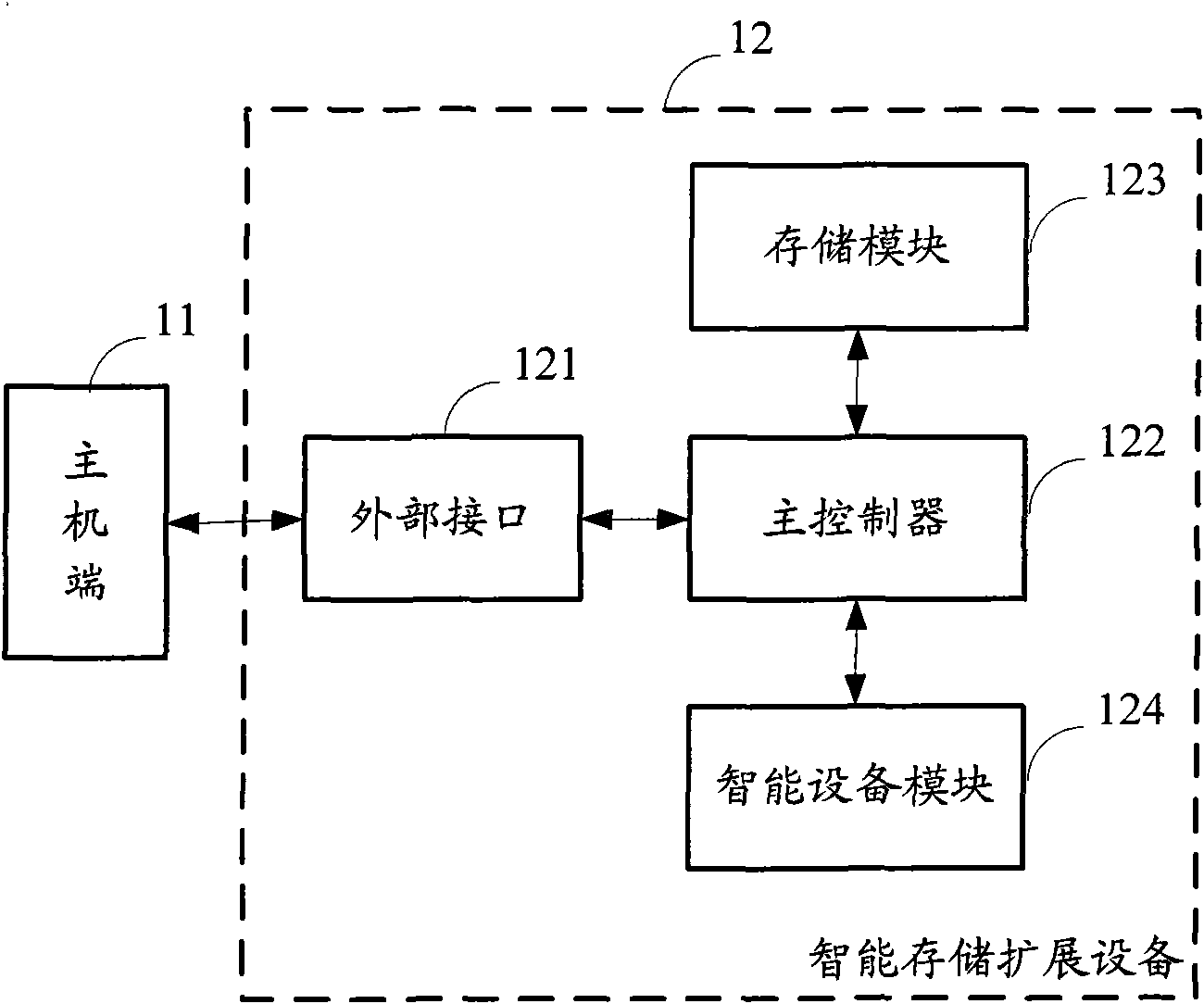

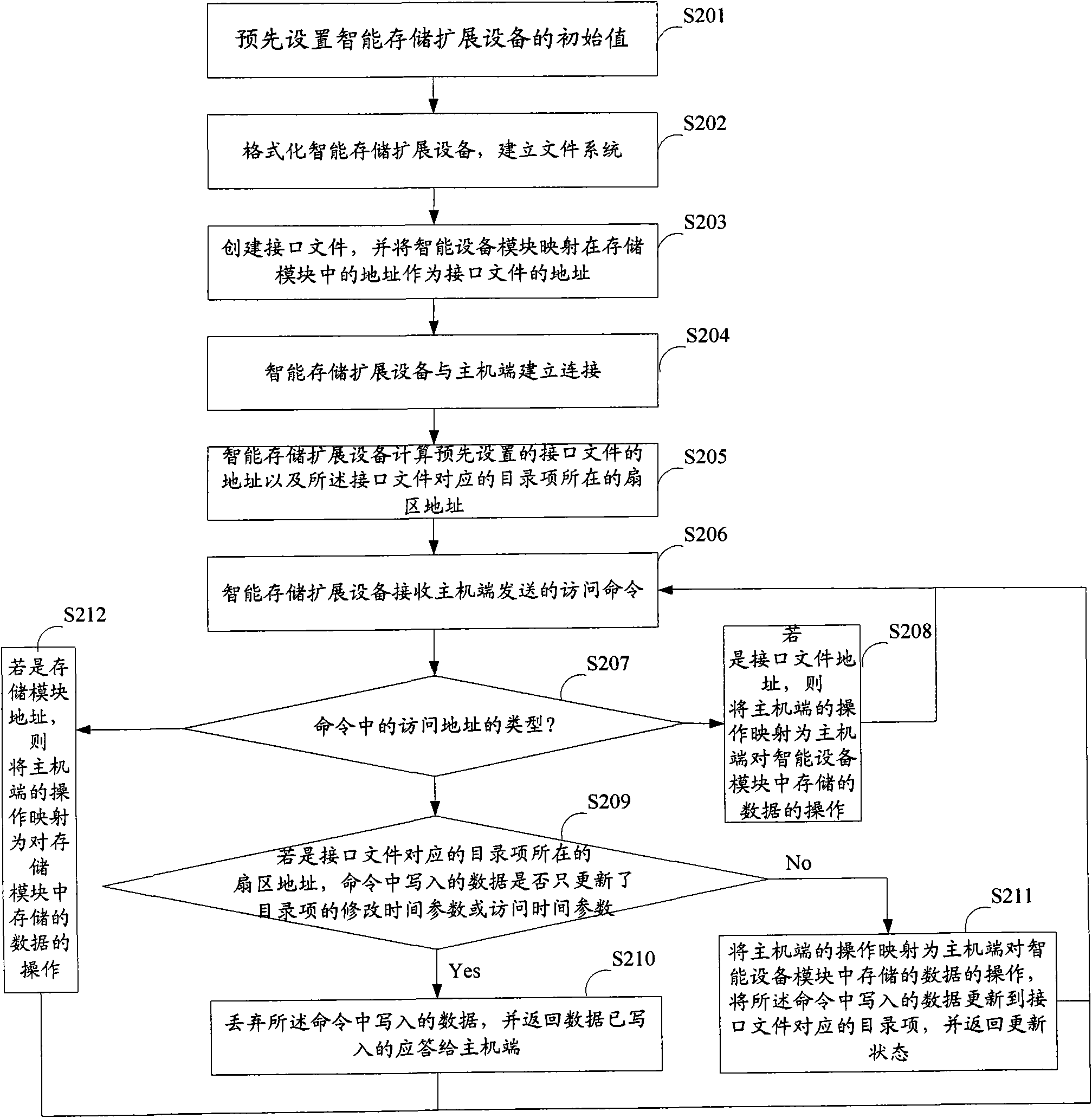

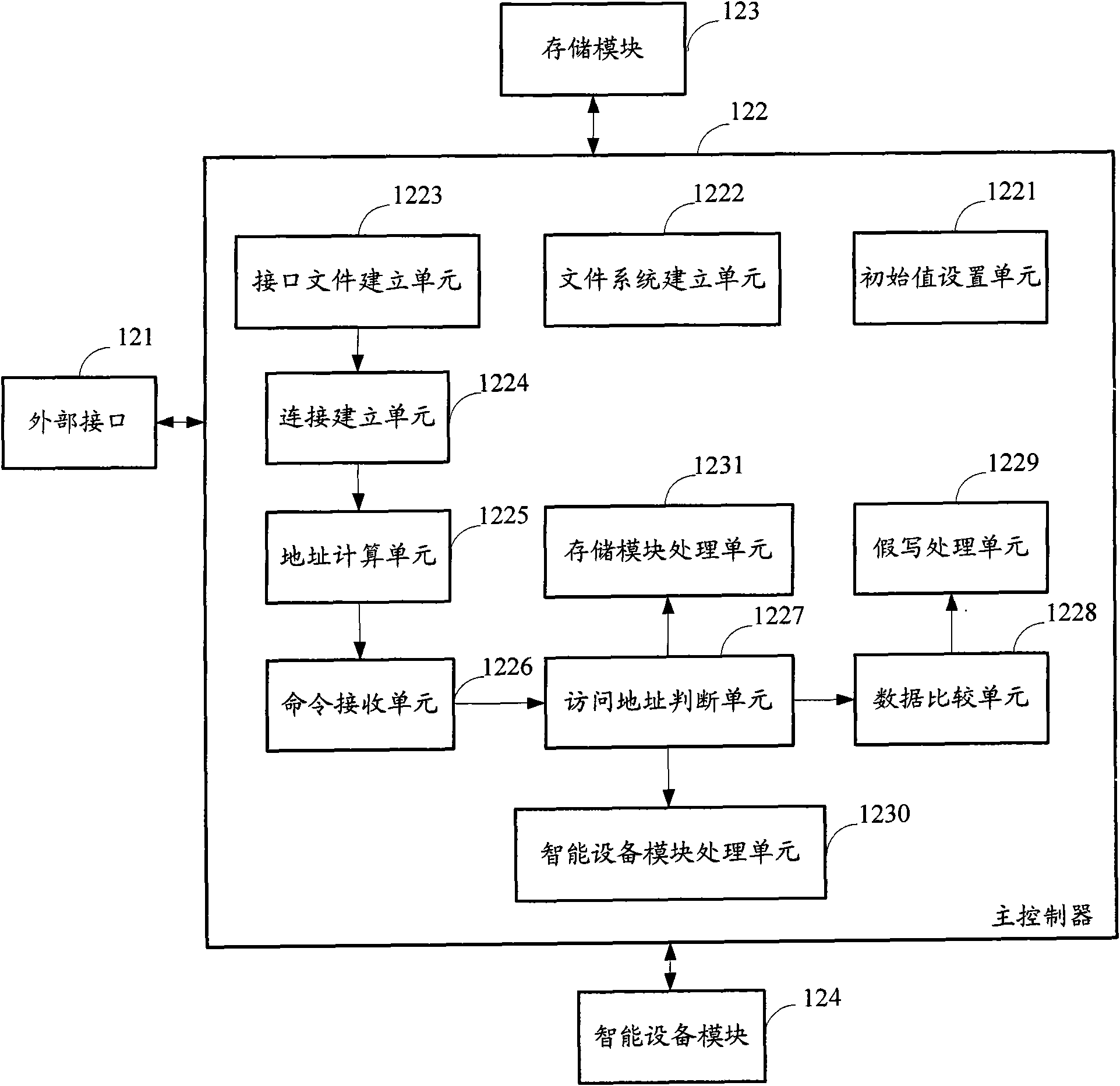

Intelligent storage and expansion equipment and access control system and method thereof

ActiveCN101901227AReduce the number of erasuresExtend your lifeSpecial data processing applicationsControl systemAccess time

The invention is suitable for the technical field of information storage and provides intelligent storage and expansion equipment and an access control system and an access control method thereof. The method comprises the following steps of: receiving an access command sent by a host by the intelligent storage and expansion equipment; judging whether an access address written in the command is a section address where a directory entry corresponding to an interface file is; if the access address is the section address, comparing data written in the command with initial data in the directory entry corresponding to the interface file and judging whether the data written in the command only updates a modification time parameter or an access time parameter of the directory entry corresponding to the interface file; and when the data written in the command only updates the modification time parameter or the access time parameter of the directory entry corresponding to the interface file, discarding the data written in the command by the intelligent storage and expansion equipment and returning a response in which the data is already written to the host. In the method, times of rewriting in a storage module are reduced, and the service life of the storage module is greatly prolonged.

Owner:SHENZHEN NETCOM ELECTRONICS CO LTD

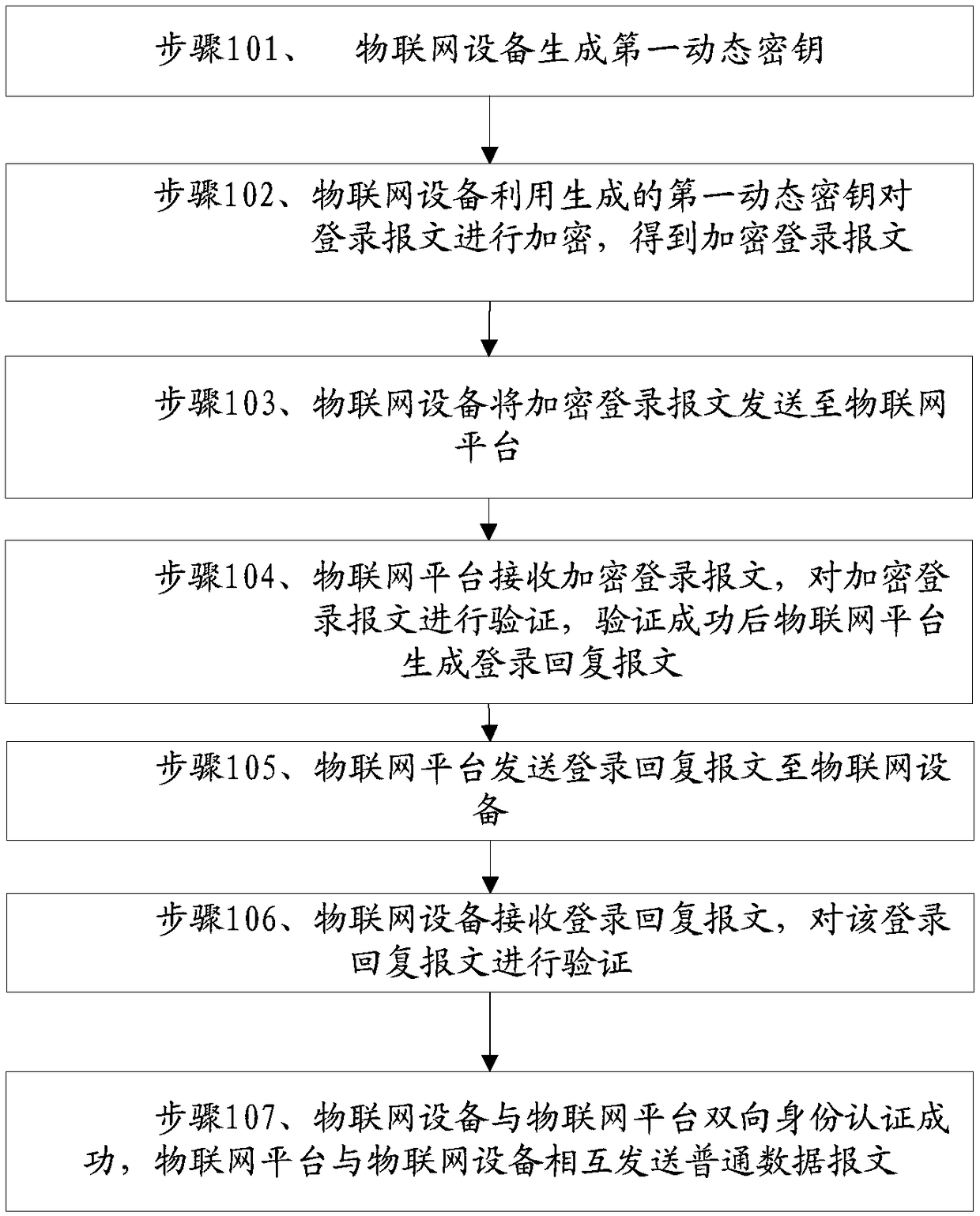

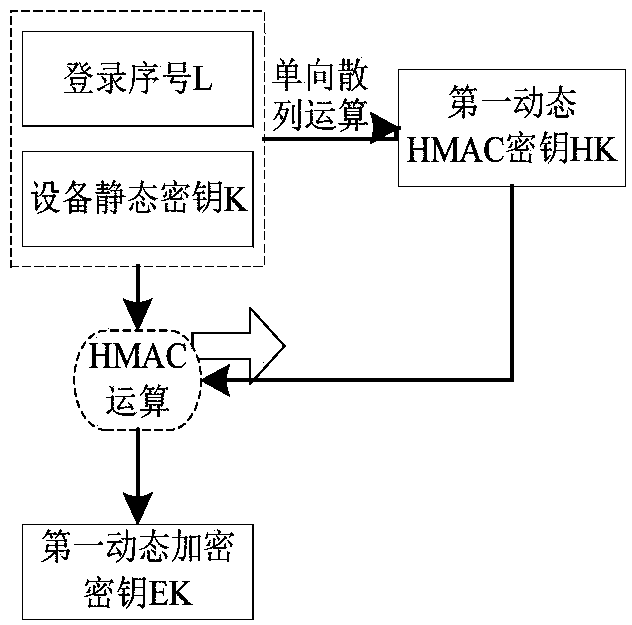

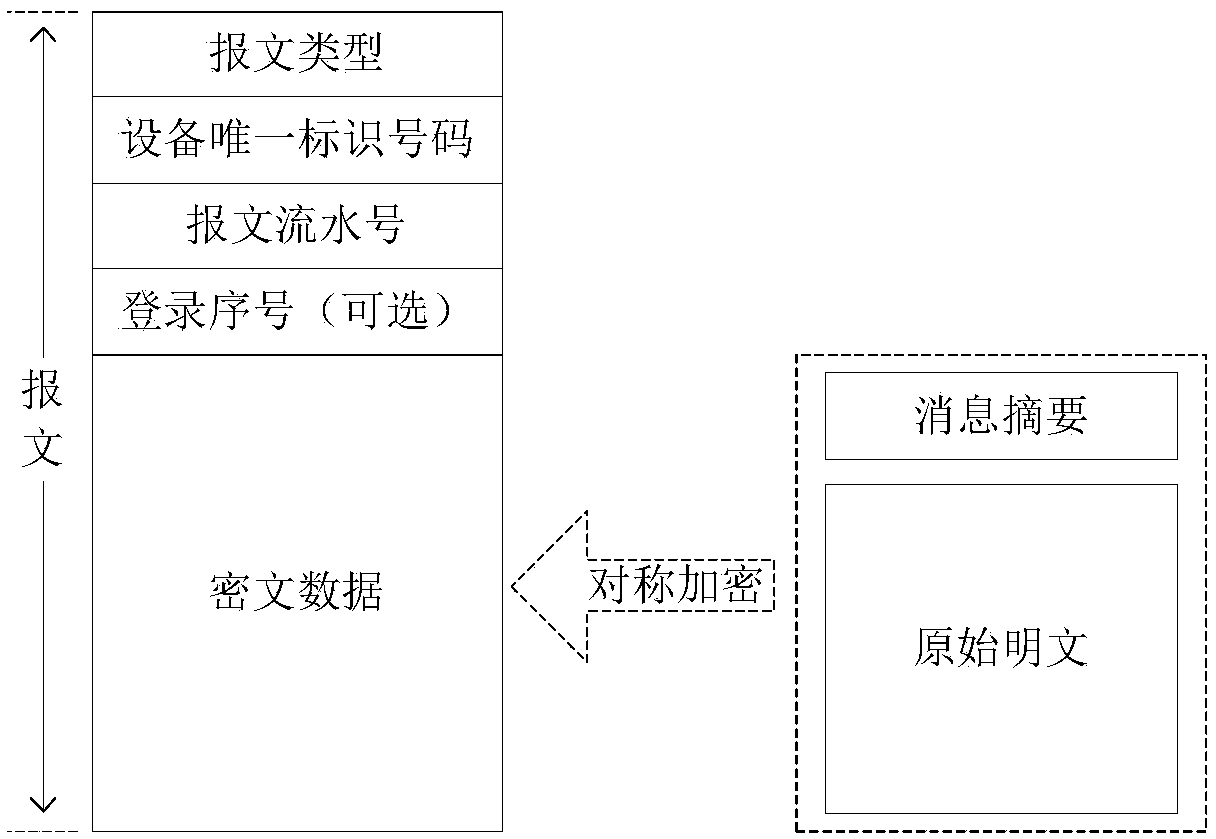

Dynamic encryption method for Internet of Things device based on login serial number

ActiveCN109361520ALow costReduce power consumptionKey distribution for secure communicationUser identity/authority verificationThe InternetSerial code

The application discloses a dynamic encryption method for an Internet of Things device based on a login serial number. The method includes steps: the Internet of Things device generates a first dynamic secret key; the Internet of Things device encrypts a login message by employing the generated first dynamic secret key and obtains an encrypted login message; the Internet of Things device transmitsthe encrypted login message to an Internet of Things platform; the Internet of Things platform receives and verifies the encrypted login message, and generates a login reply message after verification; the Internet of Things platform transmits the login reply message to the Internet of Things device; the Internet of Things device receives and verifies the login reply message; and bidirectional identity authentication of the Internet of Things device and the Internet of Things platform is successful, and the Internet of Things platform and the Internet of Things device mutually transmit ordinary data messages. According to the method, the pseudo-random dynamic secret key is generated through a static secret key and the login serial number of the Internet of Things device, and the securityof communication between the Internet of Things device and the Internet of Things platform is improved.

Owner:TAIHUA WISDOM IND GRP CO LTD

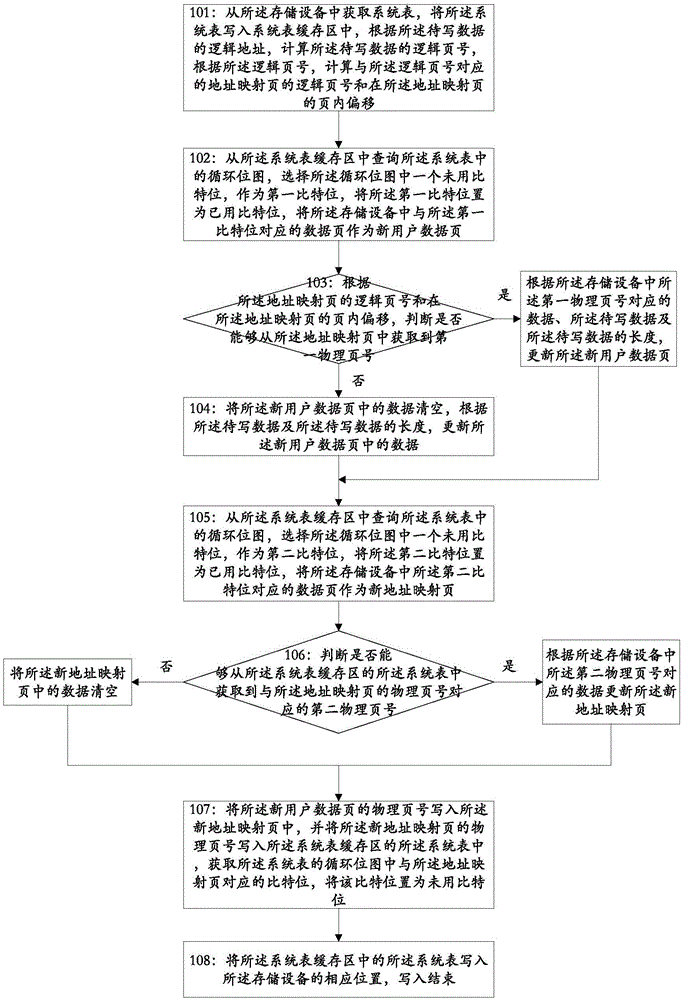

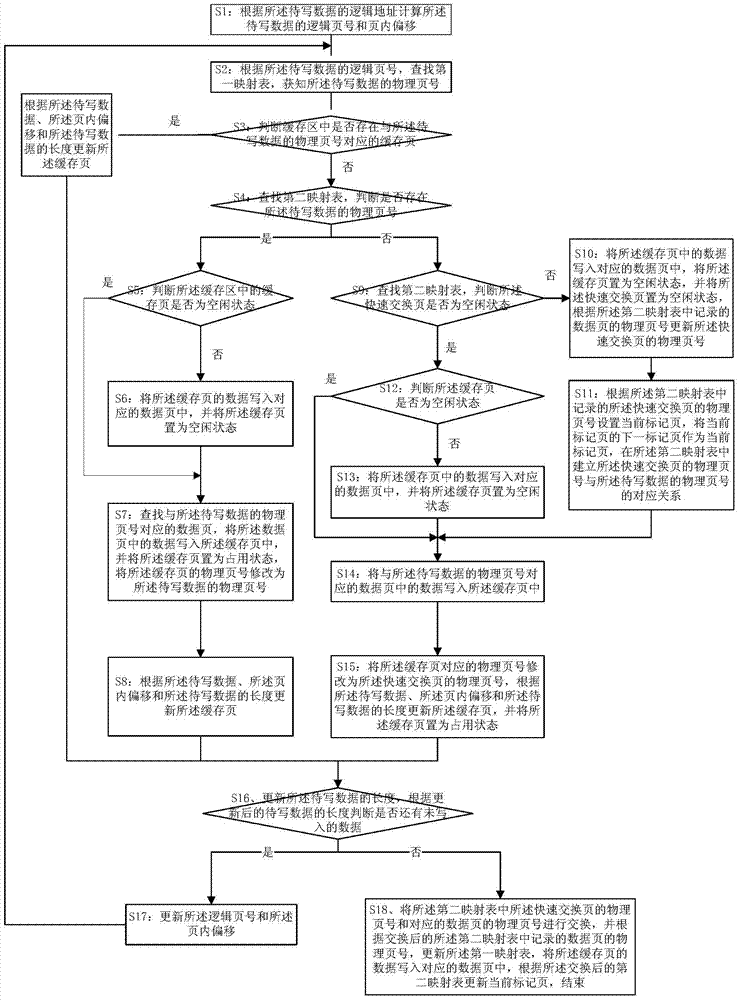

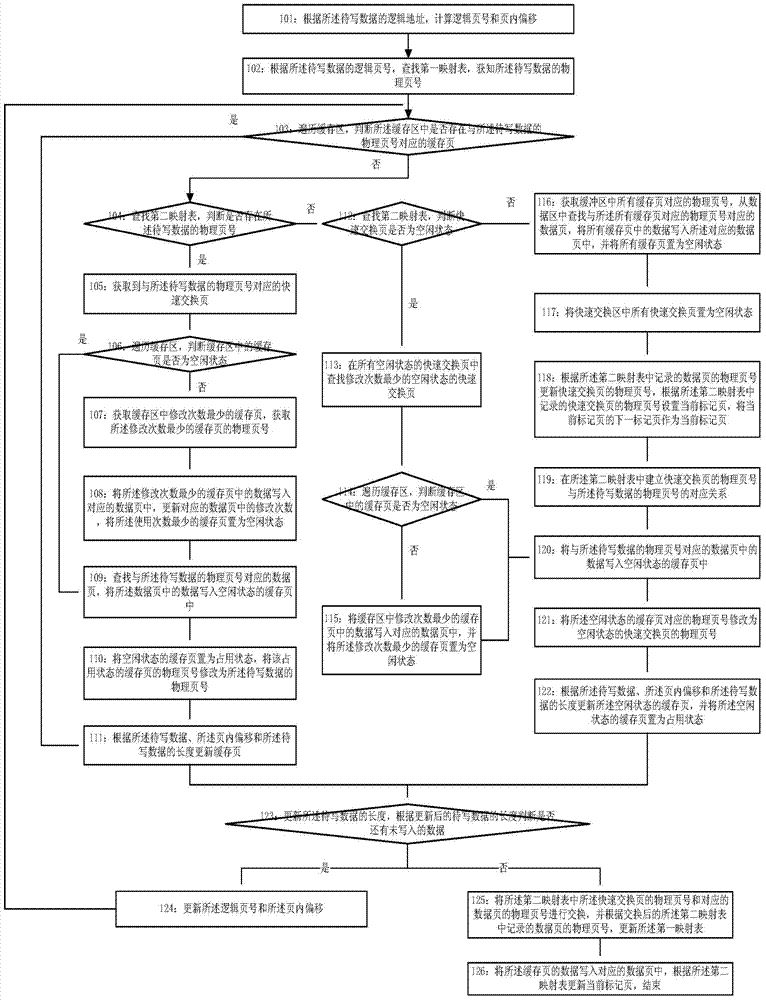

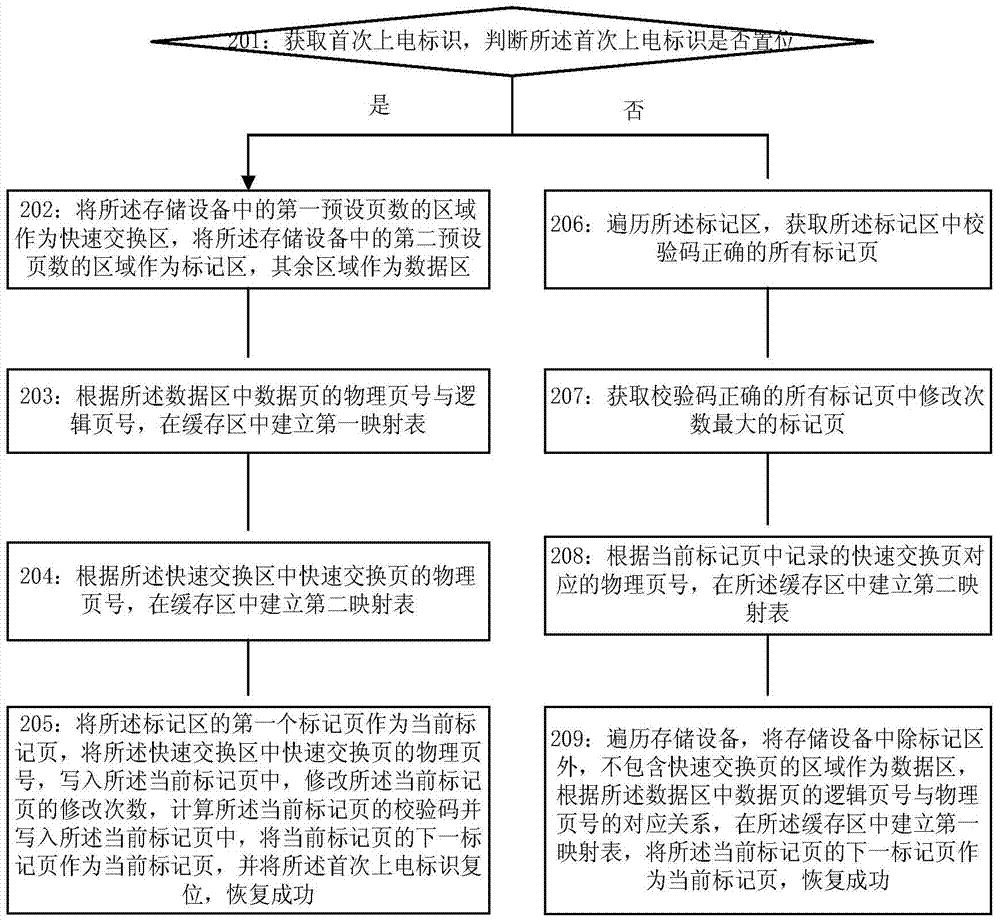

Method for writing data into storage equipment

ActiveCN103699341AReduce the number of erasuresAchieve wear levelingInput/output to record carriersMemory adressing/allocation/relocationElectricityData loss

The invention discloses a method for writing data into storage equipment and belongs to the technical field of storage. The method comprises the step of when data to be written is written to the storage equipment, writing the data to be written into the storage equipment by the processing on a cache area, a fast change area, a first mapping table, a second mapping table and a mark area according to the data to be written, the length of the data to be written and the logic address of the data to be written. The erasing times of the storage equipment are reduced by adopting cache; the data loss during power off is prevented by adopting the mark area; the abrasion balance of the storage equipment in the use process is realized by adopting the fast change area, and the service life of the storage equipment is ensured; the space of the storage equipment is saved by adopting the mode of storing the mapping tables into the cache area.

Owner:FEITIAN TECHNOLOGIES

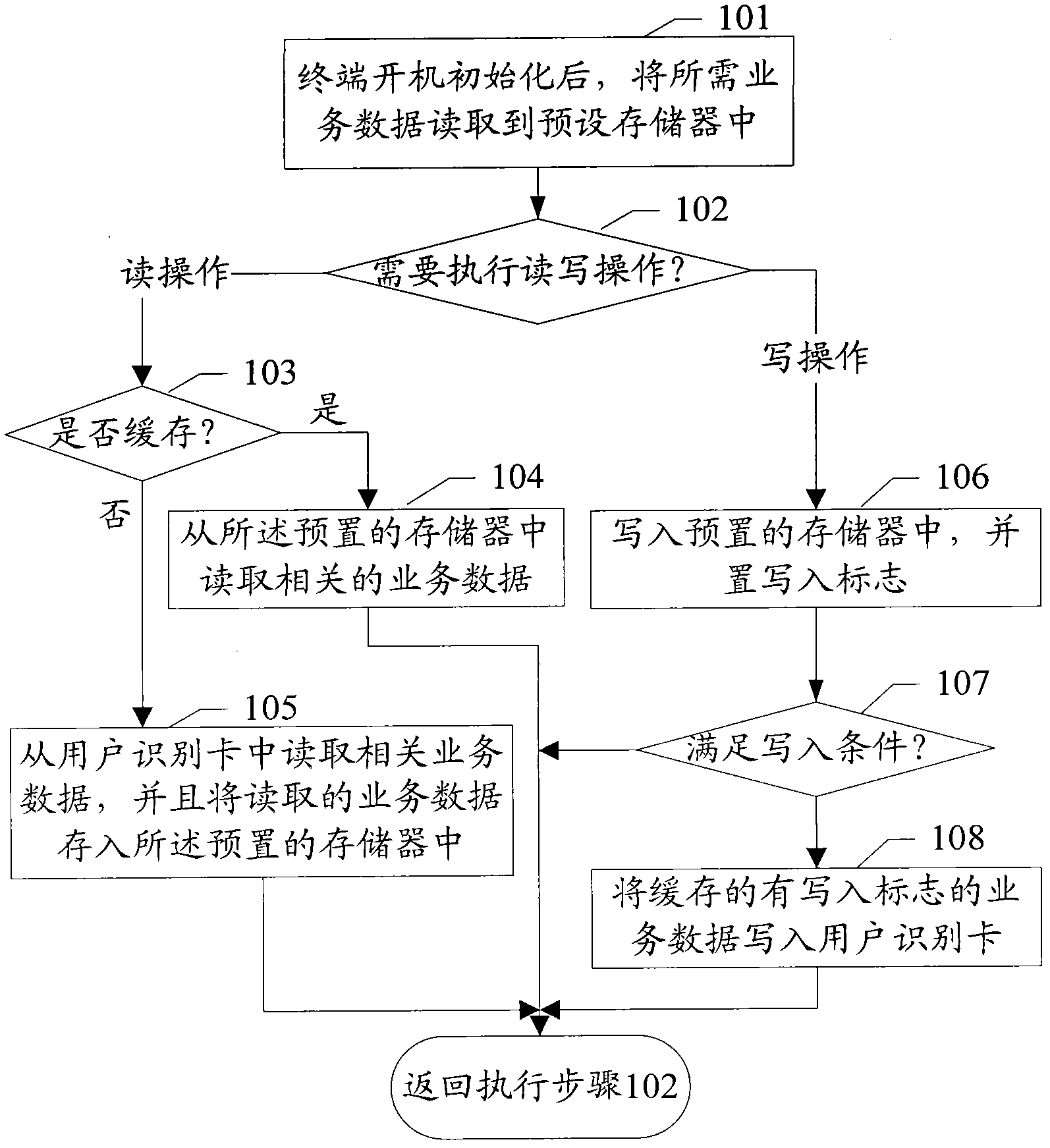

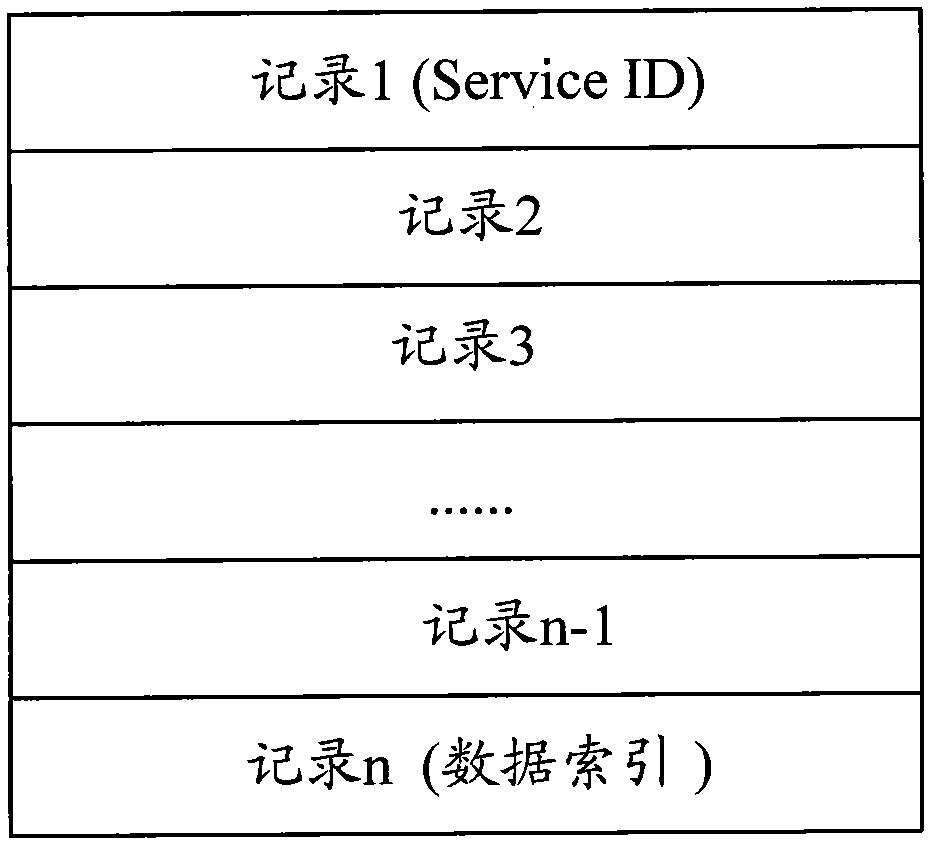

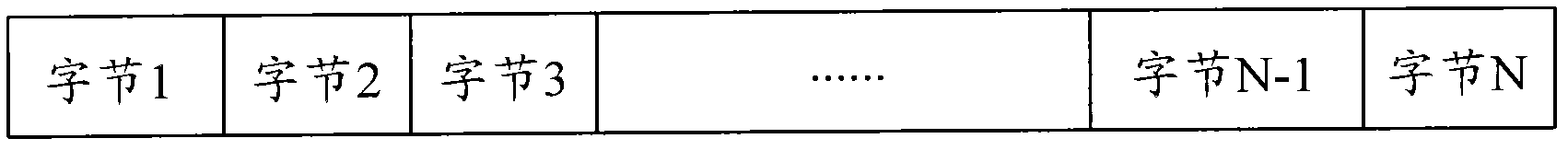

Method and device for decreasing frequency of erasing and writing subscriber identity module files

InactiveCN102402698AExtended service lifeLow costCo-operative working arrangementsSensing record carriersThe InternetSubscriber identity module

The invention discloses a method and a device for decreasing the frequency of erasing and writing subscriber identity module files, which are used for solving the problems of too short service lives of subscriber identity modules, unsmooth business operation and the like due to the fact that the subscriber identity modules are erased and written frequently in businesses of the internet of things in the environment of the internet of things. The method employs linear fixed-length files infrequently used in some businesses of a subscriber identity module, pre-reading fixed-length files enter a terminal storage area, the operating speed of a business system is increased, erasing and writing for the subscriber identity module are firstly stored in a terminal storage card in operation of the business system, and then the subscriber identity module is erased and written after read-in conditions are met, so that the frequency of visiting the subscriber identity module is decreased effectively, and the service life of the subscriber identity module is prolonged.

Owner:ZTE CORP

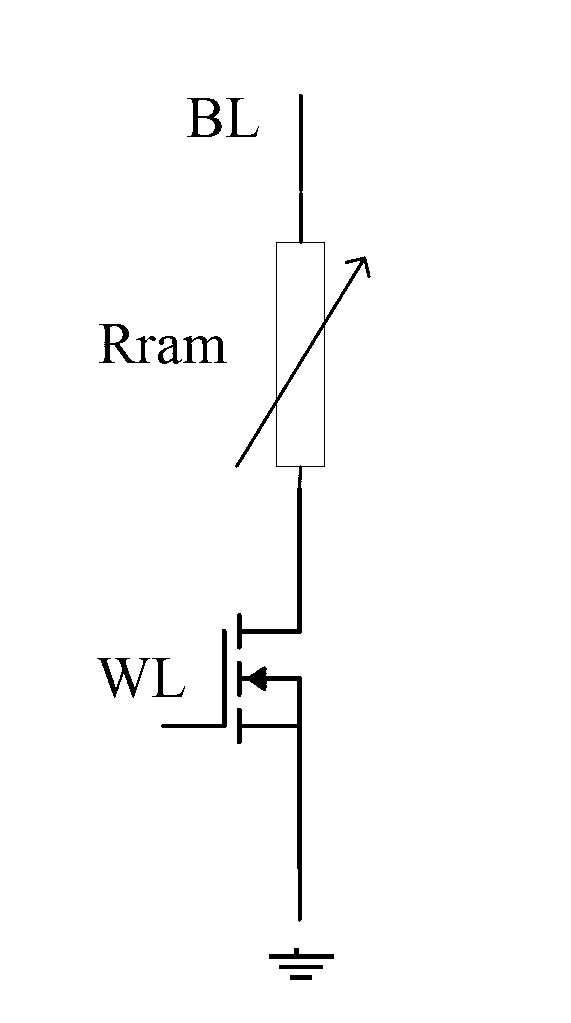

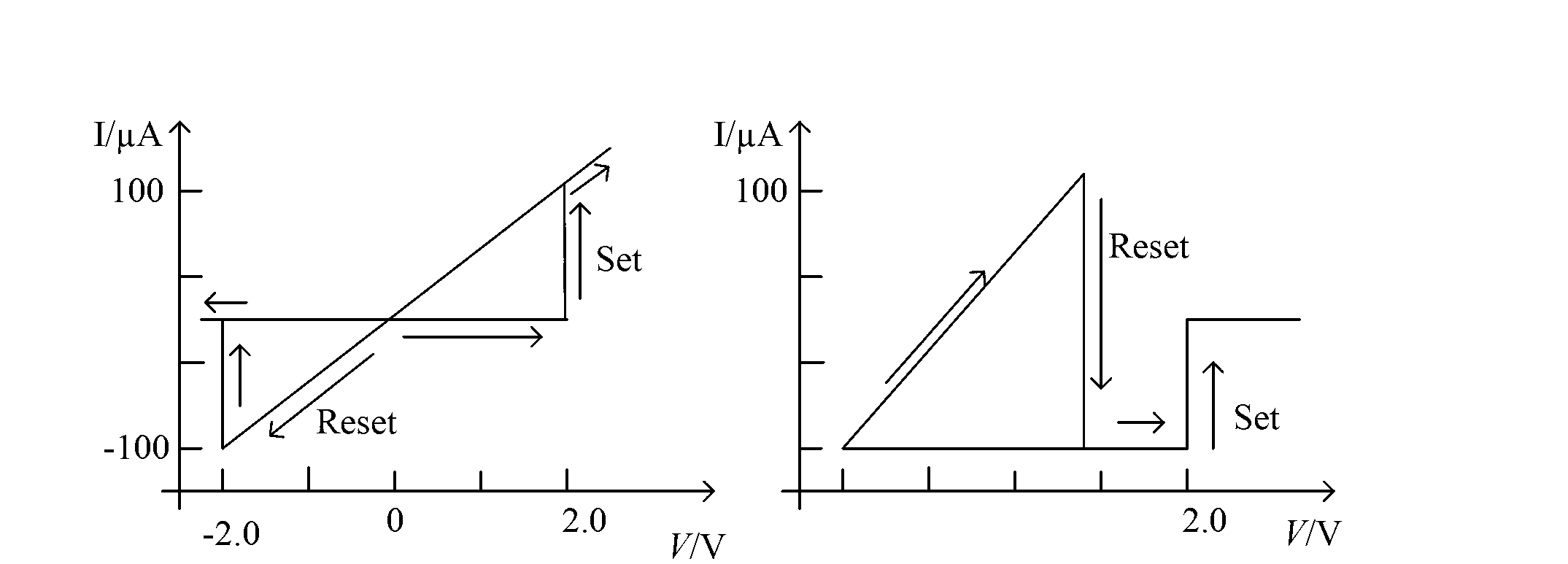

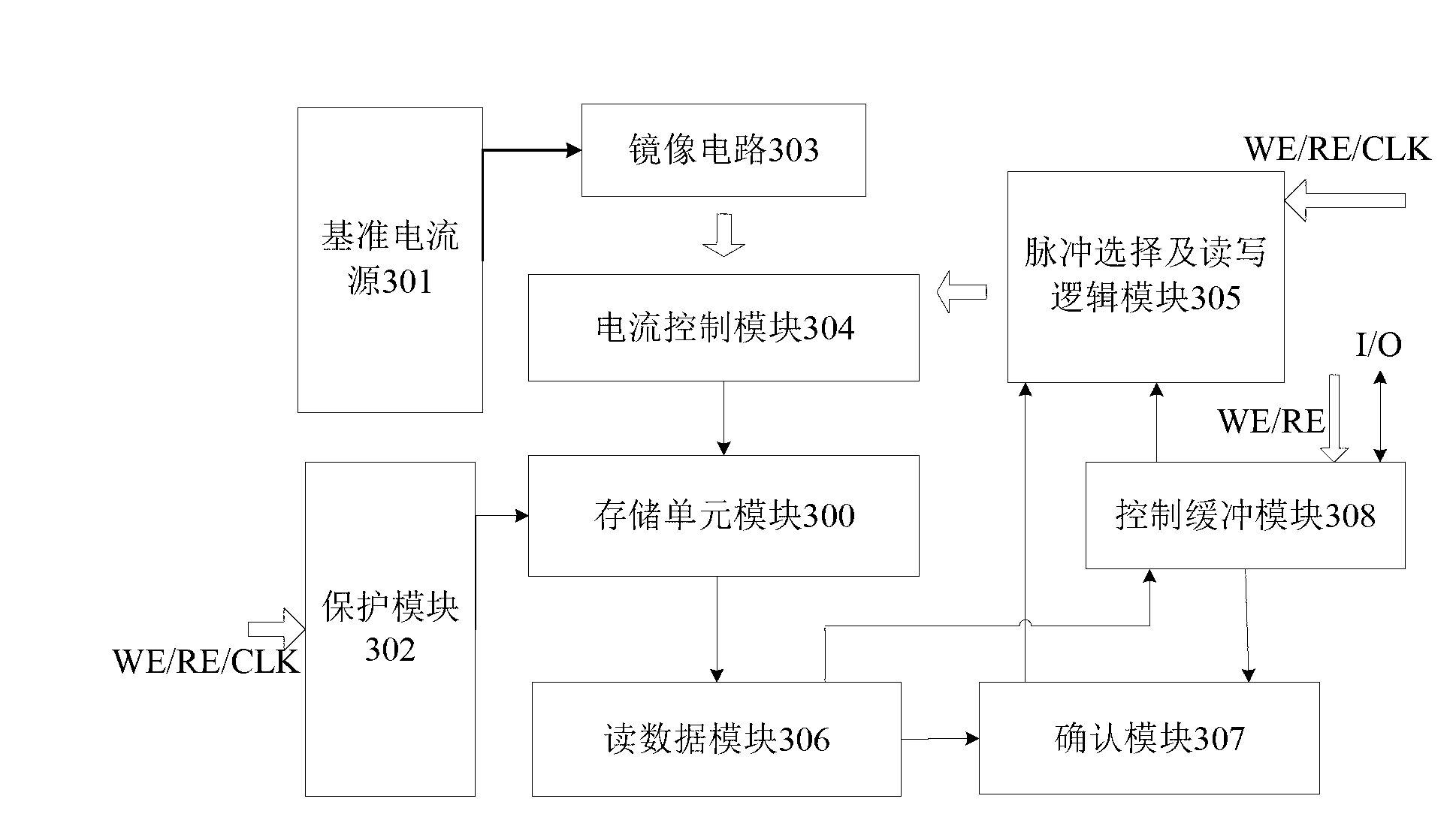

Pre-writing reading circuit of resistive random access memory and operation method thereof

InactiveCN103021458AExtended service lifeReduce the number of erasuresDigital storageElectricityStatic random-access memory

The invention discloses a pre-writing reading circuit of resistive random access memory. The pre-writing reading circuit includes a memory unit module, a reference current source module, a protection circuit module, a mirror circuit module, a current control module, a pulse selection and read-write logic module, a data reading module, a confirmation module, and a control buffer module. The input end of the memory unit module is respectively connected to the output end of the current control module and the output end of the protection circuit module. The output end of the memory unit module is in connection with the input end of the data reading module. A reference voltage source and a current-generating resistor are built in the reference current source module, the output end of which is in connection with the input end of the mirror circuit module. The input end of the protection circuit module is in electric connection with an external writing-read enable signal and a clock signal. The output end of the mirror circuit module is electrically connected to one input end of the current control module. The pre-writing reading circuit provided in the invention can, to some extent, solve the problems of frequent resistive random access memory unit operation, short resistive random access memory service life, and low memory unit reliability.

Owner:HUAZHONG UNIV OF SCI & TECH

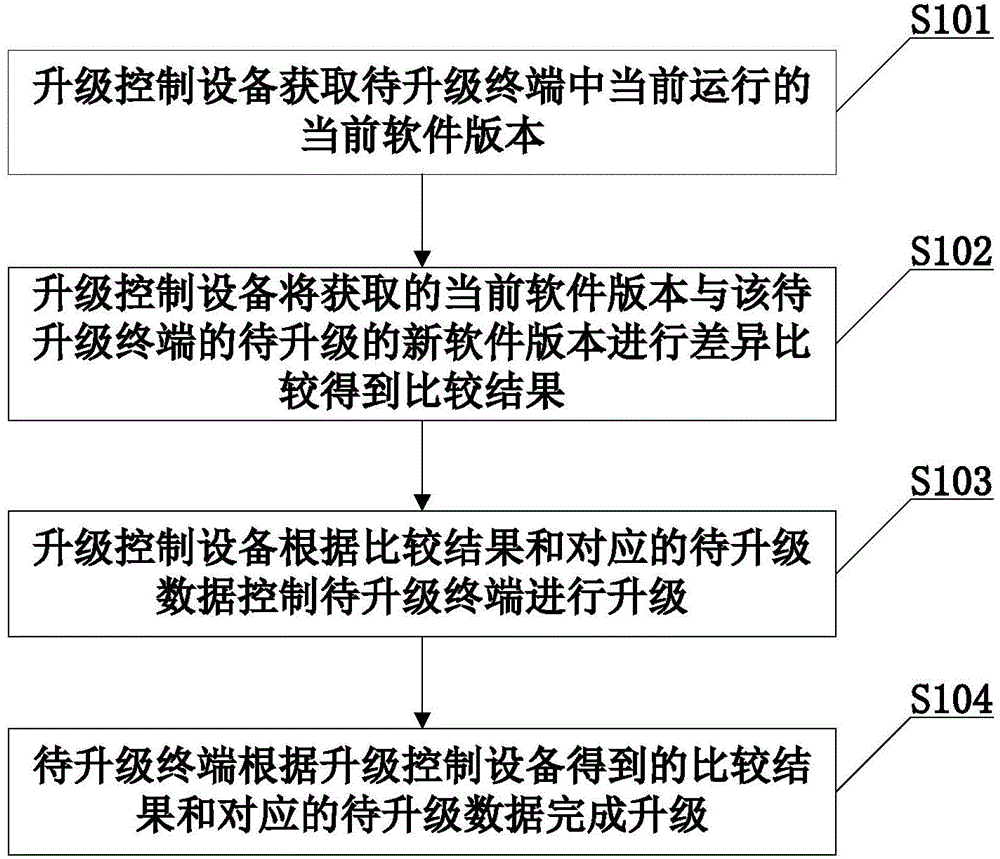

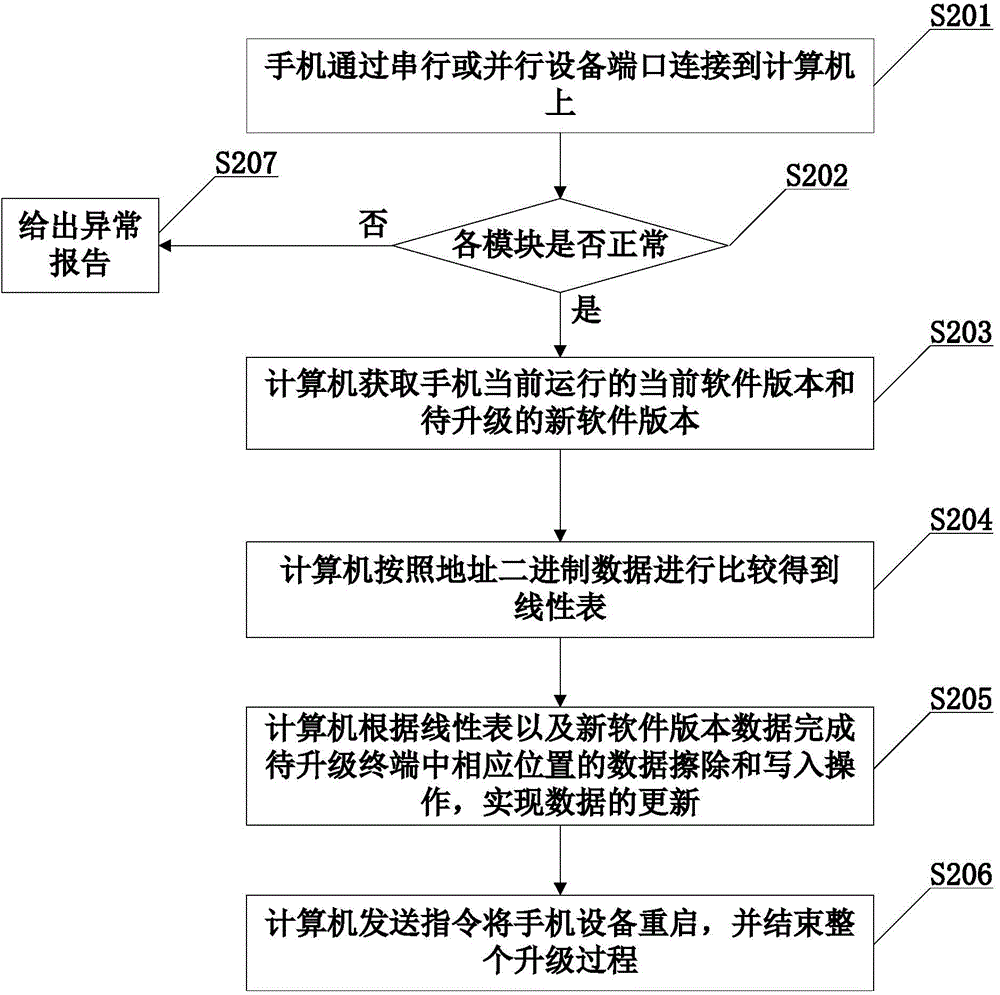

Update control device, terminal, terminal update method and system

InactiveCN105677375AShorten the timeImprove upgrade efficiencyProgram loading/initiatingTransmissionComputer terminalComputer engineering

The invention discloses an update control device, a terminal, a terminal update method and system; in a terminal update process, the update control device obtains the version of present running software in the to-be updated terminal, and carries out difference comparison between the present software version and a to-be updated novel software version of the to-be updated terminal, thus obtaining a comparison result; the update device can control the to-be updated terminal to finish update according to the difference comparison result and corresponding to-be updated data; i.e., in the update process, the to-be updated terminal can selectively update according to the difference between the present running software version and the to-be updated novel software version. The terminal will directly update the whole original software version in an update process in the prior; the novel method and device can solve said problems, thus obviously reducing Flash erase frequency by the to-be updated terminal in the update process, reducing terminal update time, improving terminal update efficiency, shortening terminal production period, and reducing production cost.

Owner:ZTE CORP

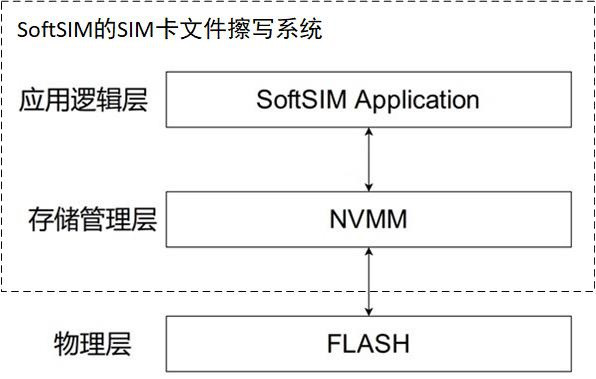

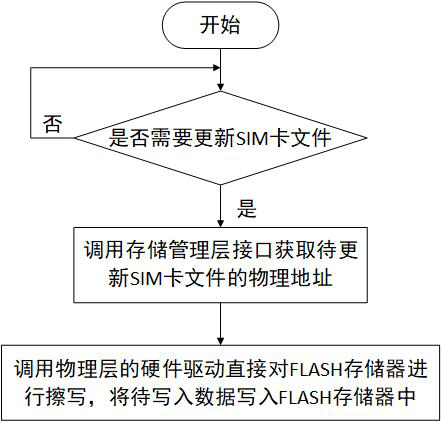

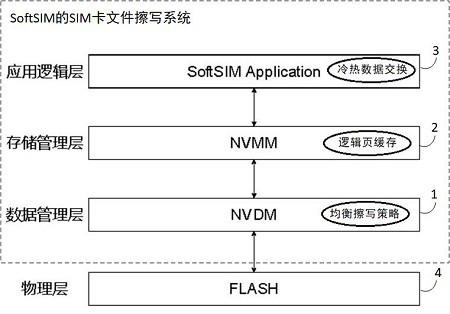

SIM card file erasing and writing system and method applied to SoftSIM and readable storage medium

ActiveCN112231244AErase levelingBalanced Erase and Write TimesMemory systemsNetwork data managementEngineeringStorage management

The invention discloses an SIM card file erasing and writing system and method applied to SoftSIM and a computer readable storage medium. The system comprises a data management layer, a storage management layer and an application logic layer; the application logic layer exchanges the storage positions of the cold data and the hot data when the communication module chip is powered on, the situationthat in the long-term erasing and writing process, the erasing and writing frequency of the storage area of the hot data is far larger than that of the storage area of the cold data, and consequentlyloss is too fast is avoided, erasing and writing balance of all the storage areas is achieved, and meanwhile, when the SIM card file needs to be updated, the data to be written is cached into the logic page of the memory space; the storage management layer writes the to-be-written data in the logic page into the logic address space formed by the data management layer when the page changing condition is met, and then the data management layer writes the to-be-written data into the FLASH memory of the communication module chip, so that the erasing and writing frequency of the FLASH memory is reduced. By achieving erasing and writing balance and reducing erasing and writing times, the service life of the FLASH memory is effectively prolonged.

Owner:SHENZHEN JETLINK TECH CO LTD

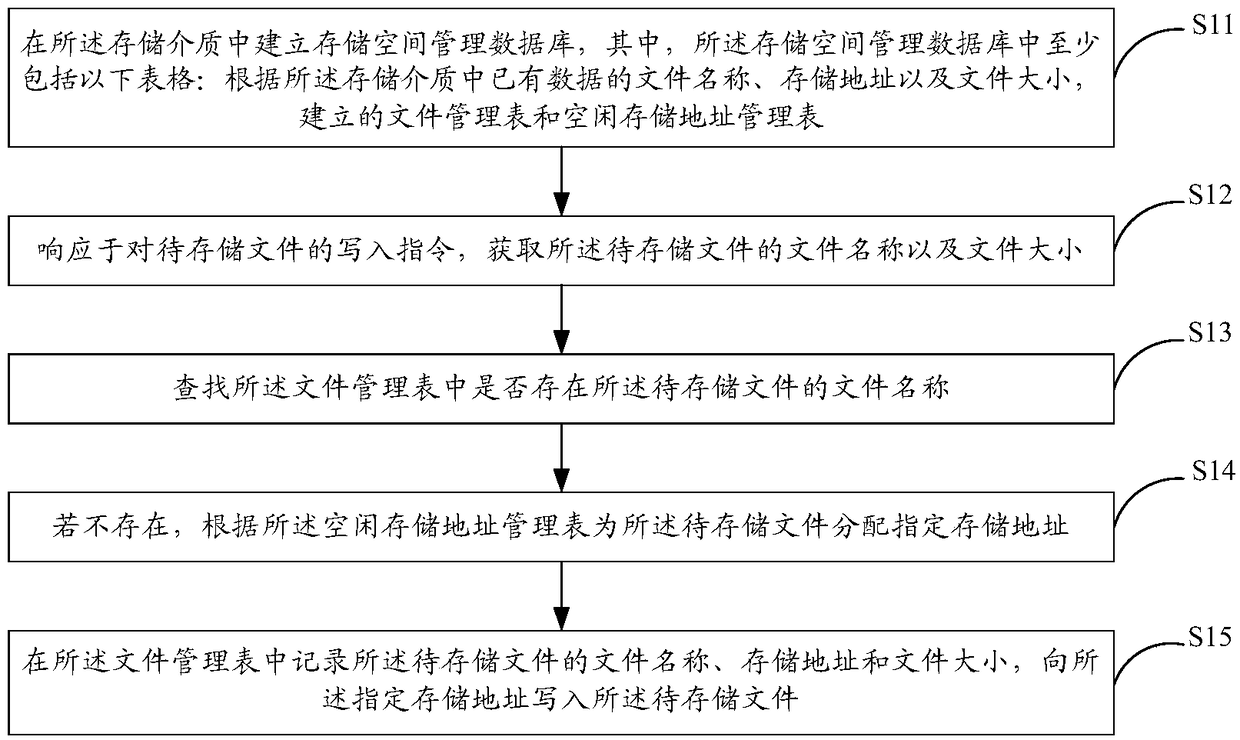

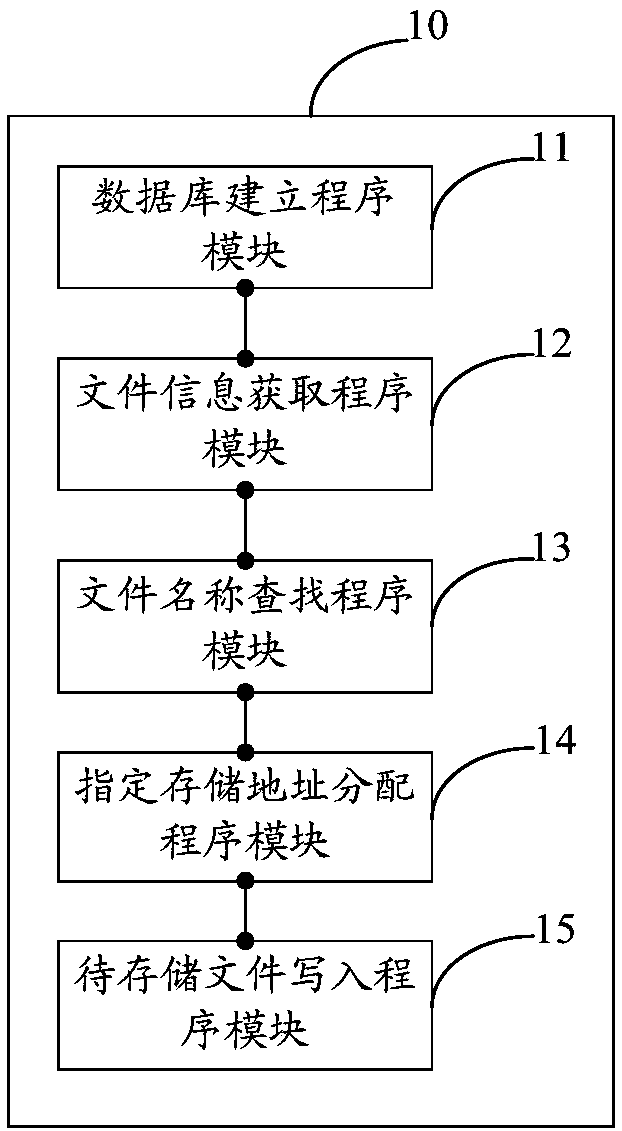

File management method and system for a fileless system storage medium

ActiveCN109189772AAdjust the interior spaceGuaranteed Cross-Platform PerformanceDigital data information retrievalSpecial data processing applicationsFile allocationFile system

An embodiment of the present invention provides a file management method for a fileless system storage medium. The method comprises the following steps of: establishing a storage space management database in a storage medium; obtaining a file name and a file size of a file to be stored in response to a write instruction of the file to be stored; looking for the file name of the file to be stored in the file management table; if not, assigning a designated storage address to the file to be stored according to the idle storage address management table; recording the file name, storage address and file size of the file to be stored in the file management table, and writing the file to be stored to the specified storage address. Embodiments of the present invention also provide a file management system for a fileless system storage medium. The embodiment of the invention provides the cross-platform performance of the fileless system storage medium and improves the reading and writing speedby recording and managing the storage space of the fileless system storage medium by using the file management table of the database and the idle storage address management table.

Owner:华清瑞达(天津)科技有限公司

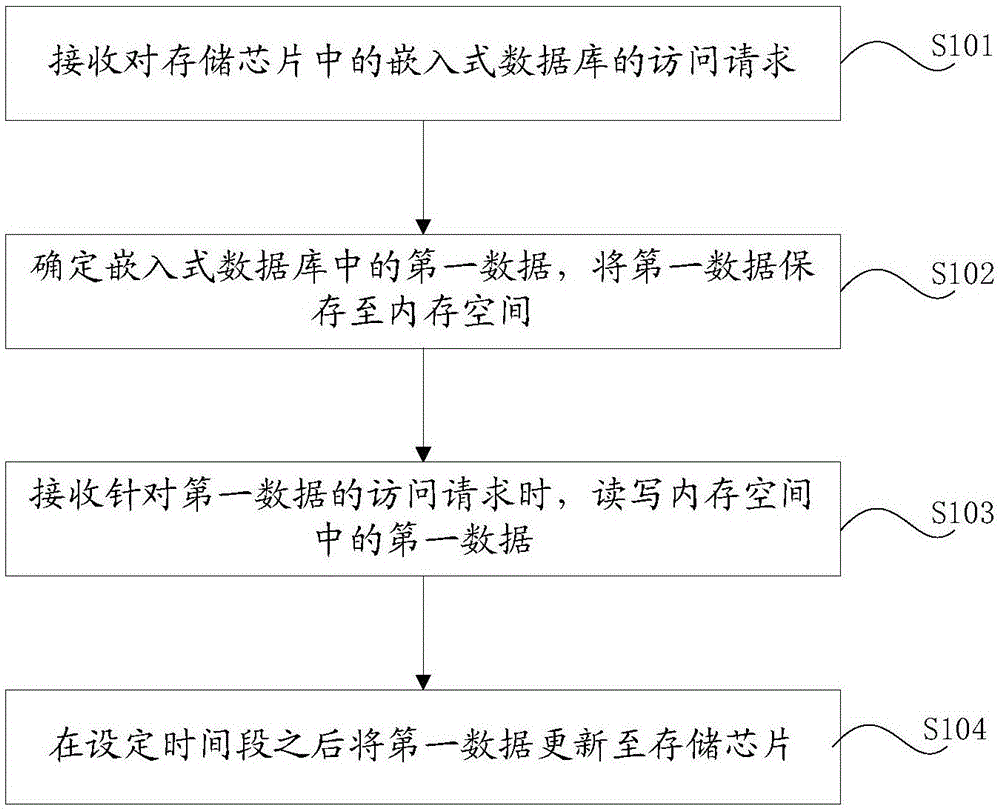

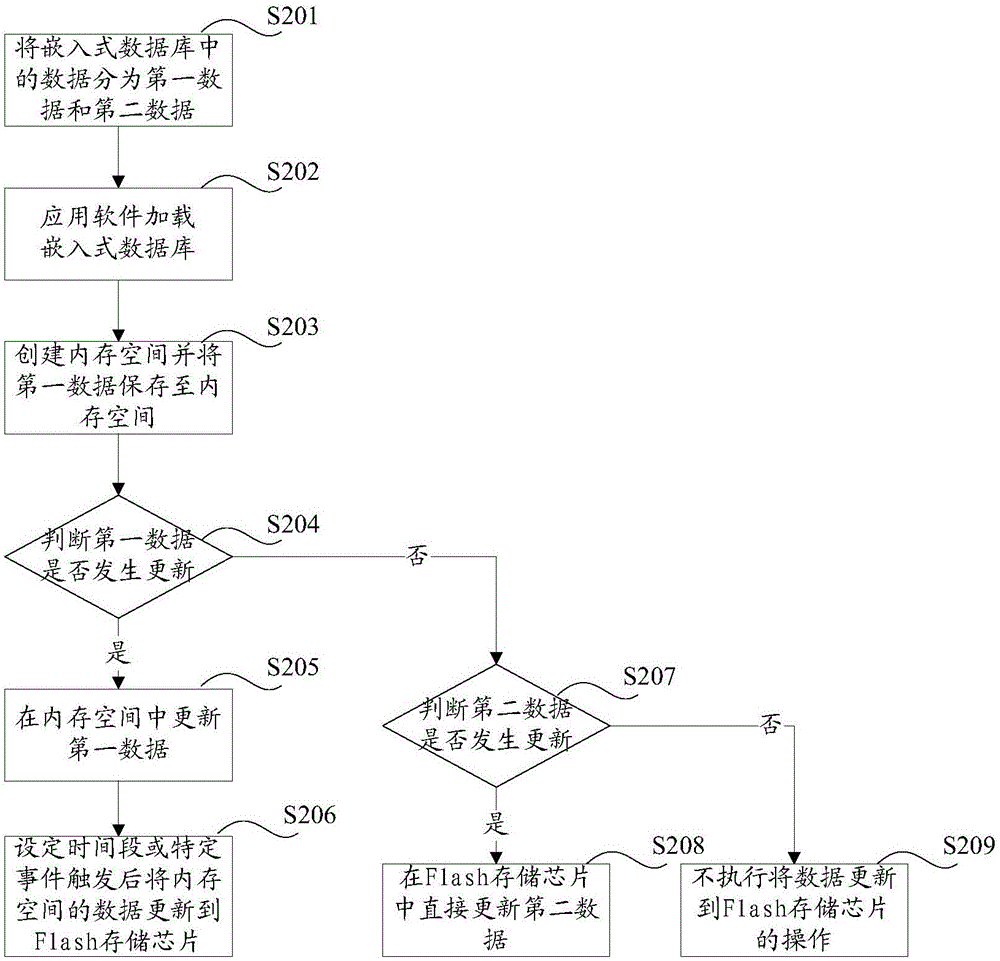

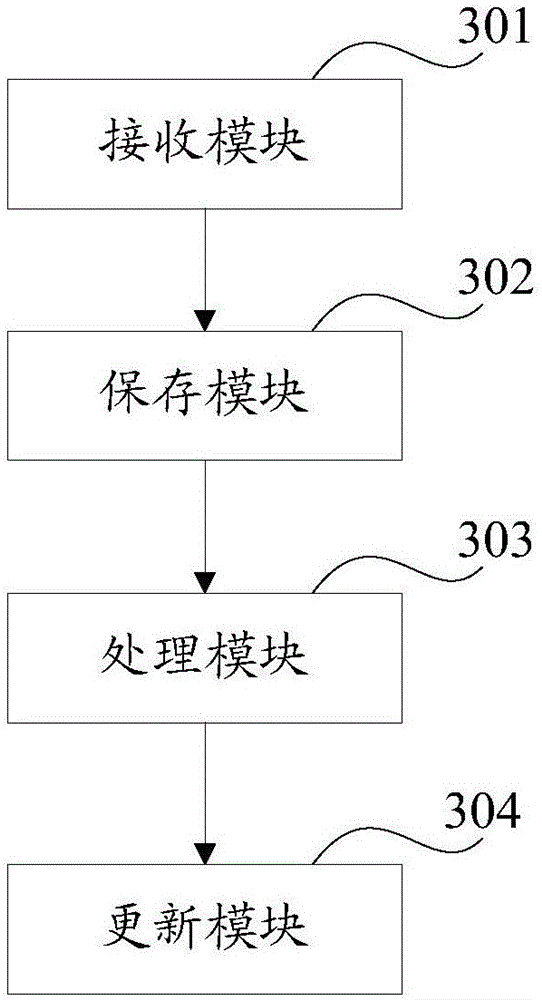

Data updating method and device

InactiveCN106649654AReduce the number of erasuresExtended service lifeDatabase updatingSpecial data processing applicationsEmbedded databaseData library

The embodiment of the invention provides a data updating method and device. The data updating method comprises the steps that an access request for an embedded database in a Flash storage chip is received, and first data in the embedded database is determined and then saved in a memory space, wherein when the access request for the first data is received, the first data in the memory space is read, written and then updated to the Flash storage chip after a set time period. According to the method, when a read-write operation is conducted on the first data in the embedded database, the first data is not updated to the Flash storage chip after each time of the read-write operation but saved in the memory space, the read-write operation on the first data is executed in the memory space, the first data is updated to the Flash storage chip after the set time period, therefore, the erasing frequency of the Flash storage chip is significantly decreased, then the service life of the Flash storage chip is prolonged, and the equipment maintenance cost is reduced.

Owner:COMBA TELECOM SYST CHINA LTD

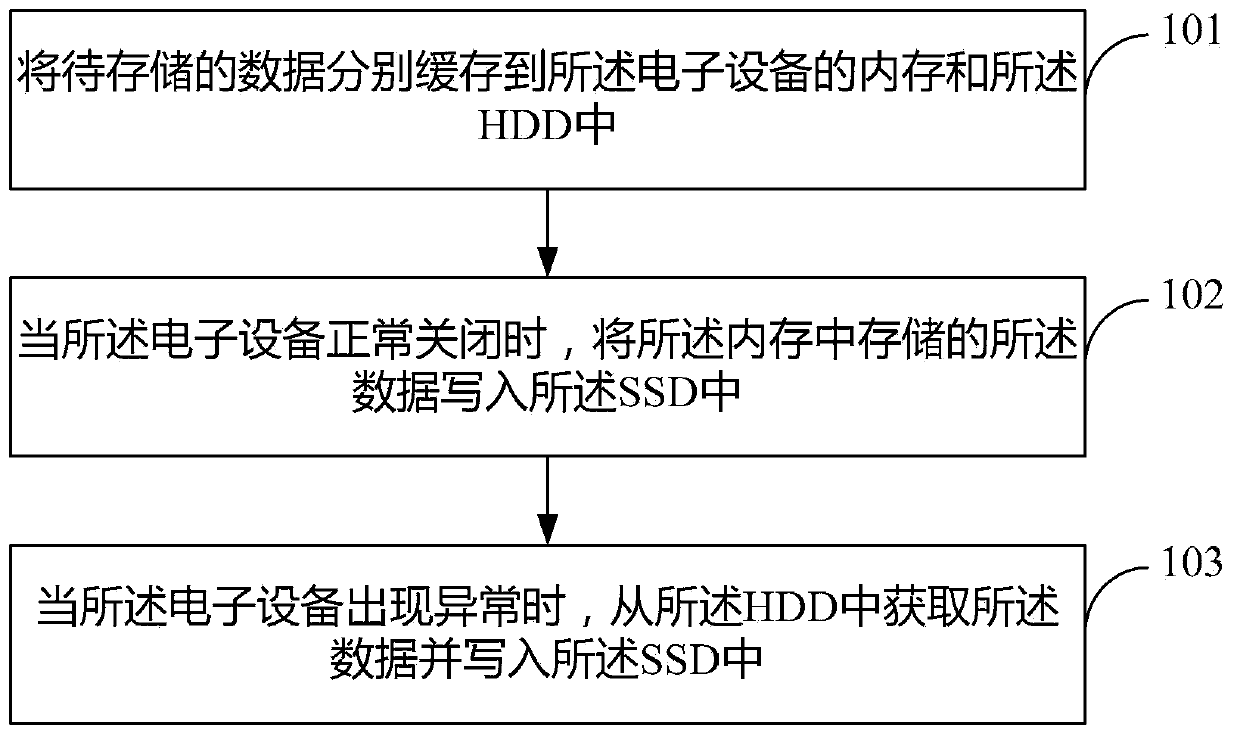

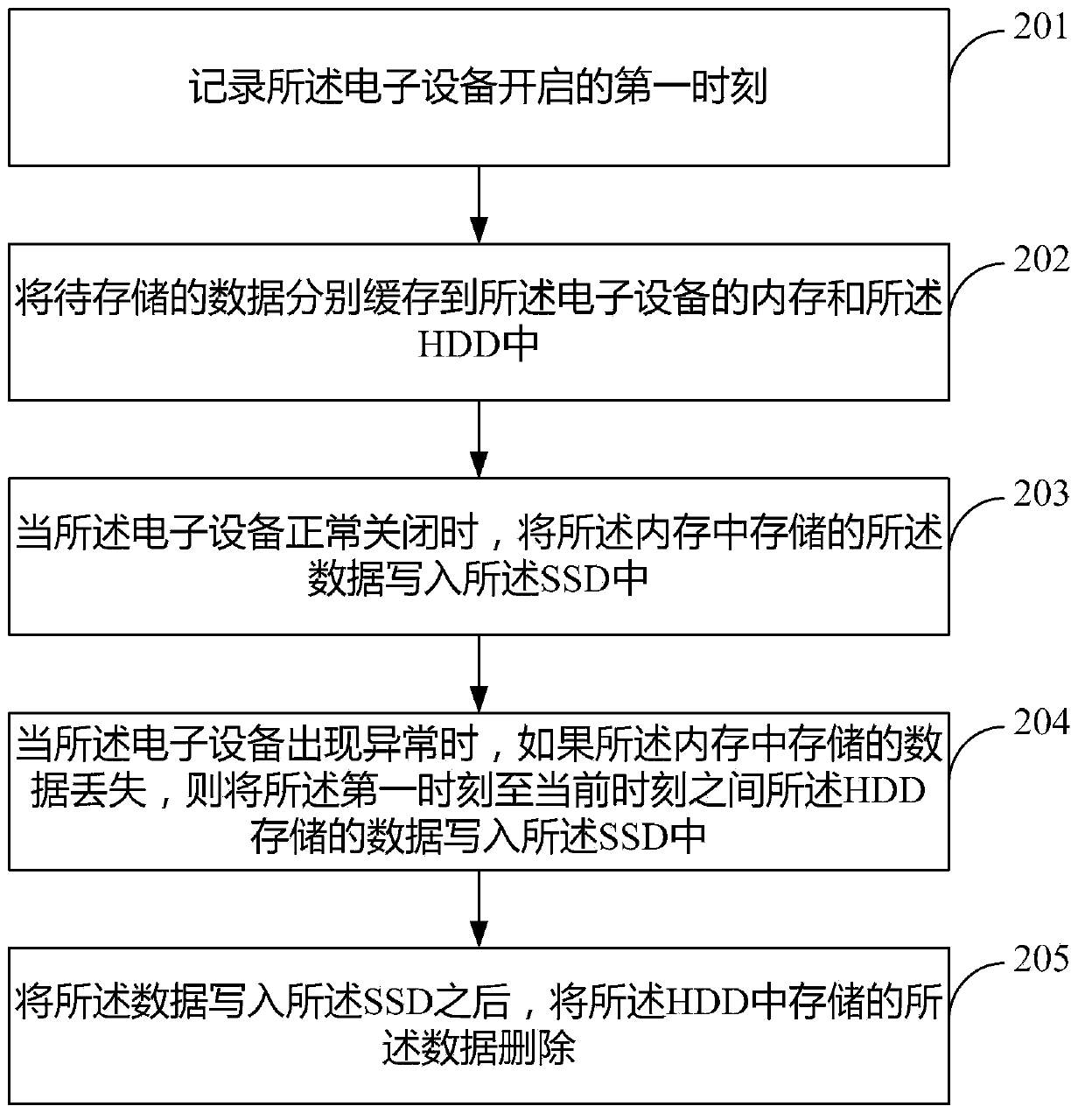

Data storage method and electronic device

InactiveCN103970684AAchieve recoveryReduce the number of erasuresMemory loss protectionInternal memorySolid-state drive

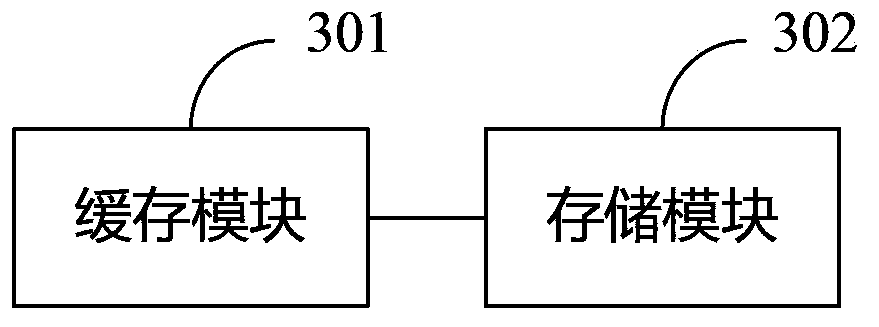

The invention discloses a data storage method and an electronic device and belongs to the field of data storage. The data storage method is applied to the electronic device, and the electronic device is connected with an HDD (hard disk drive) and an SSD (solid state drive). The data storage method includes respectively caching data to be stored into an internal memory and the HDD of the electronic device; writing the data stored in the internal memory into the SSD when the electronic device is normally shut down; acquiring the data from the HDD and writing into the SSD when the electronic device is abnormal. The electronic device comprises a cache module and a storage module. Accordingly, erasing and writing times of the SSD is decreased, service life of the SSD is prolonged, and safety and reliability of data storage are effectively improved.

Owner:LENOVO (BEIJING) LTD

Method and system for storing data by using Flash and RAM (random-access memory)

InactiveCN103761197AReduce the number of erasuresExtended service lifeMemory loss protectionElectricityRandom access memory

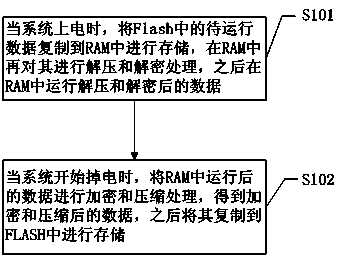

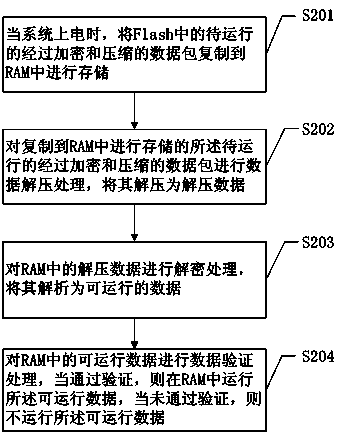

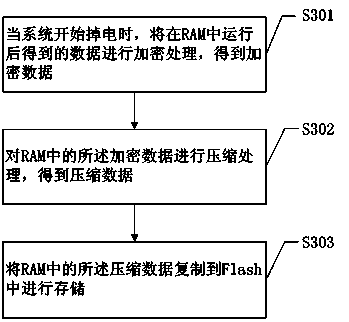

The invention provides a method and a system for storing data by using a Flash and a Ram (random-access memory). The method comprises the following steps of copying data to be run in the Flash into the RAM and storing the data to be run in the RAM when the system is powered on; decompressing and decrypting the data to be run in the RAM; running the decompressed and decrypted data in the RAM; encrypting and compressing the data running in the RAM to obtain encrypted and compressed data when the system is powered down; and copying the encrypted and compressed data into the Flash and storing the encrypted and compressed data in the Flash. Because a compression algorithm is performed on the data, the storage quantity of the data in the Flash is greatly increased, and the downloading speed and the uploading speed of the data are also increased. Moreover, the data only run in the RAM; and when the system is powered down, the data are stored in the FLASH, so that the erasing frequency of the FLASH is reduced, and the service life of the FLASH is prolonged.

Owner:SHENZHEN UNIMAT AUTOMATION TECH

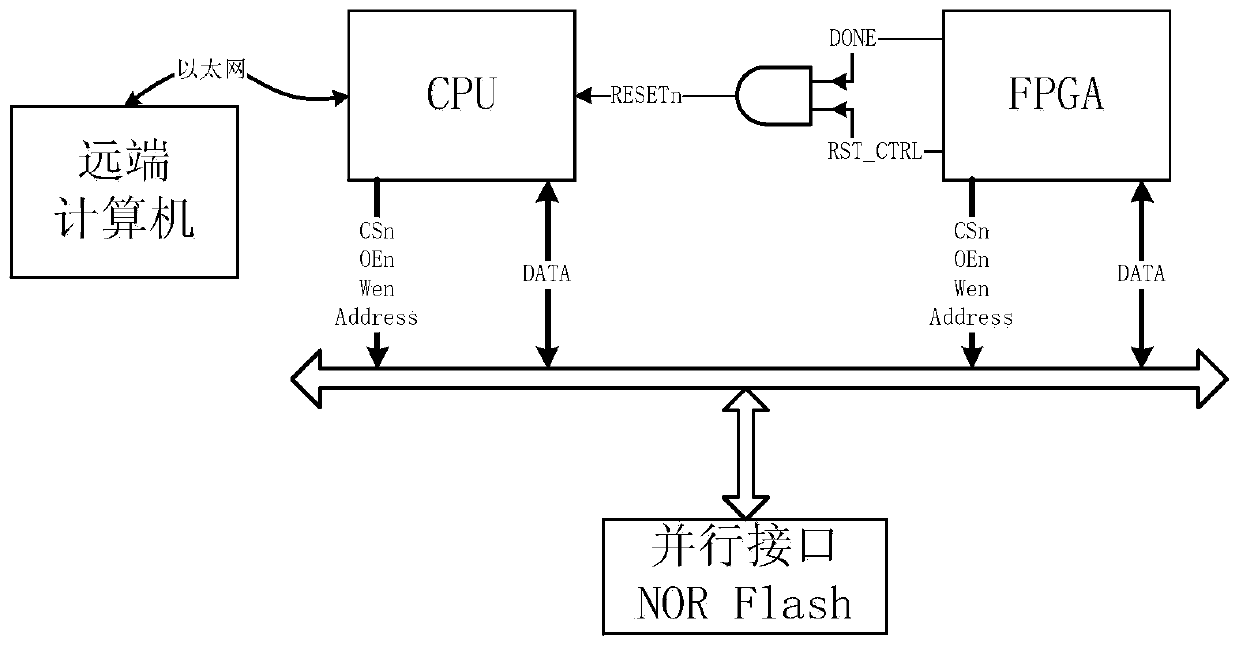

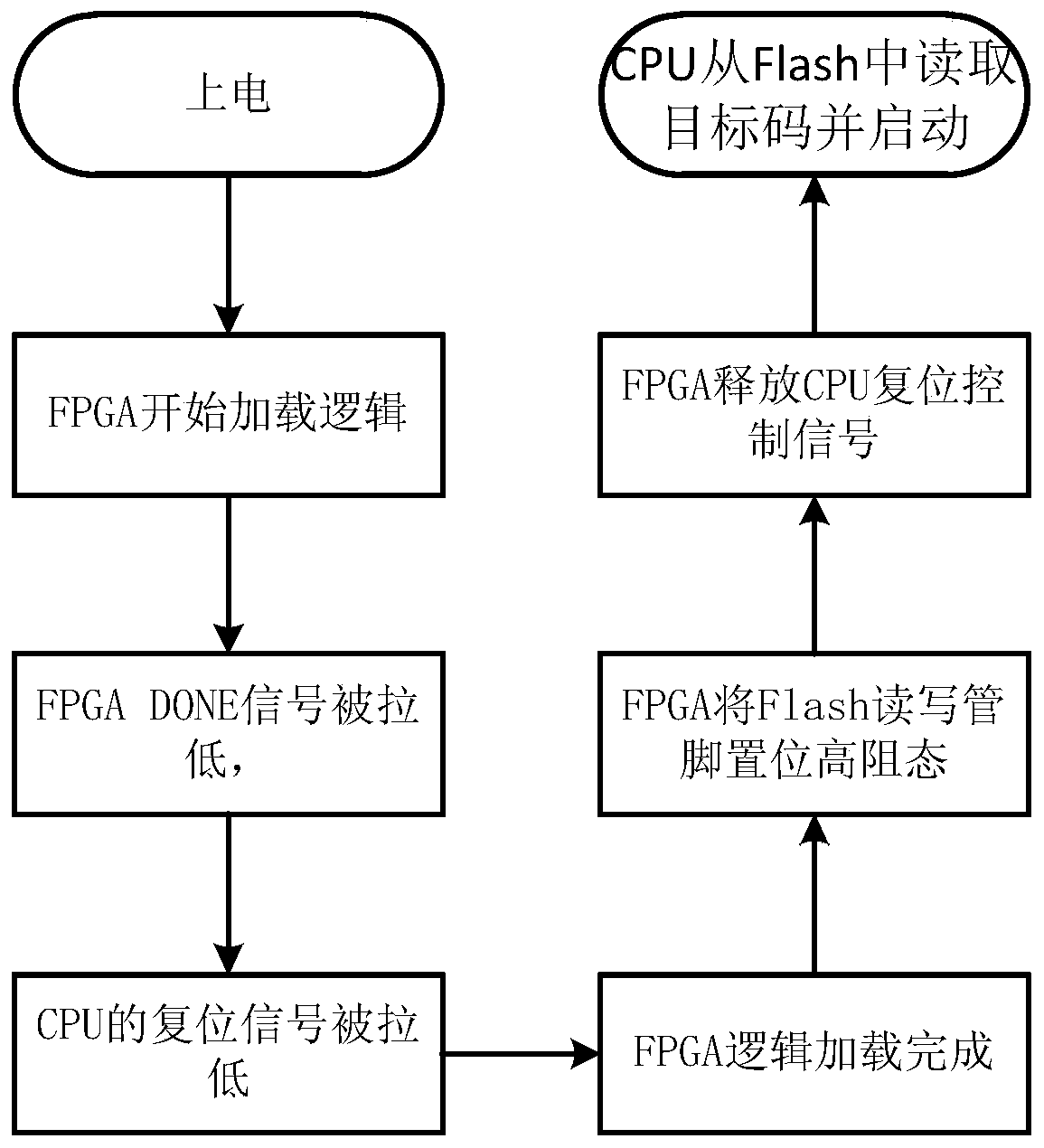

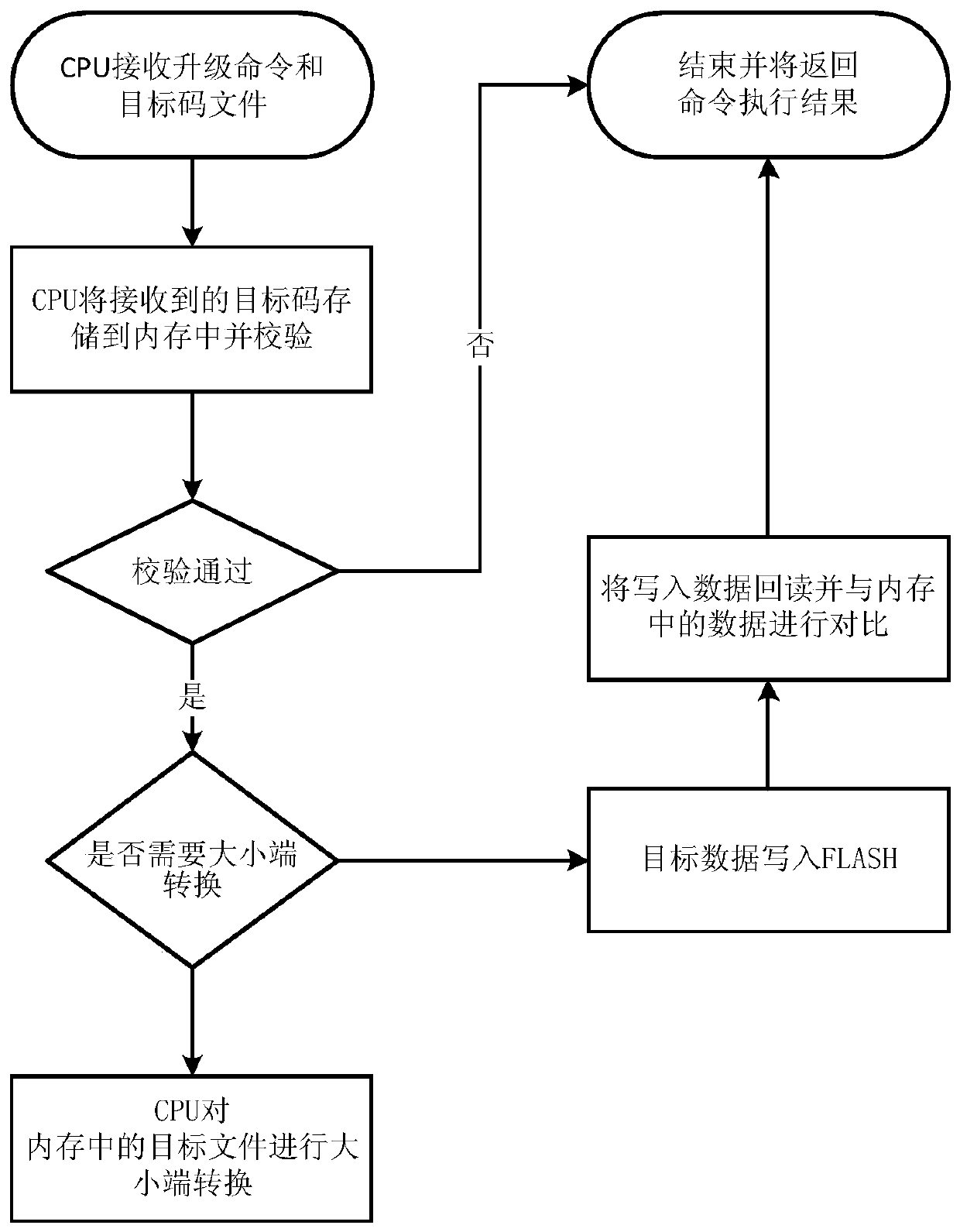

Remote online upgrading method for embedded system containing CPU and FPGA

ActiveCN111026427AExtend your lifeReduce the number of erasuresSoftware engineeringComputer architectureLookup table

The invention relates to a remote online upgrading method for an embedded system containing a CPU and an FPGA. The CPU (which can be a general CPU, a DSP, an MCU and the like) directly or indirectly share Flash with the FPGA, and an operating system and application software running on the CPU, logic and a lookup table running on the FPGA and the like are all stored in the Flash; the FPGA ensures that the access to the Flash is not conflicted by controlling the reset state of the CPU; and after the FPGA finishes logic loading, the FPGA delivers the access permission of the Flash to the CPU, andthe CPU realizes online upgrading of the FPGA through direct access to the Flash. By utilizing the method and the system, on the basis of realizing remote online upgrading, upgrading interfaces of application software / logic can be unified, and the upgrading complexity of the system is reduced while the reliability and the upgrading speed are both considered.

Owner:LUOYANG INST OF ELECTRO OPTICAL EQUIP OF AVIC

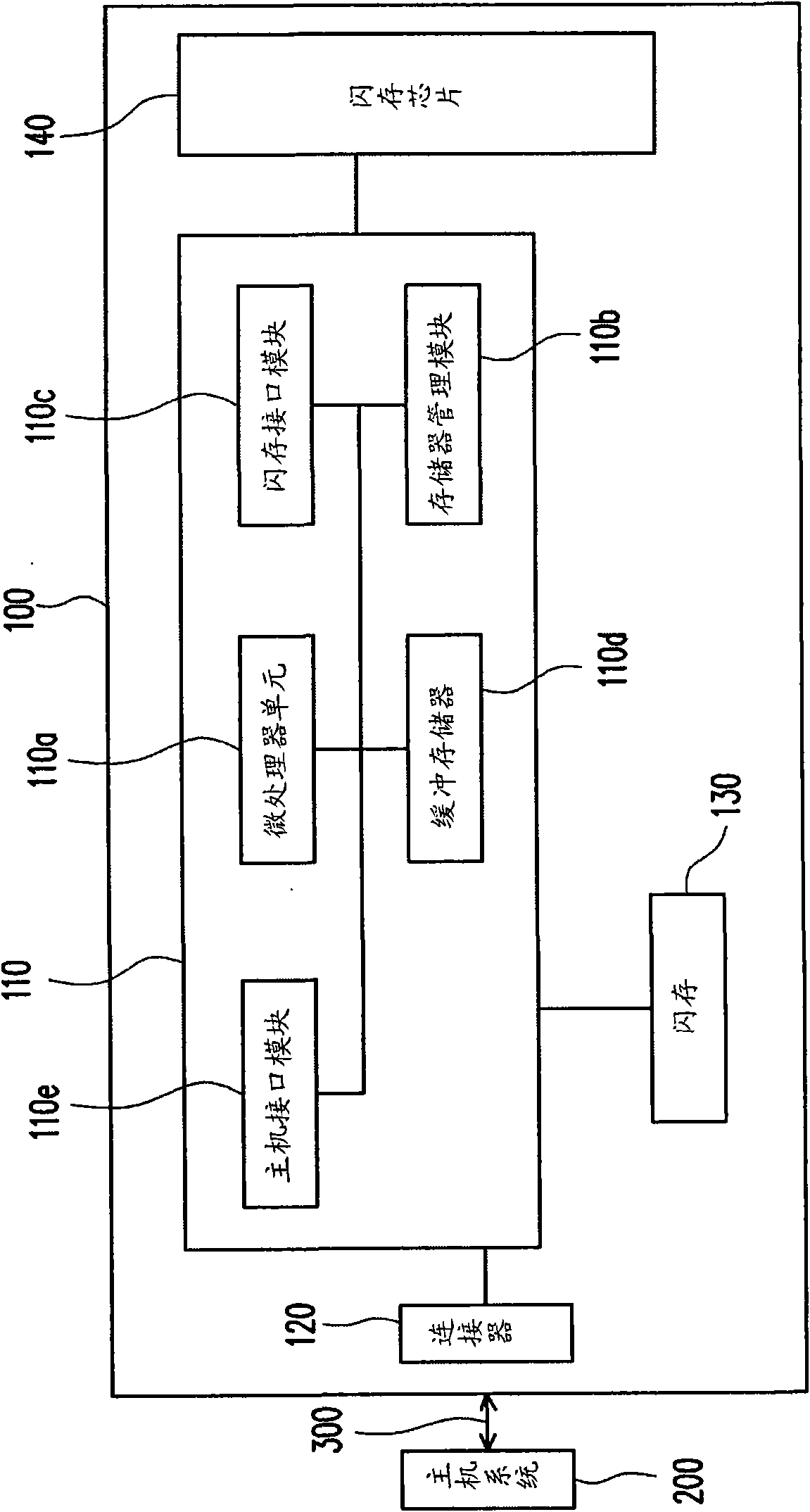

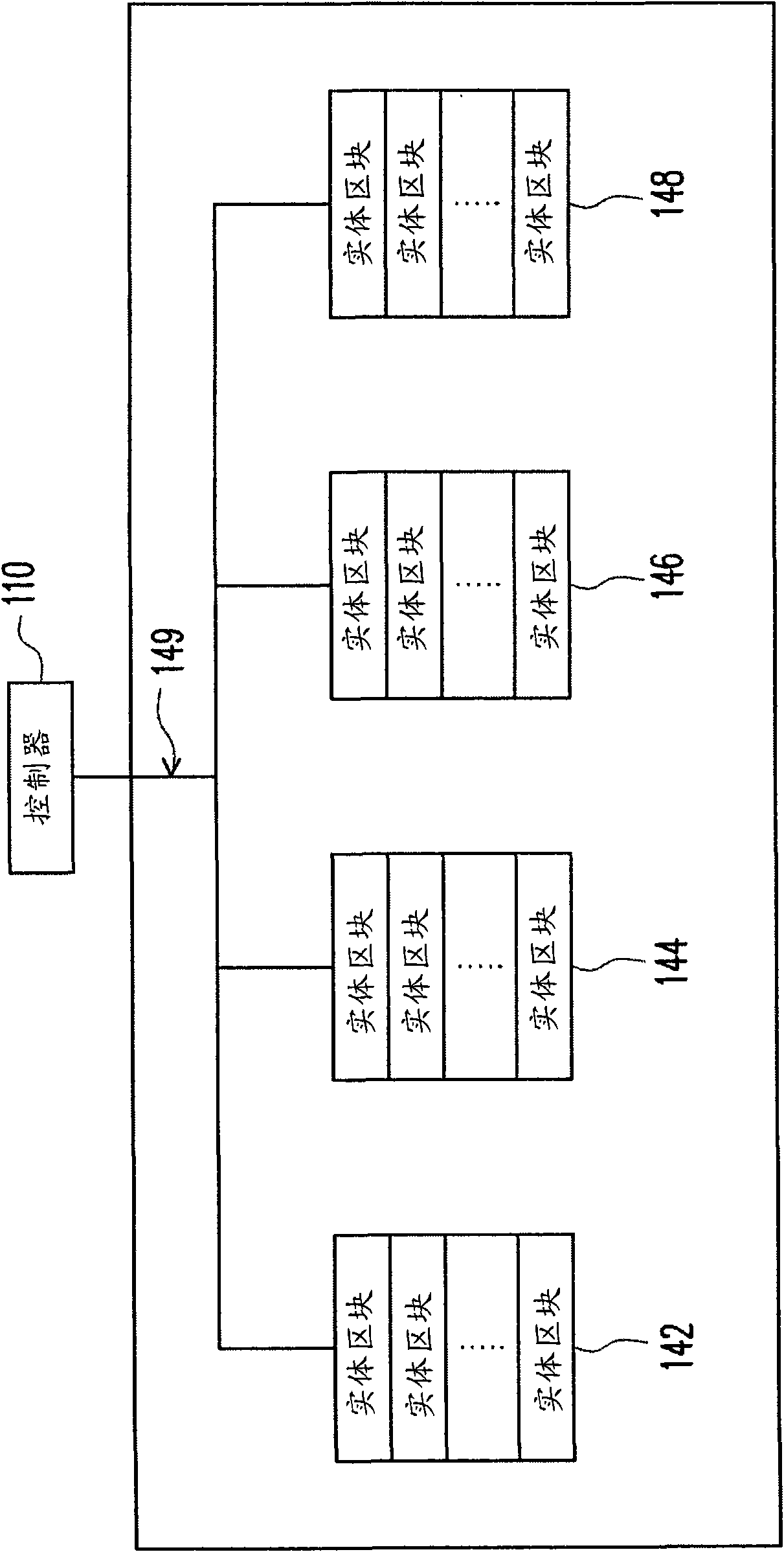

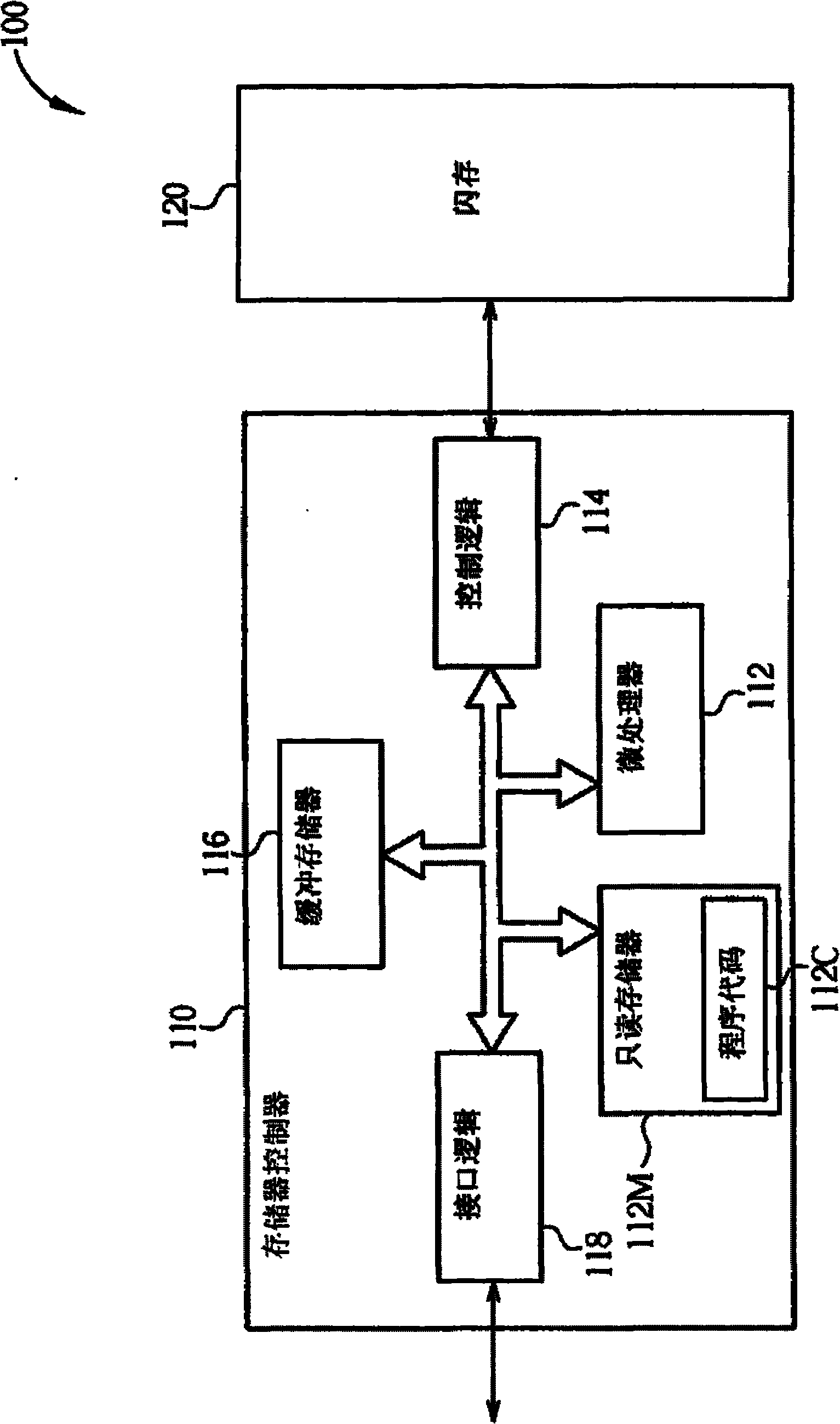

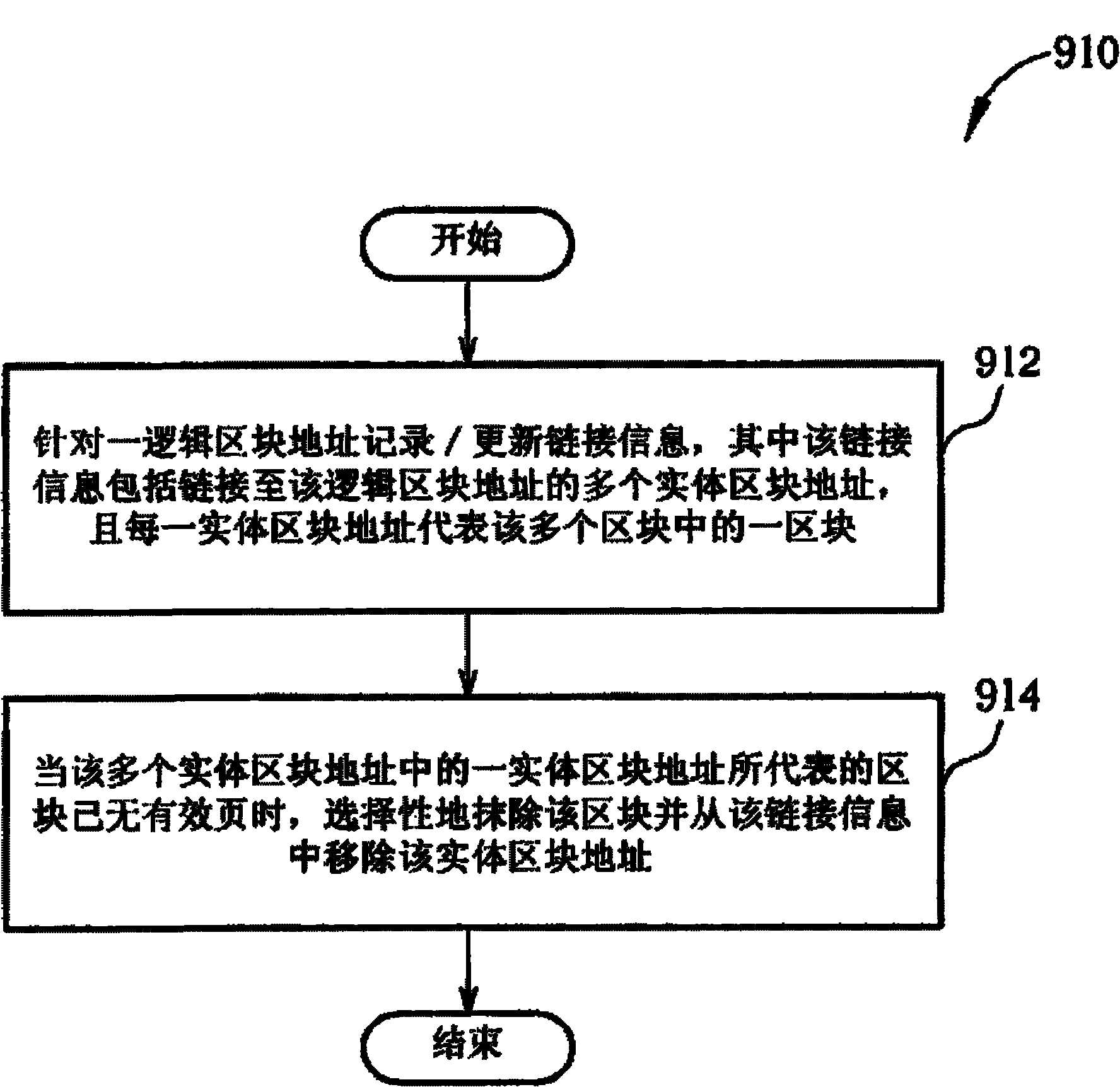

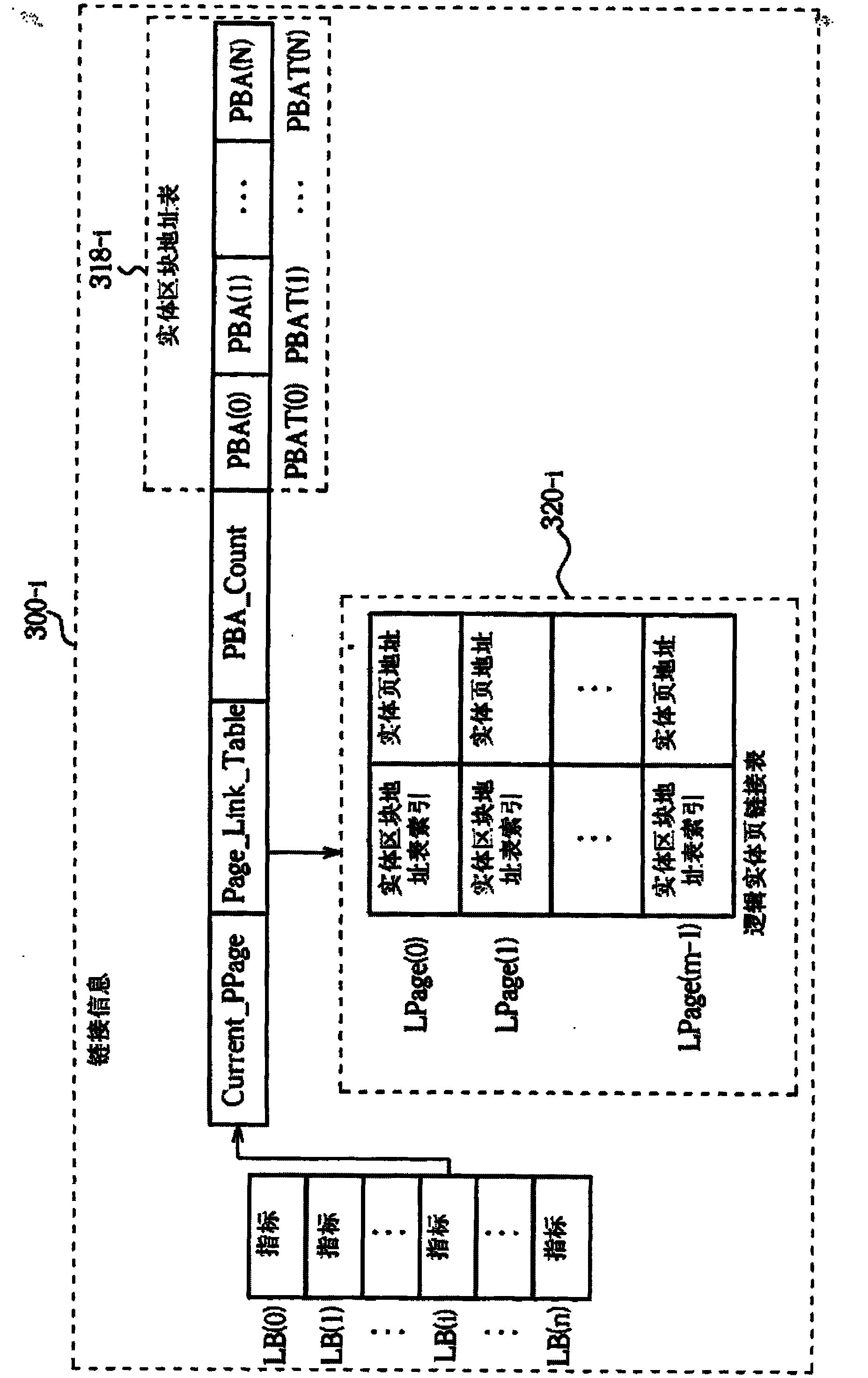

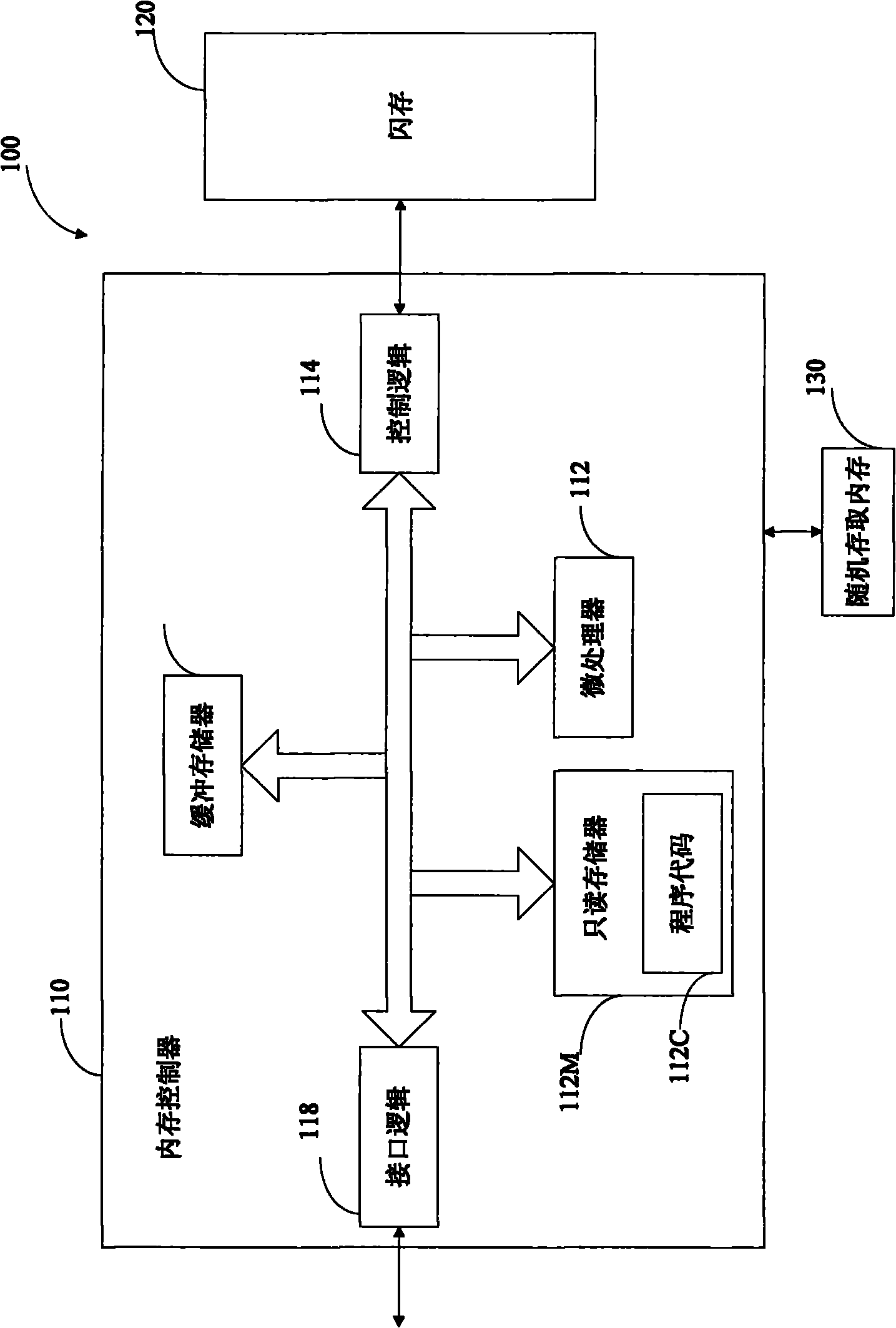

Method for managing plurality of blocks of flash memory and relevant memory device and controller thereof

ActiveCN102033812AReduce the number of merge operationsImprove operational efficiencyMemory adressing/allocation/relocationRead-only memoryLogical block addressing

The invention provides a method for managing a plurality of blocks of a flash memory and a relevant memory device and a controller thereof. The method comprises the following steps of: recording / updating link information for a logic block address, wherein the link information comprises a plurality of physical block addresses which are linked to the logic block address and each physical block address represents one of the plurality of blocks; and when a block represented by one of the plurality of physical block addresses does not contain any active page, selectively erasing the block and removing the physical block address from the link information. The invention also provides a relevant memory device and a controller thereof. The controller comprises a read-only memory which is used for storing a program code and a microprocessor which is used for executing the program code so as to access the flash memory and manage the plurality of blocks.

Owner:SILICON MOTION TECH CORP

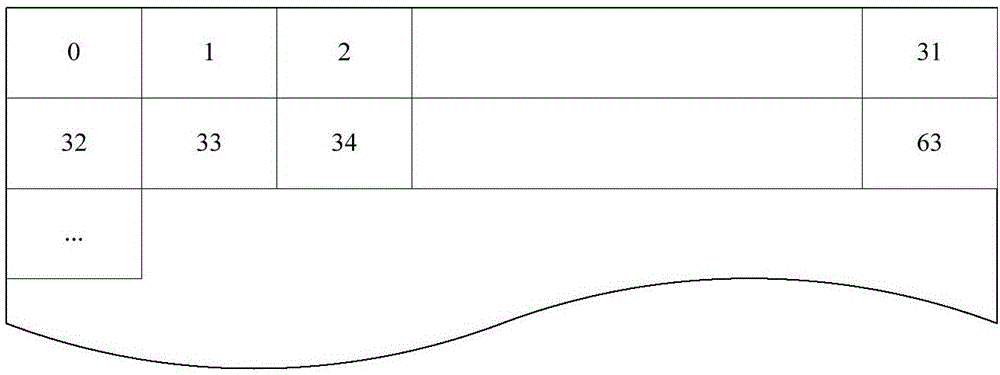

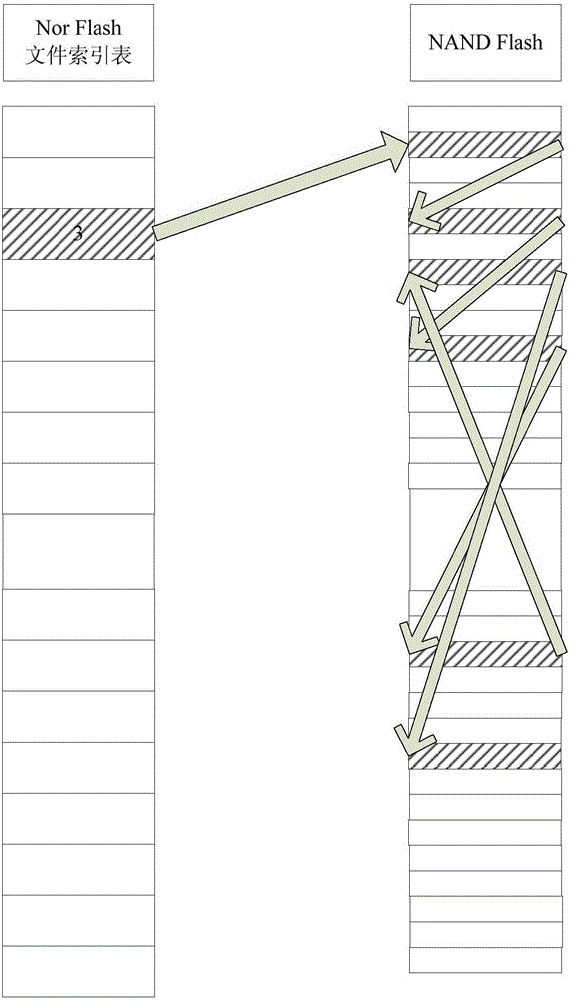

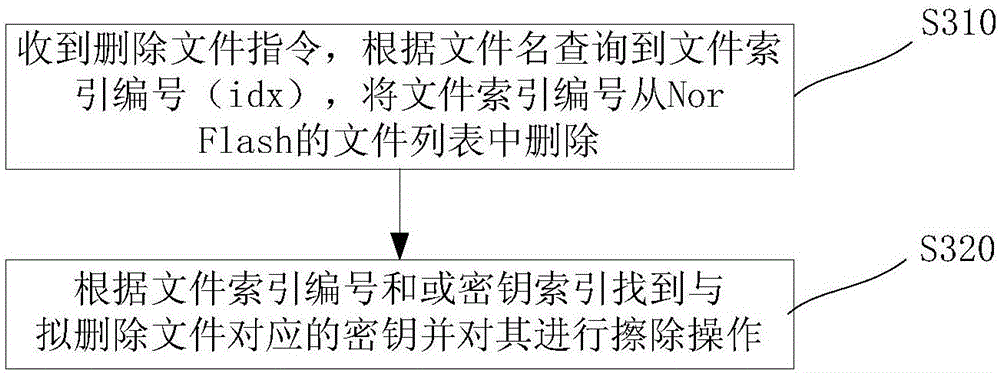

File storage method and safe deletion method of encryption card

InactiveCN106775448AReduce the number of erasuresReduce wear rateInput/output to record carriersDigital data protectionHardware structureSafe storage

The invention relates to the field of flash memory and provides a file storage method of an encryption card. The encryption card comprises NOR Flash and NAND Flash. The storage method comprises steps as follows: large-volume sensitive information is stored in the NAND Flash; auxiliary NAND Flash management information comprising a key corresponding to a file stored in the NAND Flash is stored in the NOR Flash. The safe storage method is realized on an existing encryption card platform, modification of the hardware structure of the existing encryption card is not required, an interface of the existing encryption card can be used, the characteristics of the NAND Flash and the NOR Flash are fully used, the frequency of NAND Flash erasing is greatly reduced, and the wear rate is decreased while the efficiency is improved.

Owner:AEROSPACE INFORMATION

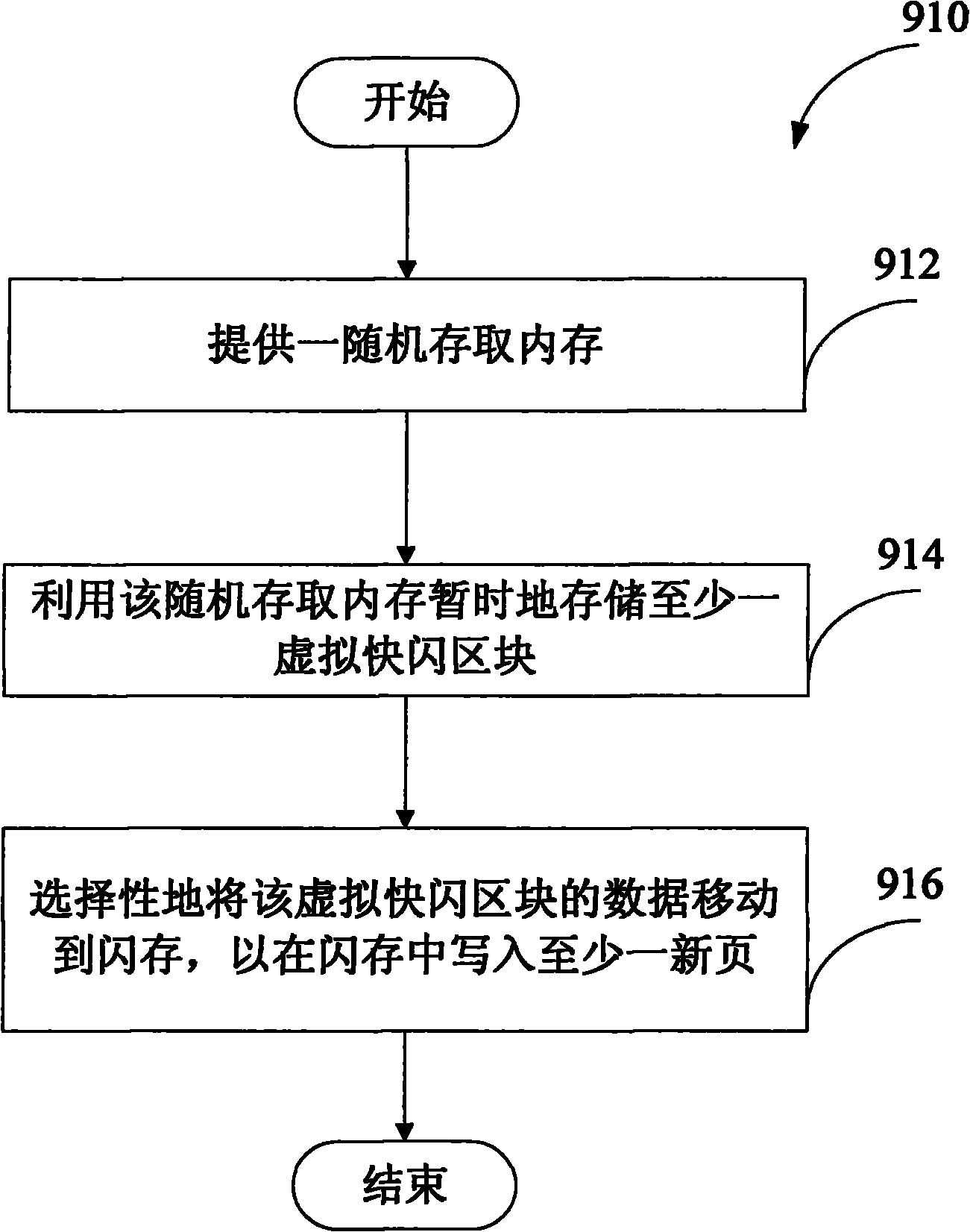

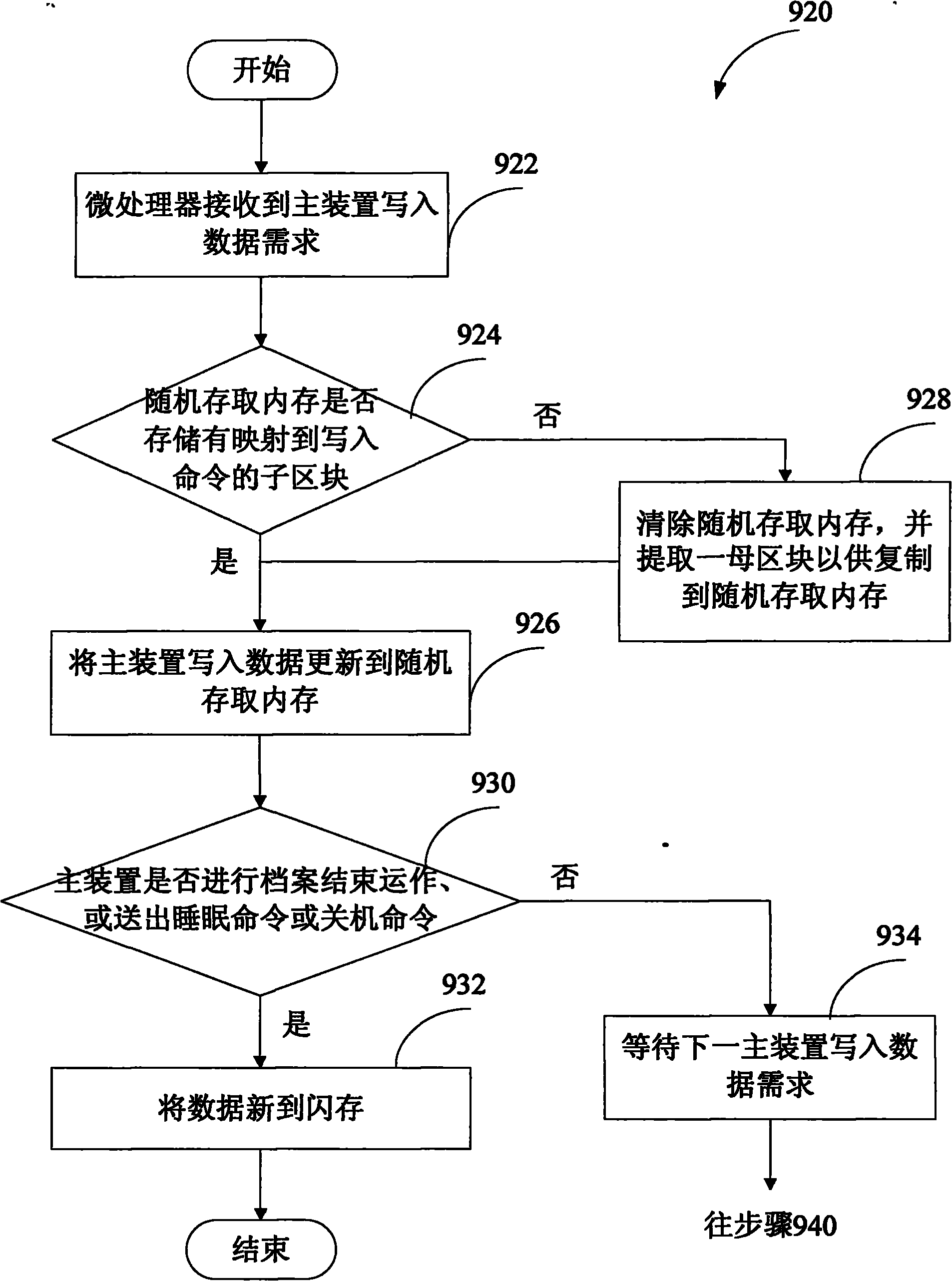

Access method for flash memory, portable memory device and controller thereof

ActiveCN101968971AAccess maintenanceExtended service lifeRead-only memoriesAccess methodRandom access memory

The invention provides a method for enhancing the efficiency of a flash memory, which comprises the following steps of: providing a random access memory; storing at least one virtual flash block temporarily by utilizing the random access memory; and transferring data of the virtual flash block to the flash memory selectively to write at least one new page in the flash memory. The invention also provides a relevant portable memory device and a controller thereof. The controller comprises a read-only memory for storing a program code and a microprocessor for executing the program code to control the access of the flash memory. The controller for executing the program code through the microprocessor transfers the data of the virtual flash block to the flash memory selectively so as to write at least one new page in the flash memory.

Owner:慧荣科技(深圳)有限公司 +1

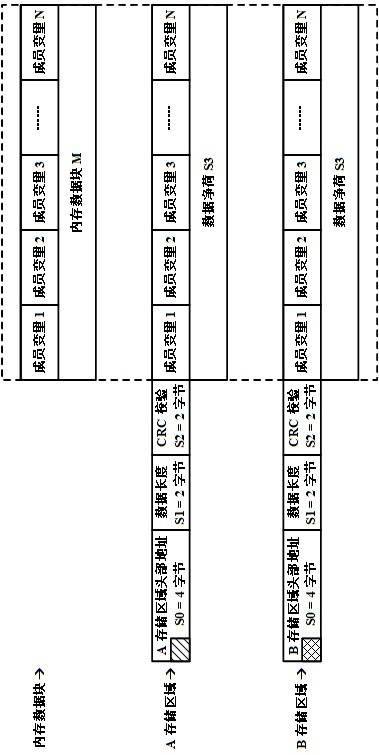

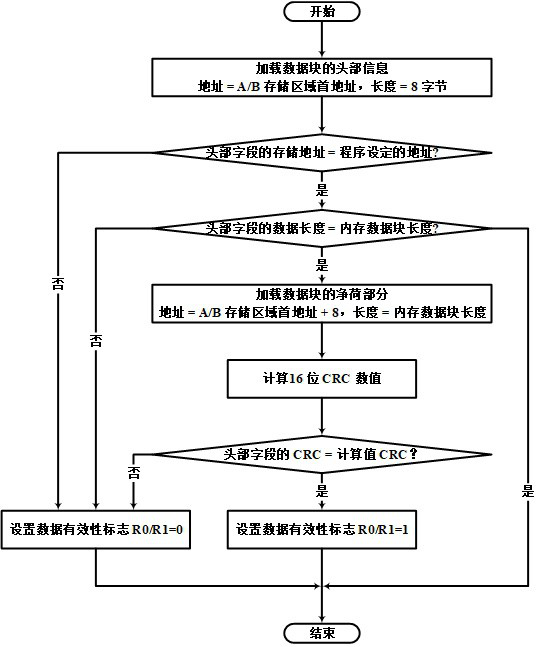

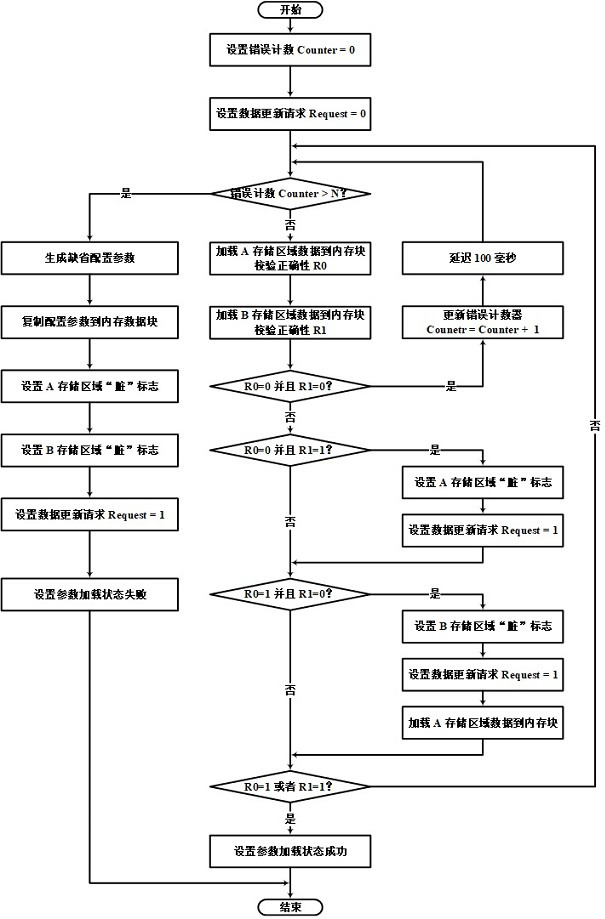

Parameter storage mechanism of embedded system

PendingCN112596808AReduce the number of erasuresExtended service lifeInput/output to record carriersProgram loading/initiatingAbstraction layerParallel computing

The invention discloses a parameter storage mechanism of an embedded system. The parameter storage mechanism comprises an abstraction layer interface, read-write integrity, real-time performance, repeated write-in filtering and default parameter automatic generation. According to the parameter storage mechanism in claim 1, the parameter storage mechanism is characterized in that: 1) a group of configuration parameters are placed in a structured memory block with continuous addresses, and an application program directly accesses member variables in the memory block when reading and writing theconfiguration parameters, so that the problem of real-time performance is solved; 2) two storage areas with non-overlapping addresses are specified on the storage medium, and the memory block is mapped to the two storage areas on the storage medium through a control head with a CRC check field; 3) data is loaded from the storage medium to the memory block only when the system is initialized, and only one-way writing from the memory block to the storage medium is executed in a system main cycle, and 4) data writing takes the storage area as a unit, and one storage area is always in a backup state, so that the reliability problem is solved.

Owner:微网智控(北京)科技有限公司

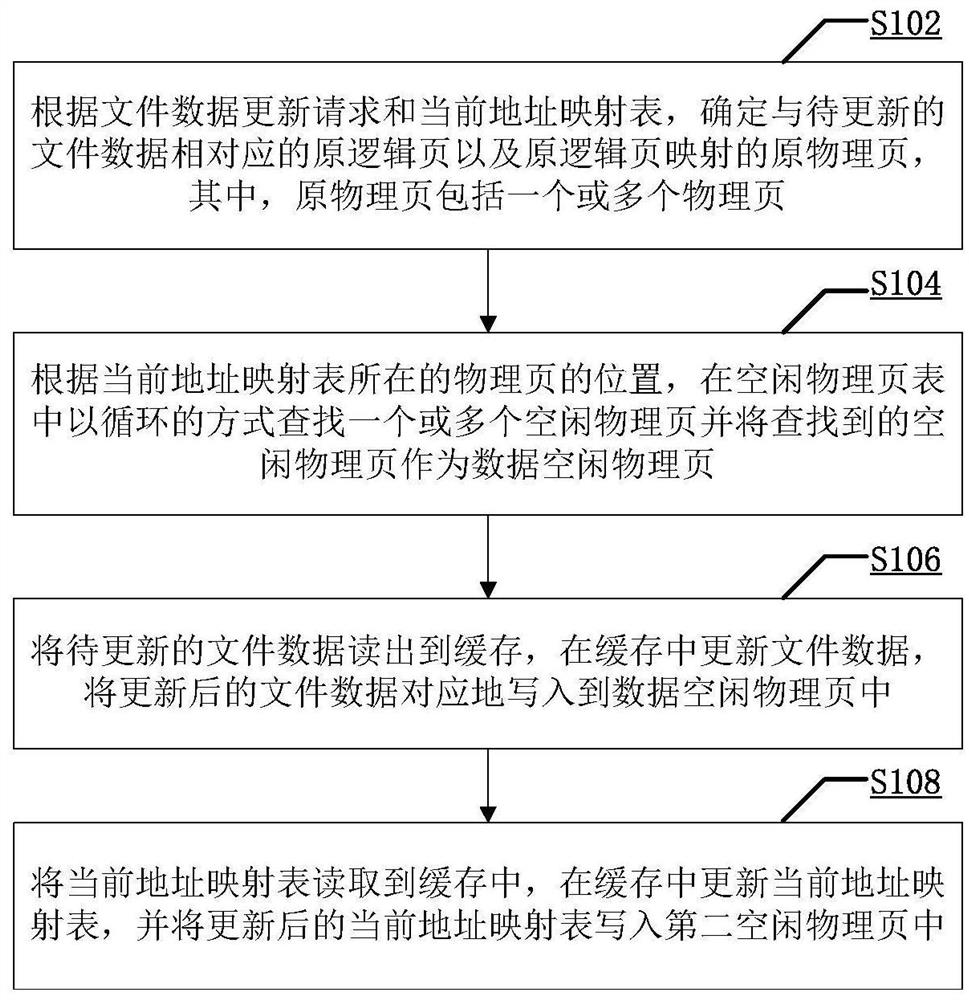

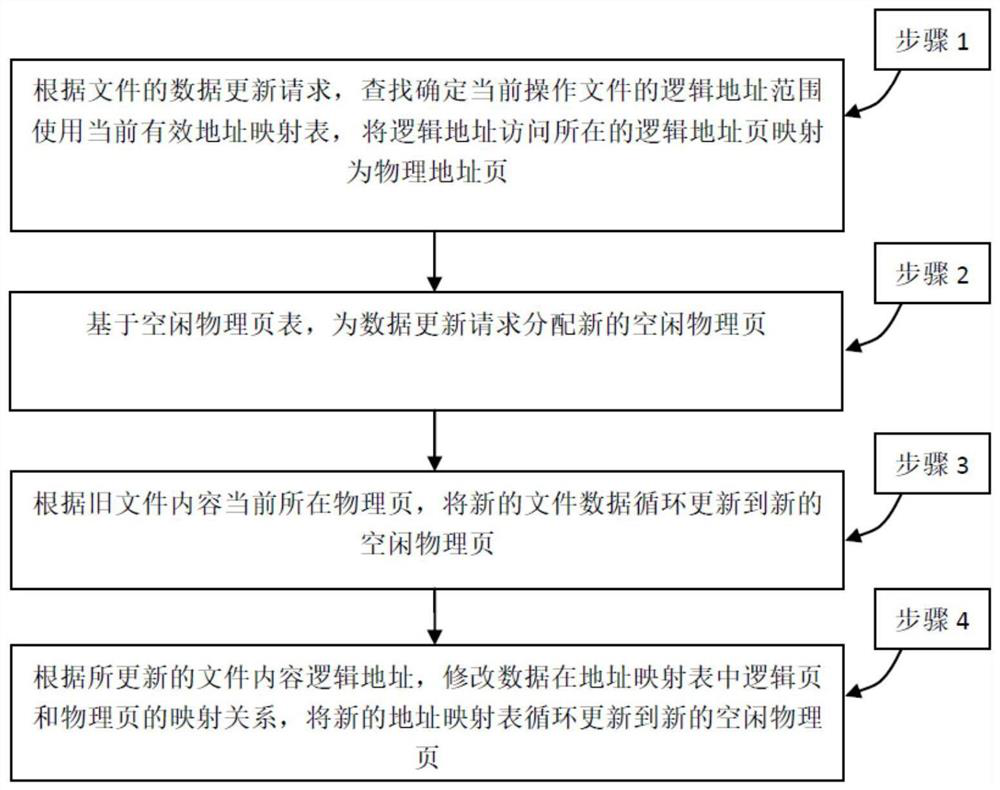

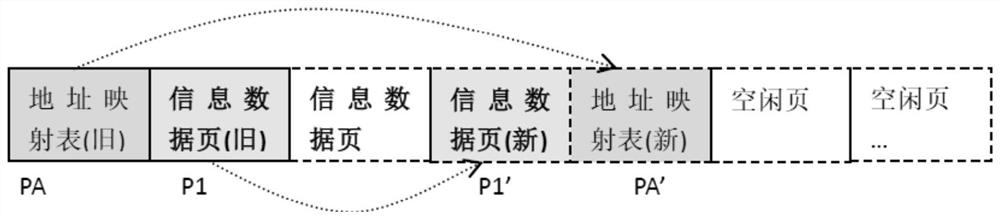

Data updating method and device of Flash memory

PendingCN112597072AImprove the erasing and writing lifeReduce the number of erasuresInput/output to record carriersMemory adressing/allocation/relocationSoftware engineeringPage table

The invention relates to a data updating method and device of a Flash memory, belongs to the technical field of data processing, and solves the problem that in the prior art, data storage and erasingare difficult to ensure the application requirement of long service life. The method comprises the steps of determining an original logic page corresponding to to-be-updated file data and an originalphysical page mapped by the original logic page according to a file data updating request and a current address mapping table; according to the position of the physical page where the current addressmapping table is located, one or more idle physical pages are searched in the idle physical page table in a circulating mode and serve as data idle physical pages; reading the to-be-updated file datato a cache, updating the file data in the cache, and correspondingly writing the updated file data into a data idle physical page; reading the current address mapping table into the cache, updating the current address mapping table in the cache, and writing the updated current address mapping table into the second idle physical page. The updating method can meet the application requirement of longservice life.

Owner:BEIJING HUAHONG INTEGRATED CIRCUIT DESIGN

Data storage method of flash memory

ActiveCN101206617AReduce relocationReduce the number of erasuresMemory adressing/allocation/relocationSpecial data processing applicationsComputer scienceData store

The present invention discloses a flash memory data storage method, comprising the following steps of setting at least one swap block, setting a corresponding structural body for each swap block, writing data into the swap block, assigning a value to the structural body of the swap block, performing data relocation according to the structural body value of at least one swap block, and resetting the value of each structural body. Through the method of the present invention, after data is written into the swap block, data relocation is not performed immediately but performed uniformly according to the structural bodies of the swap blocks after all data of the writing operation at a time is written into the appropriate swap blocks. Therefore, the method of the present invention decreases data relocation frequency so as to improve data storage speed. Meanwhile, as the erasing times of flash memory are reduced, the life span of the flash memory is prolonged.

Owner:NETAK TECH KO LTD

Memory space self-adaptive allocation method of memory

PendingCN111061649AImprove compatibilityImplement Adaptive DetectionMemory adressing/allocation/relocationEnergy efficient computingMicrocontrollerMemory chip

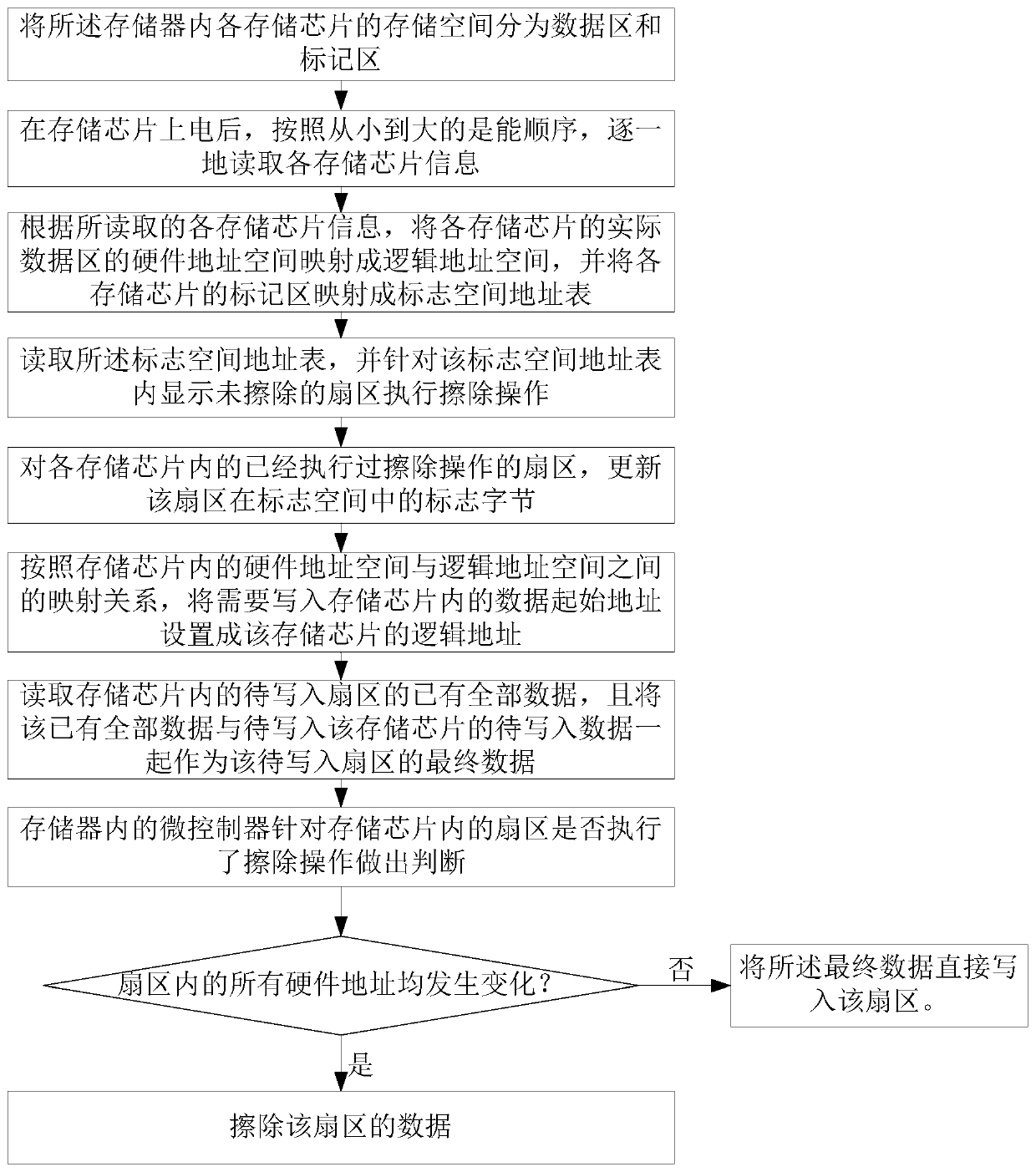

The invention relates to a memory space self-adaptive allocation method of a memory. The method comprises the following steps of: dividing all sectors of each memory chip in a memory into a data areaand a mark area, reading information of each memory chip one by one, mapping a hardware address space of an actual data area of each memory chip into a logic address space, and mapping the mark area of each memory chip into a mark space address table; executing an erase operation on the sectors which are displayed to be not erased, and updating mark bytes of the sectors in the mark space for the sectors which are already subjected to the erase operation in each storage chip; setting a data initial address needing to be written into the storage chip as a logic address of the storage chip; taking all the existing data of the to-be-written sector and the to-be-written data as final data of the to-be-written sector; erasing sector data or directly writing final data into a sector by a microcontroller according to whether the sector in the storage chip executes erasing operation, repeated erasing of the storage chip is avoided, and the service life of the memory is prolonged.

Owner:NINGBO SANXING INTELLIGENT ELECTRIC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com