fc link elastic buffer circuit

A buffer and circuit technology, applied in the computer field, can solve the problems affecting the communication function and performance of the system, data receiving buffer overflow, data loss, etc., to achieve the effect of small resource occupancy, easy implementation, and rapid integration

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

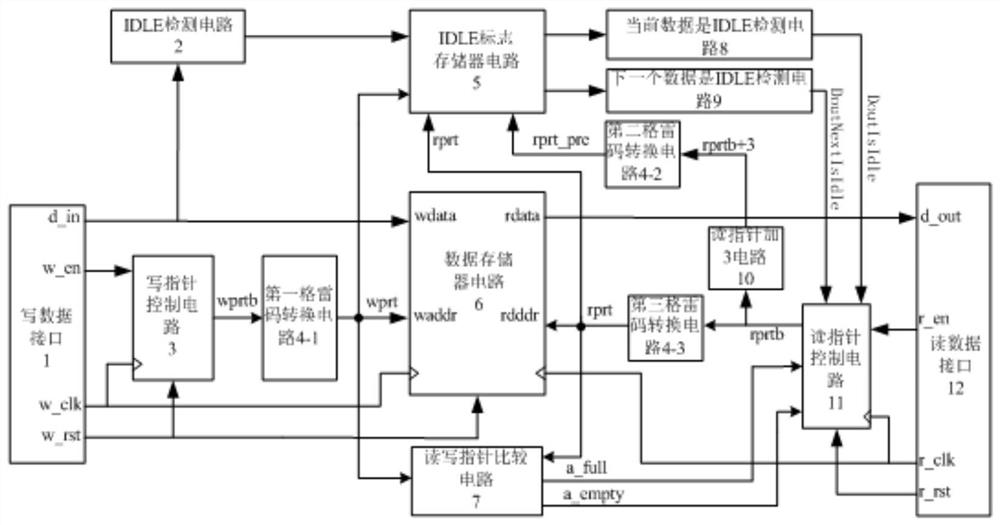

[0040] The technical solution of the present invention is further described below in conjunction with the accompanying drawings and specific embodiments, please refer to figure 1 .

[0041] The present invention provides an FC link elastic buffer circuit, comprising a write data interface 1, an IDLE detection circuit 2, a write pointer control circuit 3, a first Gray code conversion circuit 4-1, a first Gray code conversion circuit 4-2, First gray code conversion circuit 4-3, IDLE flag memory circuit 5, data memory circuit 6, read and write pointer comparison circuit 7, current data is IDLE detection circuit 8, next data is IDLE detection circuit 9, read pointer plus 3 circuits 10. Read pointer control circuit 11, read data interface 12,

[0042] Among them, write data interface 1, IDLE detection circuit 2, write pointer control circuit 3, first Gray code conversion circuit 4-1, IDLE flag memory circuit 5, and data memory circuit 6. After completing the write clock domain, wr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com