Integer and half-integer frequency divider based on characteristic state feedback

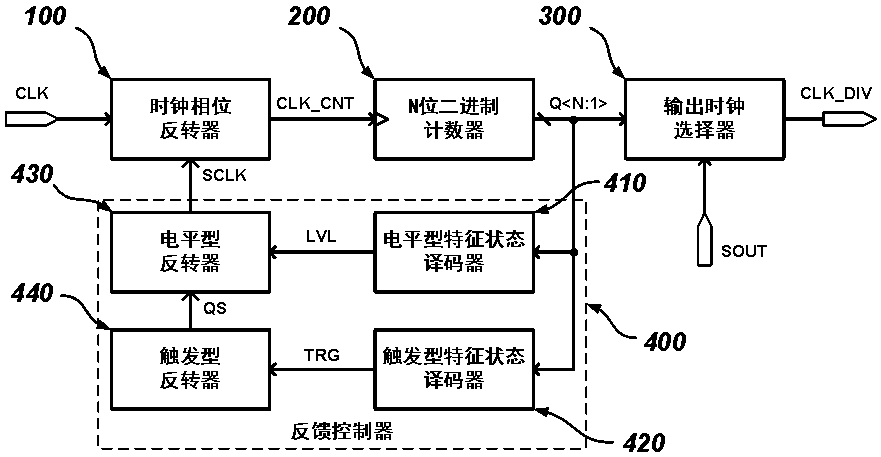

A characteristic state and frequency divider technology, applied in counting chain pulse counters, pulse counters, electrical components, etc., can solve the problems of non-universal, complex circuit structure, incomplete frequency division coefficient, etc., and achieve simple design and strong versatility Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

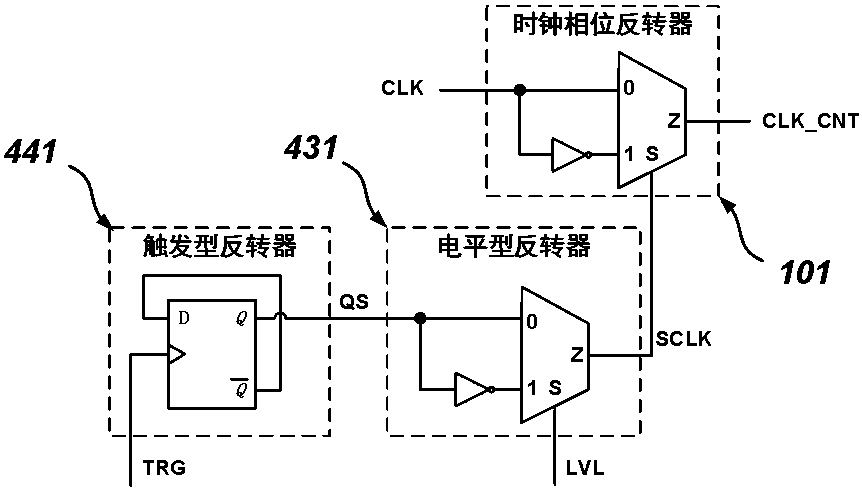

Method used

Image

Examples

Embodiment approach

[0042] (1) Substituting M=5 into relational formula 1, n=3 can be obtained, that is, the sub-state bit width is 3 bits, and correspondingly select Q as the frequency division clock output CLK_DIV;

[0043] (2) Substituting M=5 and n=3 into relational formula 2, we can get:

[0044]

[0045] (3) When the duty ratio of the input clock to be divided is 50%, in order to realize equal duty ratio frequency, substituting D=50%, M=5 and n=3 into relational formula 3, we can get:

[0046]

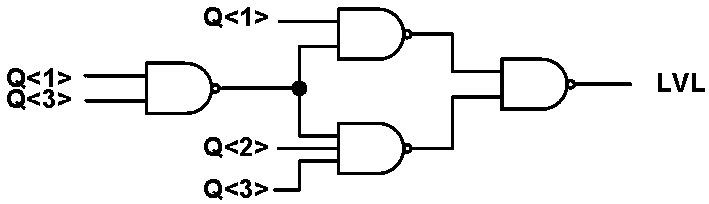

[0047] (4) Therefore, K=3 and H=0 are desirable, where: K 0 =K 1 =K X =1,H 0 =H 1 =0; Correspondingly, Q=001, 110, 011 can be respectively selected for the level-type characteristic states. Therefore, the possible logic circuit of the level-type state decoder is as follows image 3 As shown; since the frequency division factor is H=0, the output (TRG) of the trigger decoder can be a fixed level, such as Figure 4 shown can be directly connected to logic "0".

[00...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More