Reducing read disturb in memory device during signal switching transients

A memory cell, unselected technology, applied in the field of operation of memory devices

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

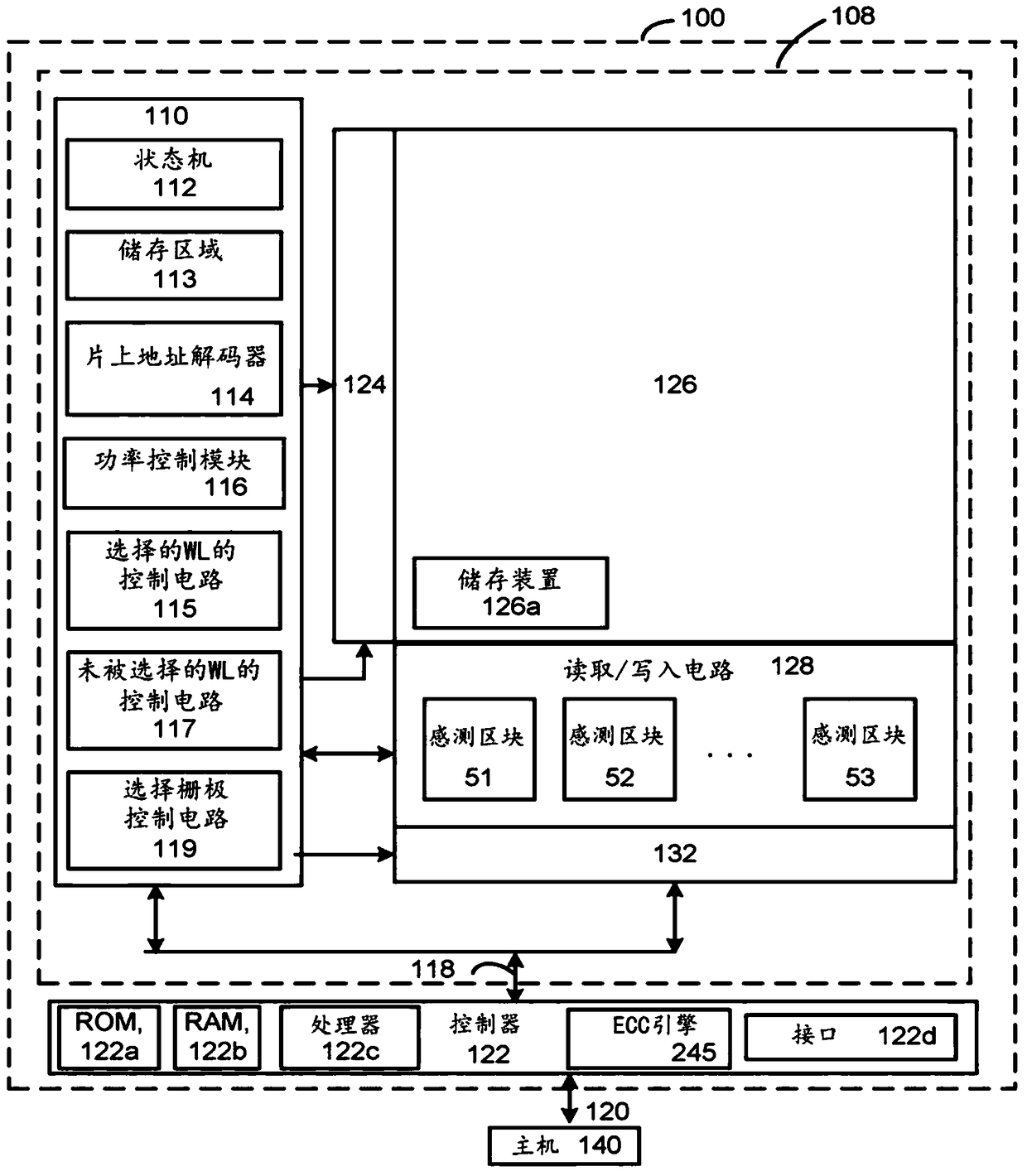

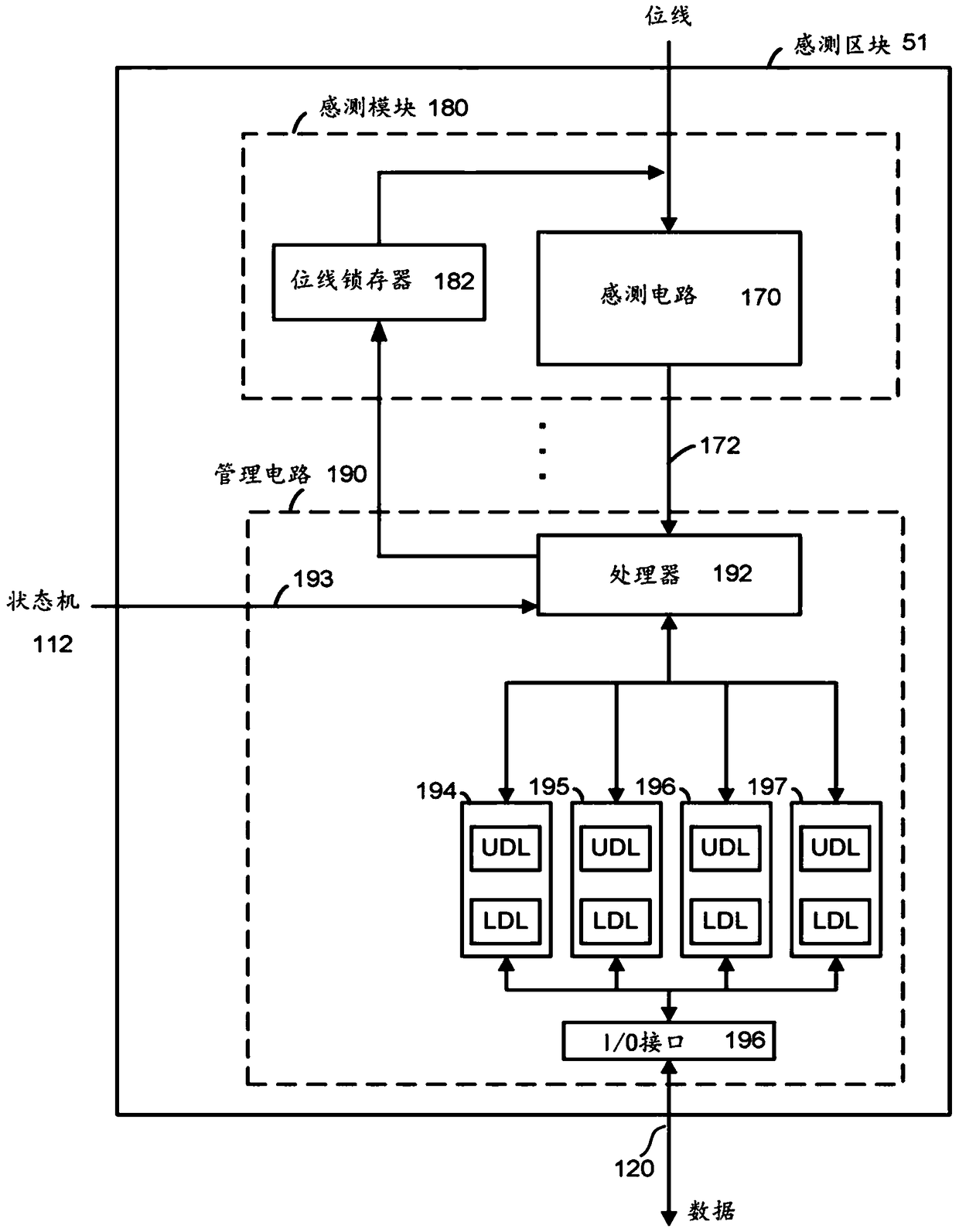

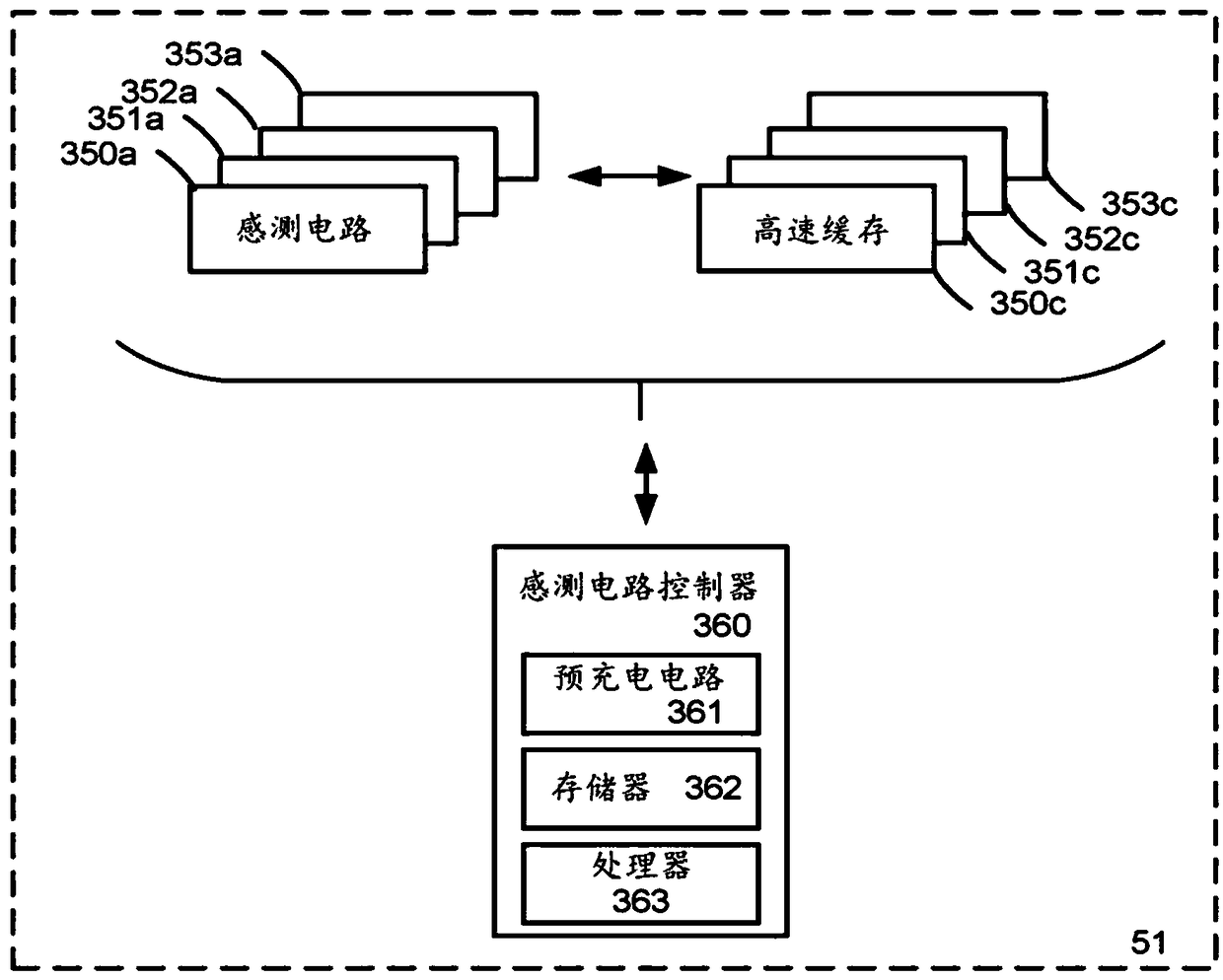

[0044] An apparatus and technique are described for reducing read disturb in a memory device.

[0045] In some memory devices, such as in NAND strings in blocks or sub-blocks, memory cells are connected to each other. Each NAND string consists of several memory cells connected in series between one or more select gate (SG) transistors on the drain side (referred to as SGD transistors) and one or more source-terminal SG transistors (referred to as SGS transistors), which One or more drain select gate (SG) transistors are on the drain terminal of the NAND string connected to the bit line, and the one or more source terminal SG transistors are on the source terminal of the NAND string connected to the source line. In addition, the memory cells may be arranged with a common control gate line (eg, a word line) serving as a control gate. A set of word lines extends from the source side of the block to the drain side of the block. The memory cells can be connected in other types of...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More