Integrated circuit layout method and distributed design method

A technology of integrated circuits and layout methods, applied in computing, electrical digital data processing, special data processing applications, etc., can solve problems such as low efficiency, and achieve the effect of efficient layout solutions

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

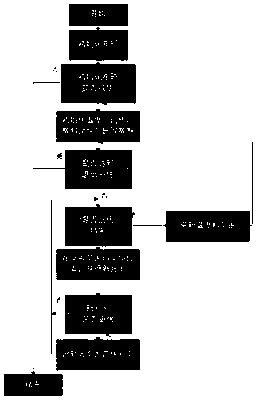

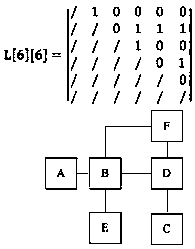

[0061] 1) The server side reads the logical netlist that needs to be laid out, and generates graph G logic (V logic ,E logic ), where the set of vertices V logic Each element in is a layoutable logical unit, which contains information such as the name, type, and constraints of the logical unit. The edge set E logic Contains associations between logical units.

[0062] 2) The server reads the integrated circuit chip model library file and generates graph G device (V device ,E device ), where the set of vertices V device Each element in is an available layout unit, including the name, type, location and other related information of the unit. The edge set E device Contains the association relationship between physical resources. It is initially empty and is constantly modified during the layout process. device .

[0063] 3) The layout is for V logic Each logic cell in is assigned a corresponding V device In the physical unit, at the same time need to consider how to me...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More