A construction method and decoding device of a multi-code-rate ldpc code

A technology of LDPC code and construction method, applied in error detection coding using multi-bit parity bits, generation of response errors, error detection of redundant codes, etc., can solve the problems of waste of storage space and decoding pass rate, etc., Achieve the effect of improving early read and write pass rate, increase service life, and high decoding pass rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

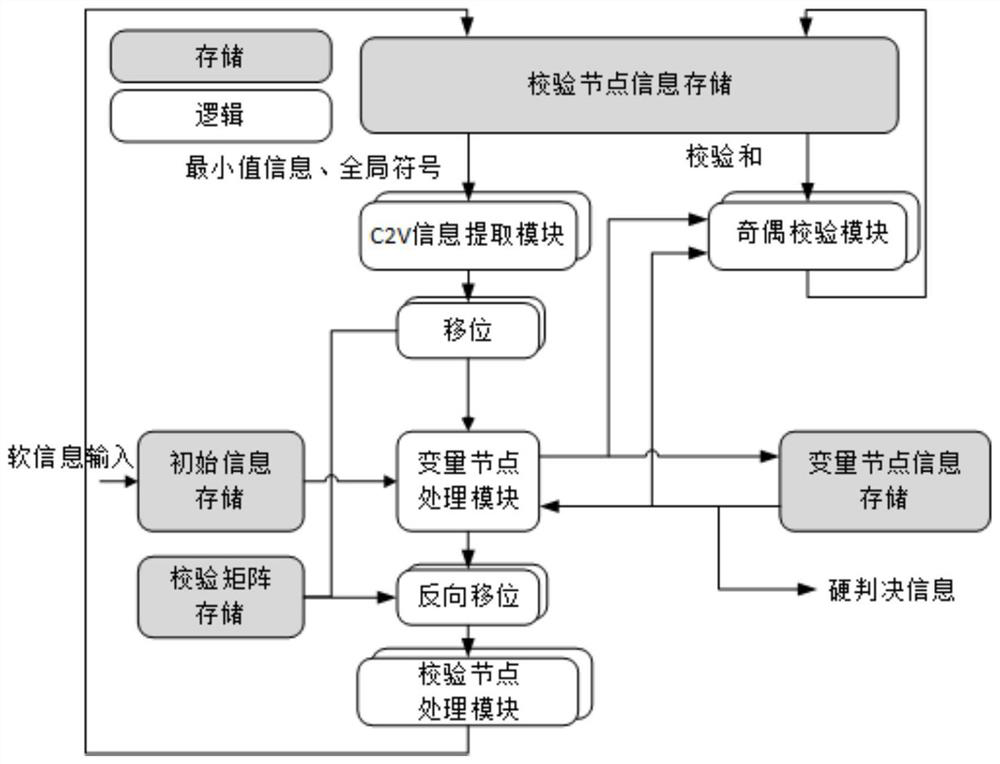

[0041] First of all, the method of the present invention is applicable to flash memory technology, specifically for a construction method of QC-LDPC codes applicable to a multi-code rate of flash memory, specifically as follows:

[0042] (1) Suppose the parity check matrix of the p multi-code rate LDPC codes that want to construct is:

[0043]

[0044] The corresponding QC-LDPC fundamental matrix is as follows:

[0045]

[0046] Check matrix sub-matrix size is Q, then M r =Q×m r ,N r =Q×n r , where r∈{0,1,...p-1} is the code rate parameter.

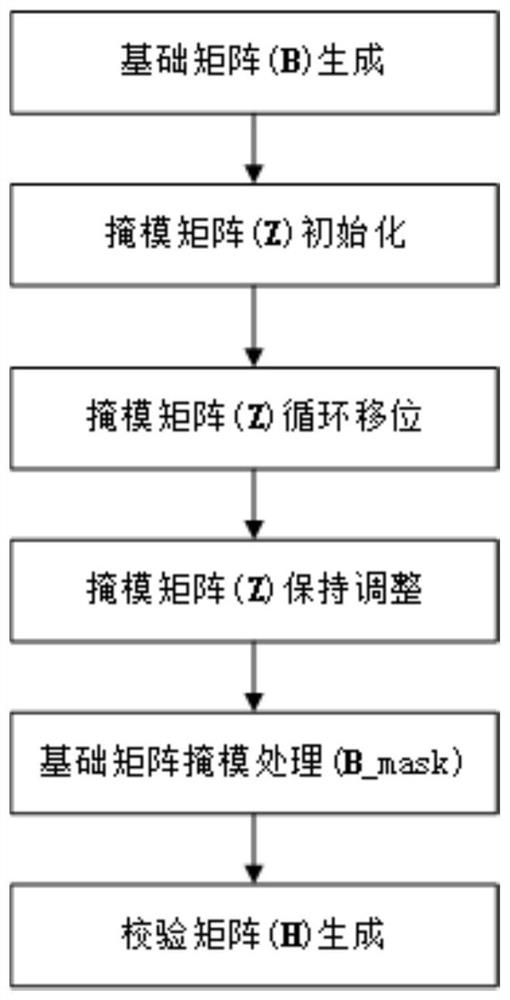

[0047] The construction method is mainly as follows:

[0048] Based on the element {α in the Galois Field GF(q) -∞ ,α 0 ,α 1 ,…,α q-1}, construct p fundamental matrices with different code lengths and different code rates For any one of the basic matrix B m×n The construction; any one of the basic matrix B m×n The construction of the element B in the fundamental matrix m×n =[b kl ] 0≤k<m,0≤l<n are elements in GF(q)...

Embodiment 2

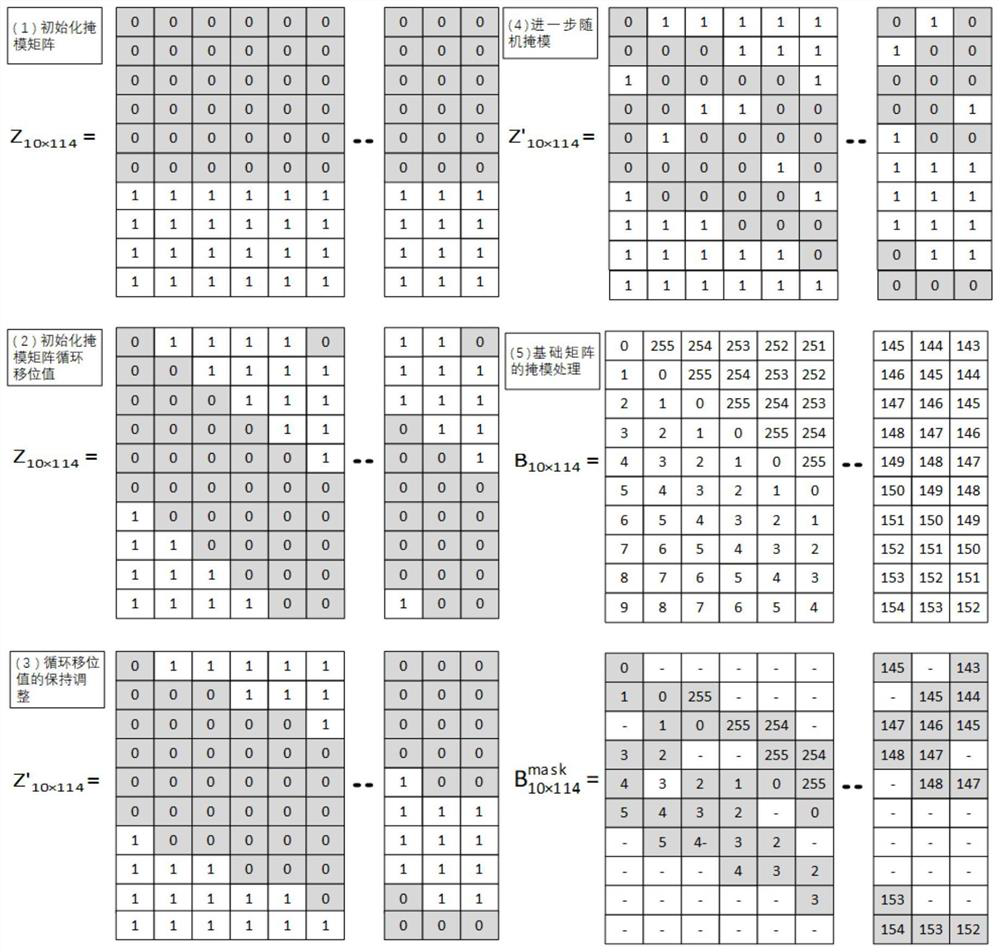

[0073] Firstly, the multi-code rate QC-LDPC built on flash memory has 6 code rates ranging from 0.867 to 0.946, and the information bits are fixed at K=26520. QC-LDPC is constructed based on the Galois field GF(257), and the CPM size Q in the parity check matrix is Q=255.

[0074] Step 1. Construct the fundamental matrix

[0075] Construct the basic matrix B of 6 multi-code rates 16×120 ,B 14×118 ,B 12×116 ,B 10×114 ,B 8×112 ,B 6×110 . In this embodiment, the method of intercepting elements from the Latin square matrix is adopted. in latin phalanx L 256×256 Any column and any row in are composed of different elements in GF(257). in L 256×256 Intercept the first 16 rows and the first 120 columns of elements in the upper left corner to get B 16×120 . Obtain other fundamental matrices in the same way.

[0076] Step 2. Construct a mask matrix.

[0077] The mask matrix of the present invention can make the parity check matrix set of multiple code rates have a unif...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More