A Capacitorless Low Dropout Linear Regulator

A low-dropout linear, capacitor-free technology, applied in the direction of instruments, electric variable adjustment, control/regulation systems, etc., can solve the problems affecting the performance of the circuit system, the deterioration of the power supply rejection ratio, and the deterioration of transient characteristics, etc., to achieve improved Effects of system efficiency, size reduction, and bandwidth expansion

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

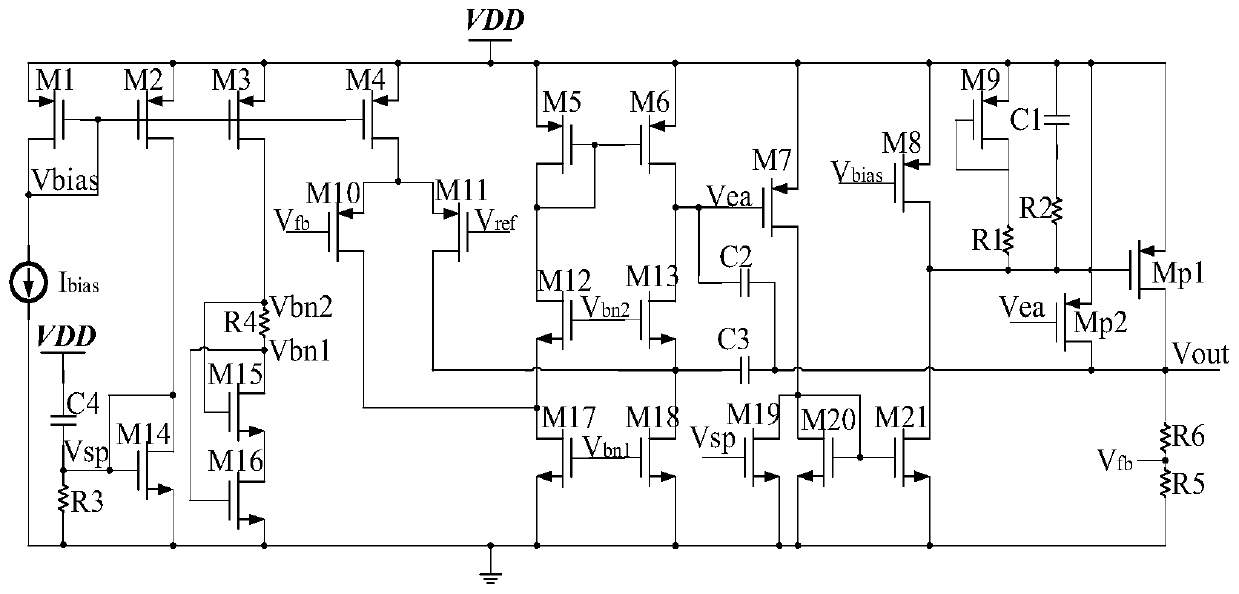

[0040] The technical solutions of the present invention will be described in detail below with reference to the accompanying drawings and specific embodiments.

[0041] A capacitorless low-dropout linear regulator proposed by the present invention includes a bias circuit, an operational amplifier circuit, a compensation circuit, a power tube and a feedback loop, wherein the bias circuit is used to provide a first bias voltage V bn1 , the second bias voltage V bn2 , the third bias voltage Vsp and the first bias current; such as figure 1 An implementation form of the bias circuit is shown, including the eighth PMOS transistor M1, the ninth PMOS transistor M2, the tenth PMOS transistor M3, the eleventh PMOS transistor M4, the ninth NMOS transistor M15, and the tenth NMOS transistor M16 and the fourth resistor R4, the gate and drain of the eighth PMOS transistor M1 are short-circuited and connected to the bias current source Ibias with a fixed current value, and its gate outputs ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More