Algorithm for reducing write-in amplification rate and improving random write-in performance

A random write and magnification technology, applied in computing, instruments, electrical and digital data processing, etc., to slow down FLASH life loss, improve random write speed, and reduce write magnification.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] The preferred embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings, so that the advantages and features of the invention can be more easily understood by those skilled in the art, so as to define the protection scope of the present invention more clearly.

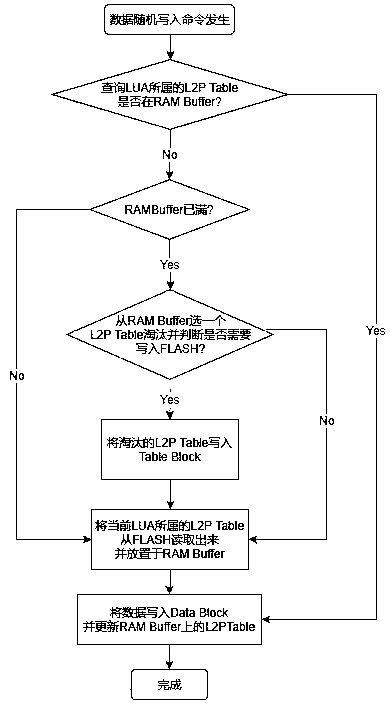

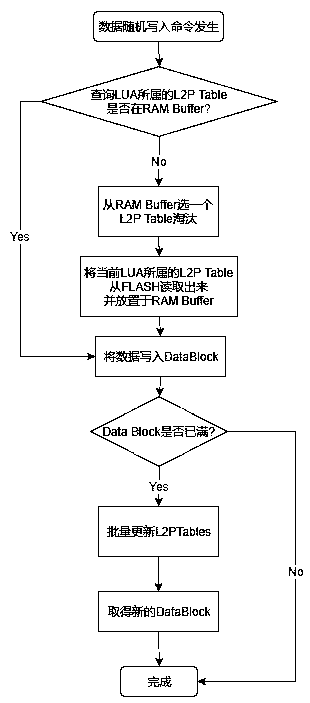

[0022] Such as figure 2 As shown, it is a flow chart of the algorithm for reducing write amplification and improving random write performance of the present invention, including the following steps:

[0023] Step 1, a logical address LBA data random write command occurs;

[0024] Step 2. Query whether the L2P Table to which the LUA belongs is in the RAM Buffer. If it is not in step 3, if it is in step 5;

[0025] Step 3. Select an L2P Table from the RAM Buffer to eliminate;

[0026] Step 4, read from the FLASH from the L2P Table to which the current LUA belongs and place it in the RAM Buffer;

[0027] Step 5. Write data into DateBlock;

[0028] Step...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com