Arrangement method of exposure areas on wafer

A technology for exposure area and wafer, which is applied in microlithography exposure equipment, photolithography process exposure device, optics, etc., can solve the problems of wafer edge defocus and improper arrangement, and avoid the problem of wafer edge defocus Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

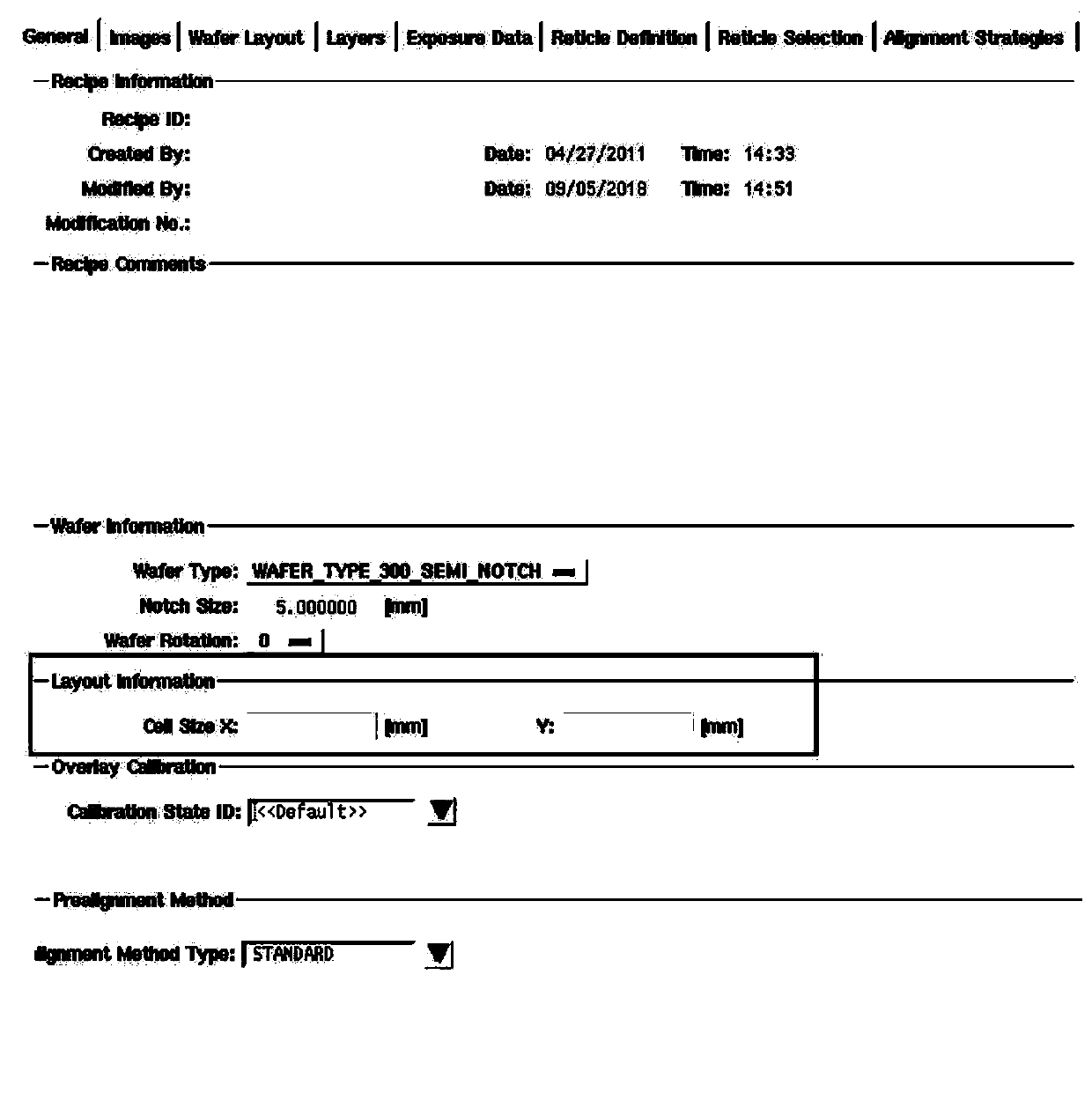

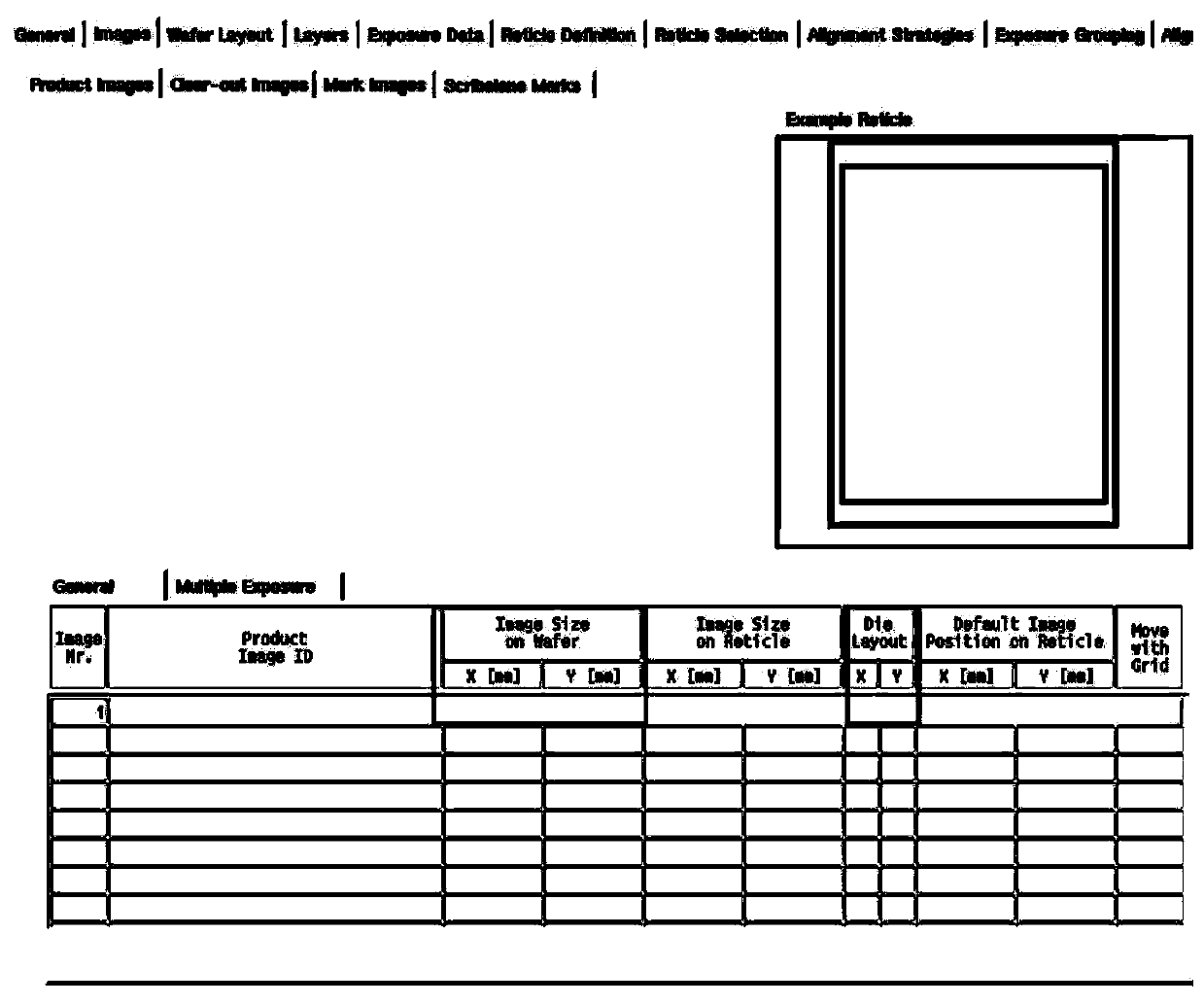

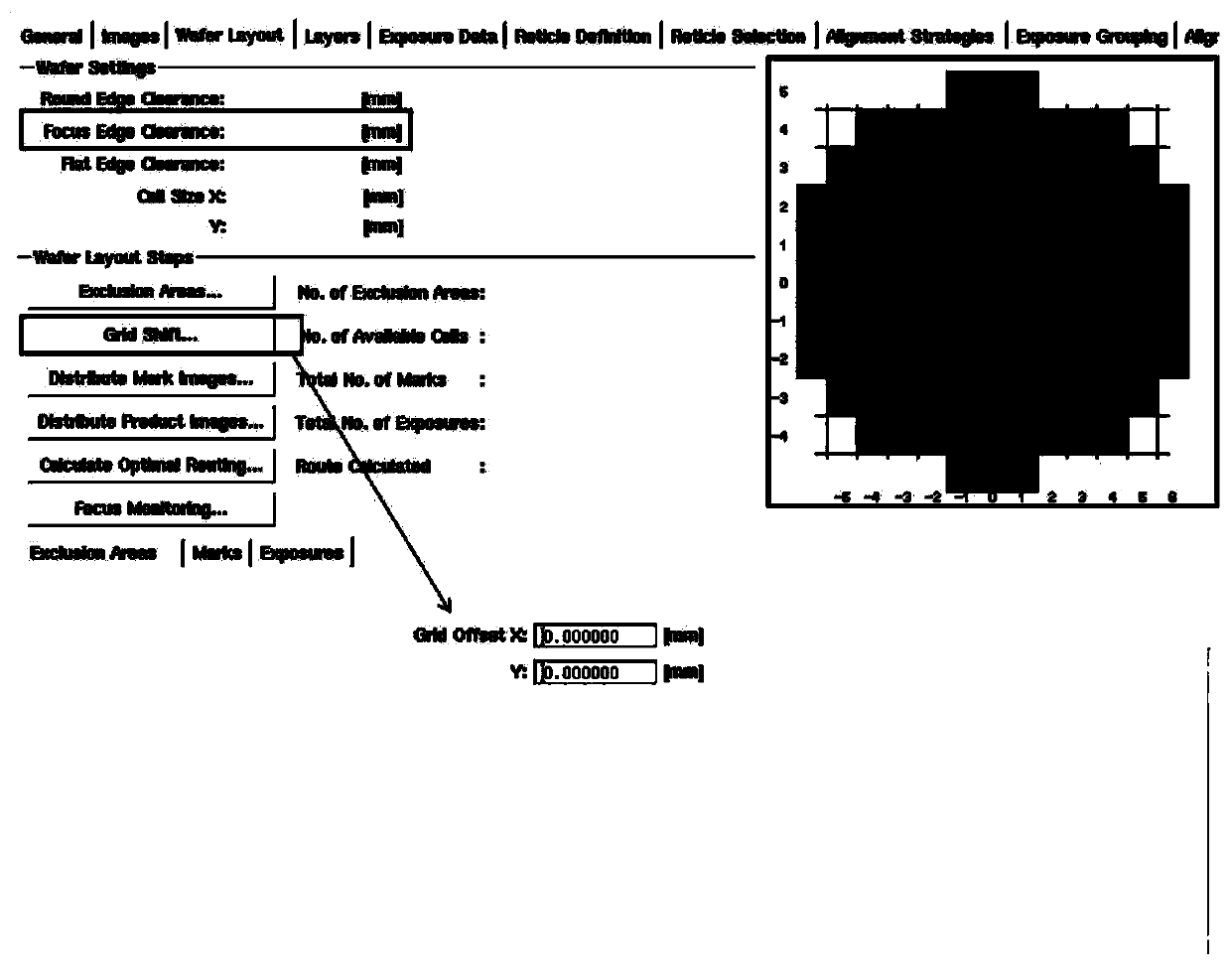

[0024] like Figure 4 as shown, Figure 4 It is shown as a flowchart of the method for arranging exposure regions on a wafer according to the present invention. The present invention provides a method for arranging exposure regions on a wafer, the method at least including the following steps:

[0025] Step 1. Provide exposure area information and lithography machine exposure information that affects the arrangement of exposure areas; in the lithography process, the maximum range of areas that a lithography machine can support for a single exposure is the exposure area. In the present invention, preferably, the exposure area information in step 1 includes: unit size, exposure area size, and the number of Dies arranged in one exposure area. According to the exposure area, the wafer surface is divided into grids (grid) of several rectangular areas of the same size. The area in each grid is called a unit cell, and there is one exposure area in each unit. The area of the expo...

Embodiment 2

[0033] like Figure 4 as shown, Figure 4 It is shown as a flowchart of the method for arranging exposure regions on a wafer according to the present invention. The present invention provides a method for arranging exposure regions on a wafer, the method at least including the following steps:

[0034] Step 1. Provide exposure area information and lithography machine exposure information that affects the arrangement of exposure areas; in the lithography process, the maximum range of areas that a lithography machine can support for a single exposure is the exposure area. In the present invention, preferably, the exposure area information in step 1 includes: unit size, exposure area size, and the number of Dies arranged in one exposure area. According to the exposure area, the wafer surface is divided into grids (grid) of several rectangular areas of the same size. The area in each grid is called a unit cell, and there is one exposure area in each unit. The area of the expo...

PUM

| Property | Measurement | Unit |

|---|---|---|

| width | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com