A memory access optimization method and system for graph processing based on activeness layout

An optimization method and graph processing technology, applied in special data processing applications, other database retrieval, other database indexes, etc., can solve problems such as affecting graph processing efficiency, large optimization space, ignoring inactive data load pressure, etc. The effect of processing efficiency, improving memory access speed, and reducing memory access waiting time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0039] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention. In addition, the technical features involved in the various embodiments of the present invention described below can be combined with each other as long as they do not constitute a conflict with each other.

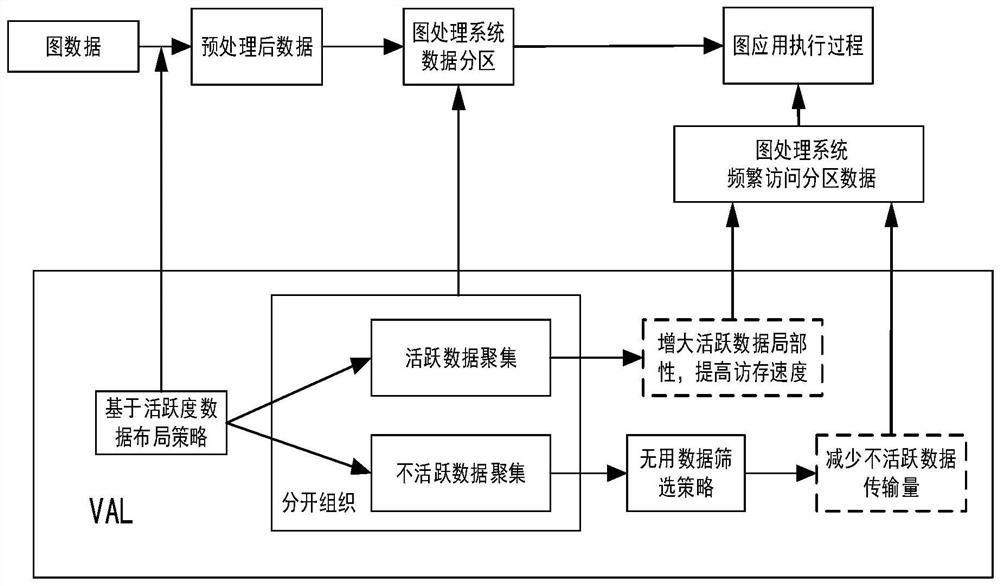

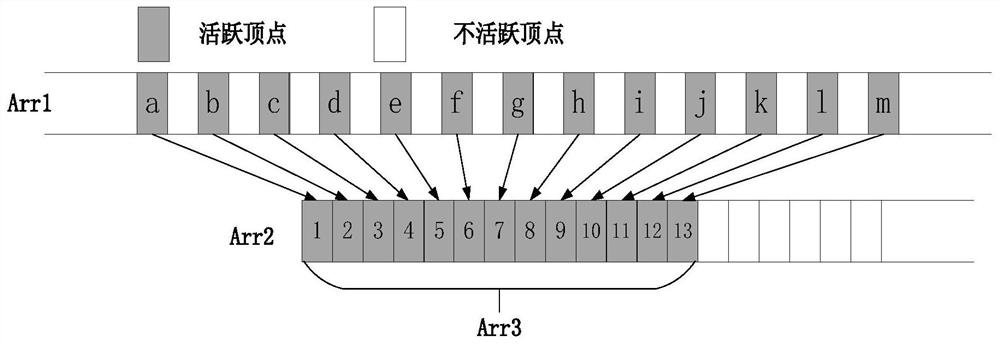

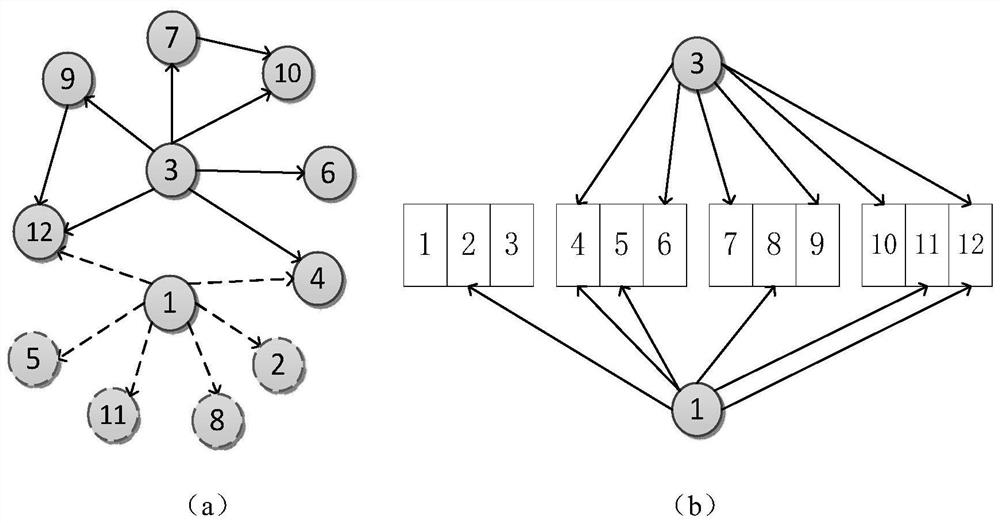

[0040] In order to reduce the memory access waiting time during the execution of the graph application and improve the graph processing efficiency, the present invention provides a graph processing memory access optimization method and system based on activity layout. Rearrange, consider the distribution of active data and inactive data at the same time, improve the data layout of the graph part...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More