Annular buffer self-adaptive network-on-chip router

An on-chip network and ring buffer technology, applied in the electronic field, can solve problems such as resource waste and system resources cannot be fully utilized, and achieve the effect of reducing message delay and improving network performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

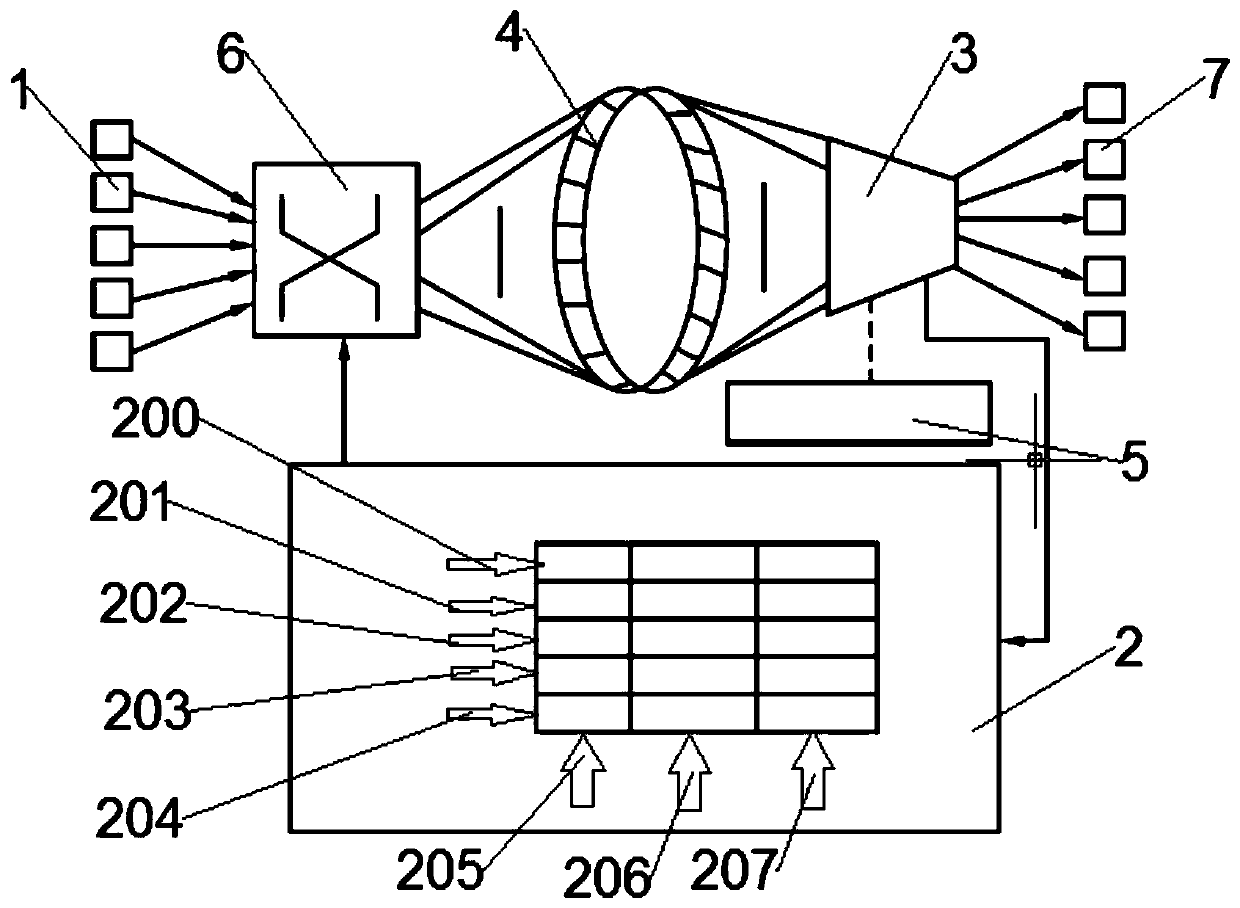

[0015] The present invention will be further described below in conjunction with the accompanying drawings.

[0016] like figure 1 As shown, a ring buffer adaptive network-on-chip router according to the present invention includes an input channel 1, a buffer management register group 2, a data selector 3, a ring buffer 4, a data packet decoder 5, and a crossbar switch matrix 6 and output channel 7, the input channel 1 and output channel 7 are provided with 5, the input channel 1 is connected with the ring buffer 4 through the crossbar matrix 6, and the ring buffer 4 is connected with the output channel 7 through the data selector 3 , the buffer resources in the input channel 1 and the output channel 7 form a ring with each other, and the data selector 3 is connected to the crossbar switch matrix 6 through the buffer management register group 2 .

[0017] Further, the buffer management register group 4 is divided into five rows and three columns, the five rows are divided int...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More