Method for managing a DVFS power supply and corresponding system

A system-on-chip, power management technology, applied in data processing power supply, electrical digital data processing, digital data processing components, etc., can solve the problems of delay and performance loss, increase execution time, increase energy consumption, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

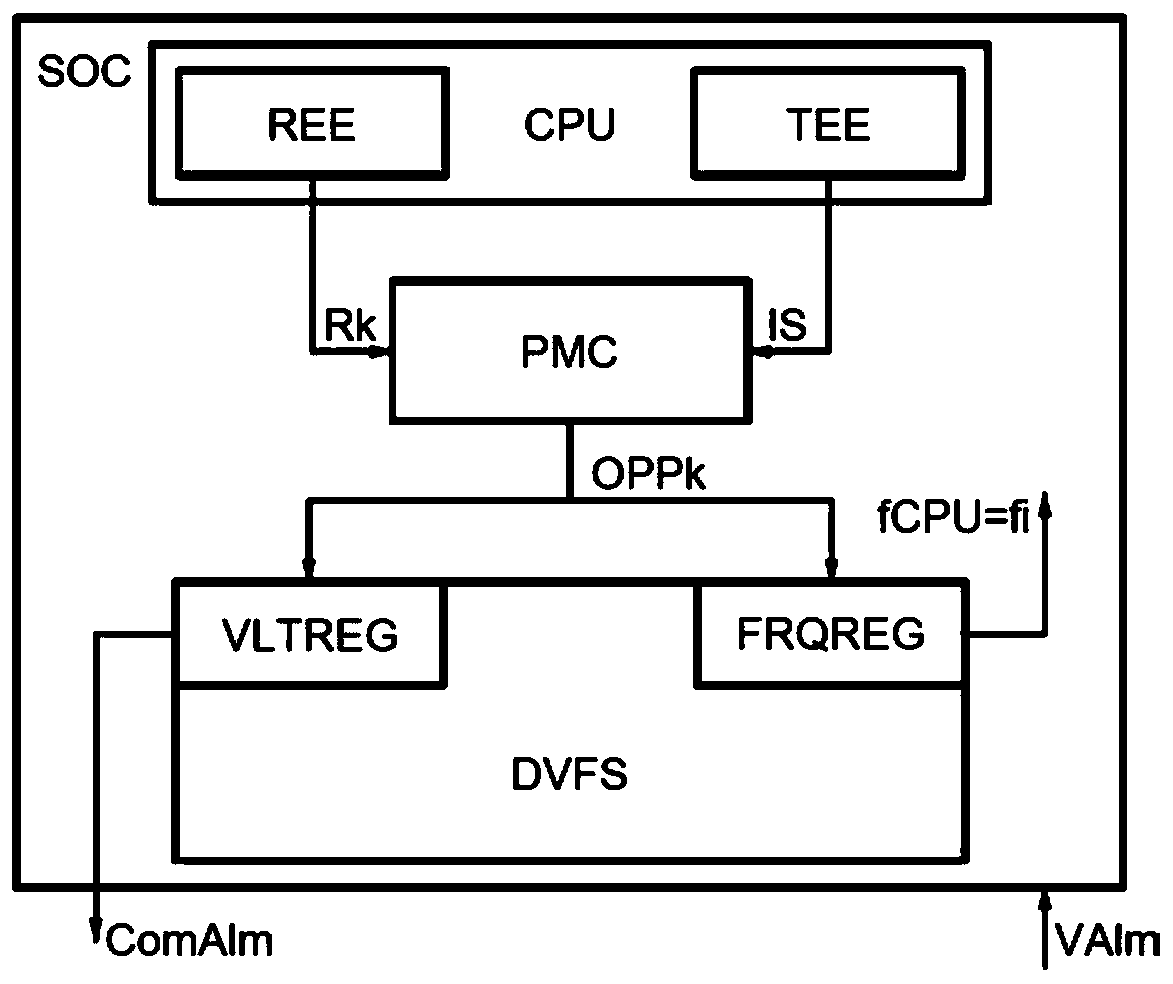

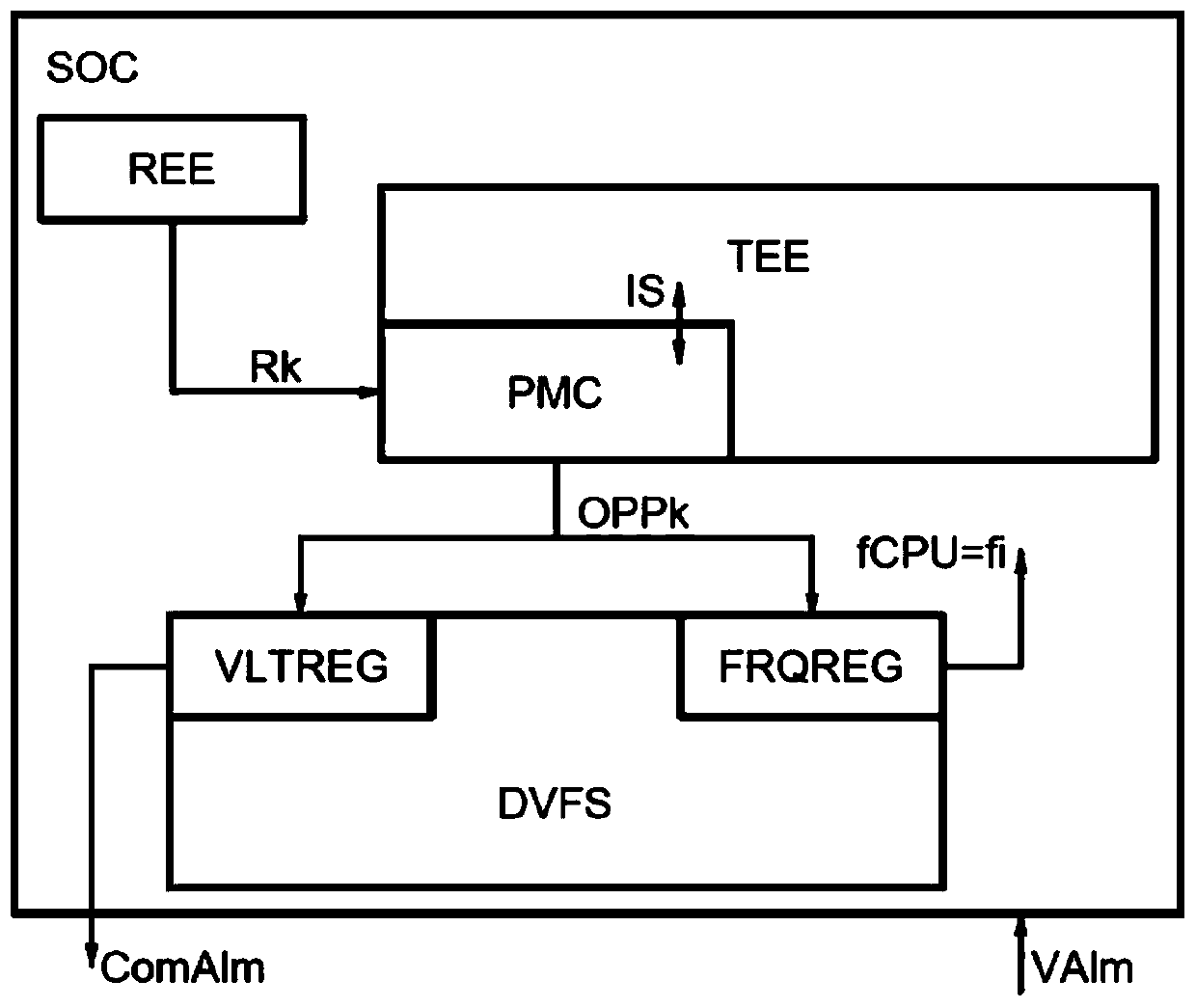

[0057] figure 2 represents one embodiment of a system-on-chip SOC.

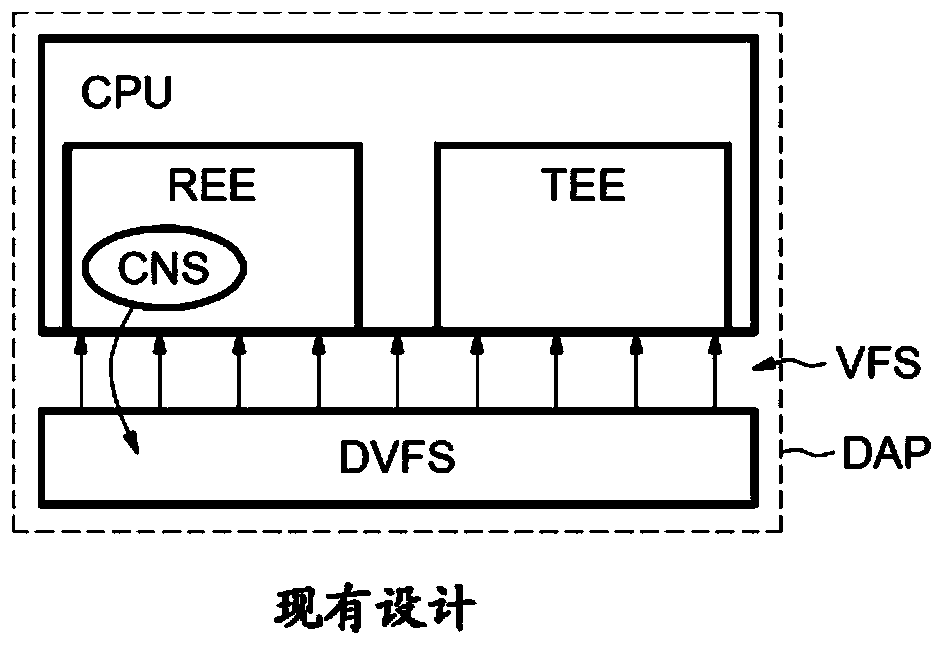

[0058] A system-on-chip SOC includes a dynamic voltage and frequency scaling type of power supply known as "DVFS". The system-on-chip includes a microprocessor-type secure environment TEE and a non-secure environment REE, which are software code execution environments.

[0059] In this example, the secure environment TEE and the non-secure environment REE belong to the same computing unit CPU of microprocessor type. Communication between the secure environment TEE and the outside world (in particular the non-secure environment REE) is performed via a hardware interface configured to prevent unauthorized access. It is also contemplated that the secure environment TEE and the non-secure environment REE are implemented on two physically separate computing units sharing the same power source.

[0060] In this example, the DVFS power supply includes a frequency regulator FRQREG and a voltage regulator VLTREG. ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More