Method for layout wiring of transistors in to-be-tested array one by one

A transistor and wiring technology, which is applied in the field of layout and wiring of transistors in the array to be tested one by one, can solve the problems of small feature size, increased complexity, and inability to meet the needs of integrated circuit design, and can ensure the quality of wiring and save time. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

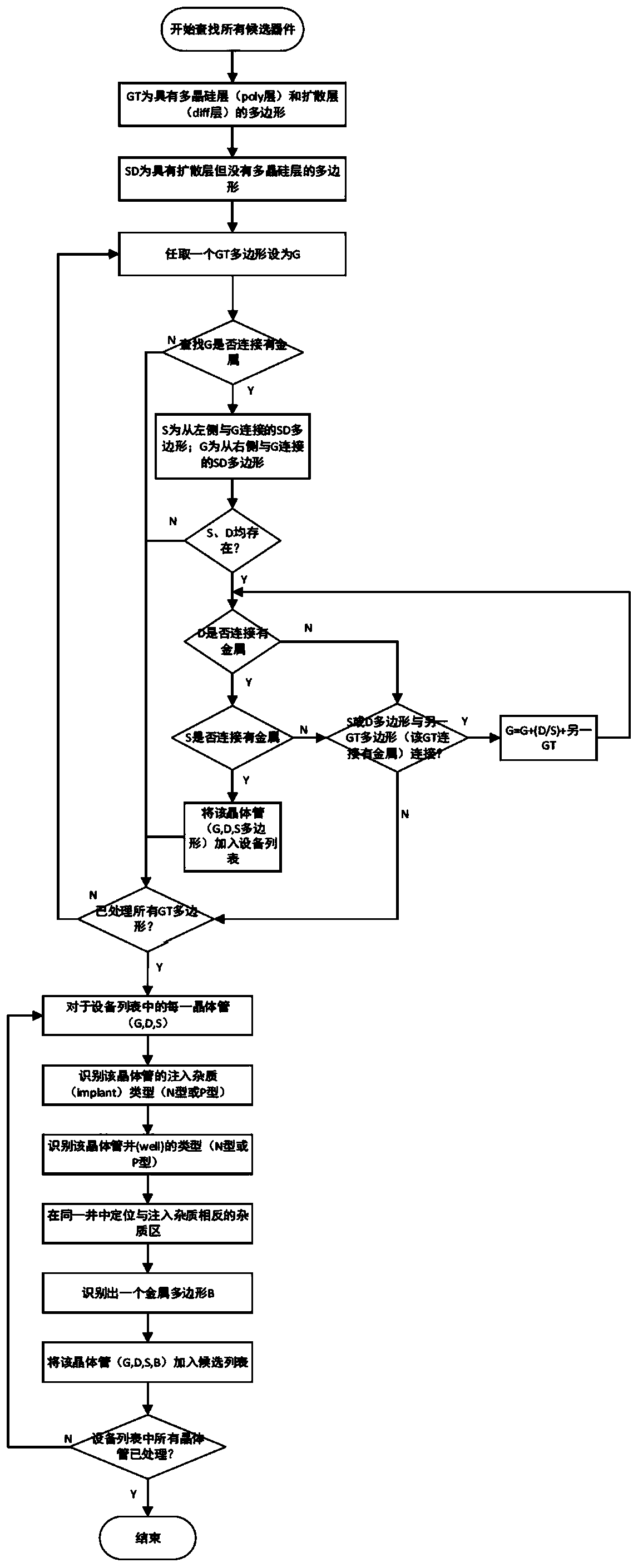

[0059] Below in conjunction with accompanying drawing and specific embodiment the present invention is described in further detail:

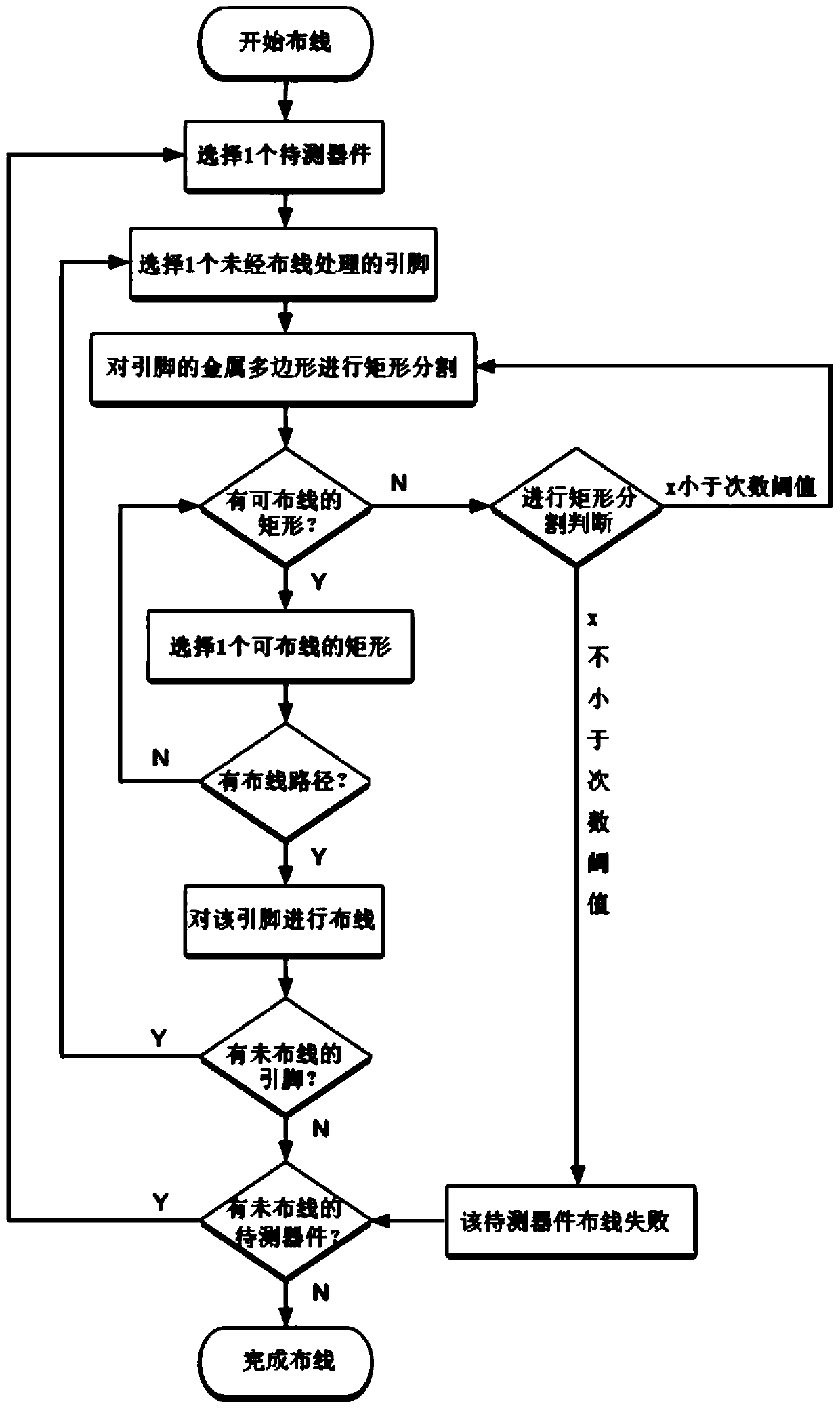

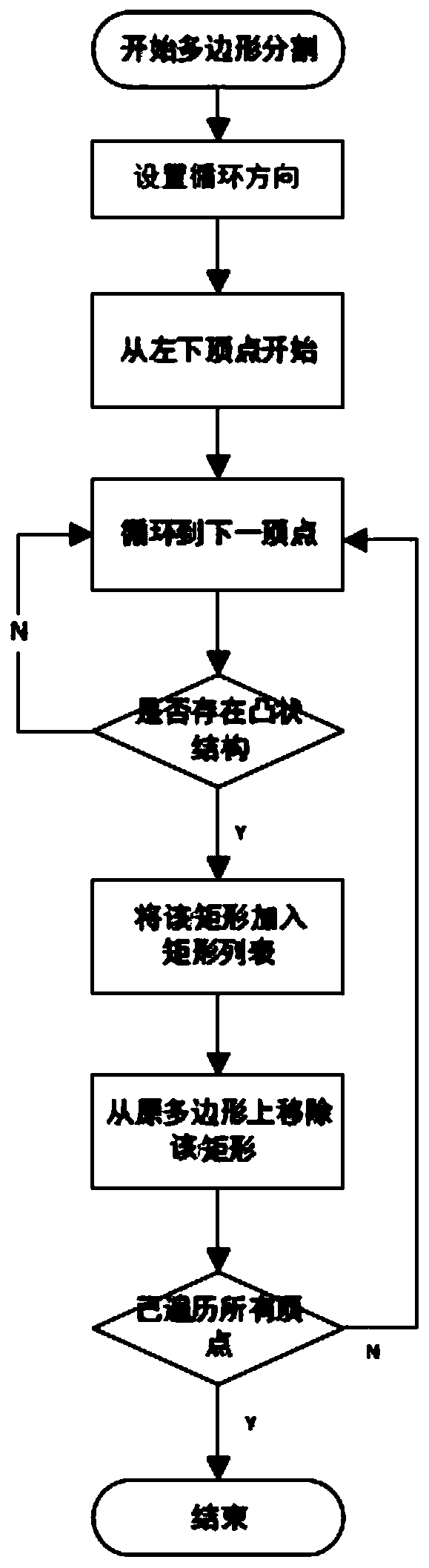

[0060] A method for performing layout and wiring of transistors in an array to be tested one by one, including a preprocessing process and a wiring process; the method can ensure the quality of wiring and save time while processing and wiring the devices to be tested one by one. The following is a detailed introduction.

[0061] The preprocessing process specifically includes the following steps:

[0062] Step (1): If the locations of all candidate devices (DUTs) are known, directly import the location information; if the locations of candidate devices are not known, search to obtain the locations of all candidate devices. After obtaining the positions of all candidate devices, determine the device under test corresponding to each metal frame (frame) from the candidate devices. Candidate devices in the center of the frame; each metal frame cor...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More