Patents

Literature

128 results about "Test array" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

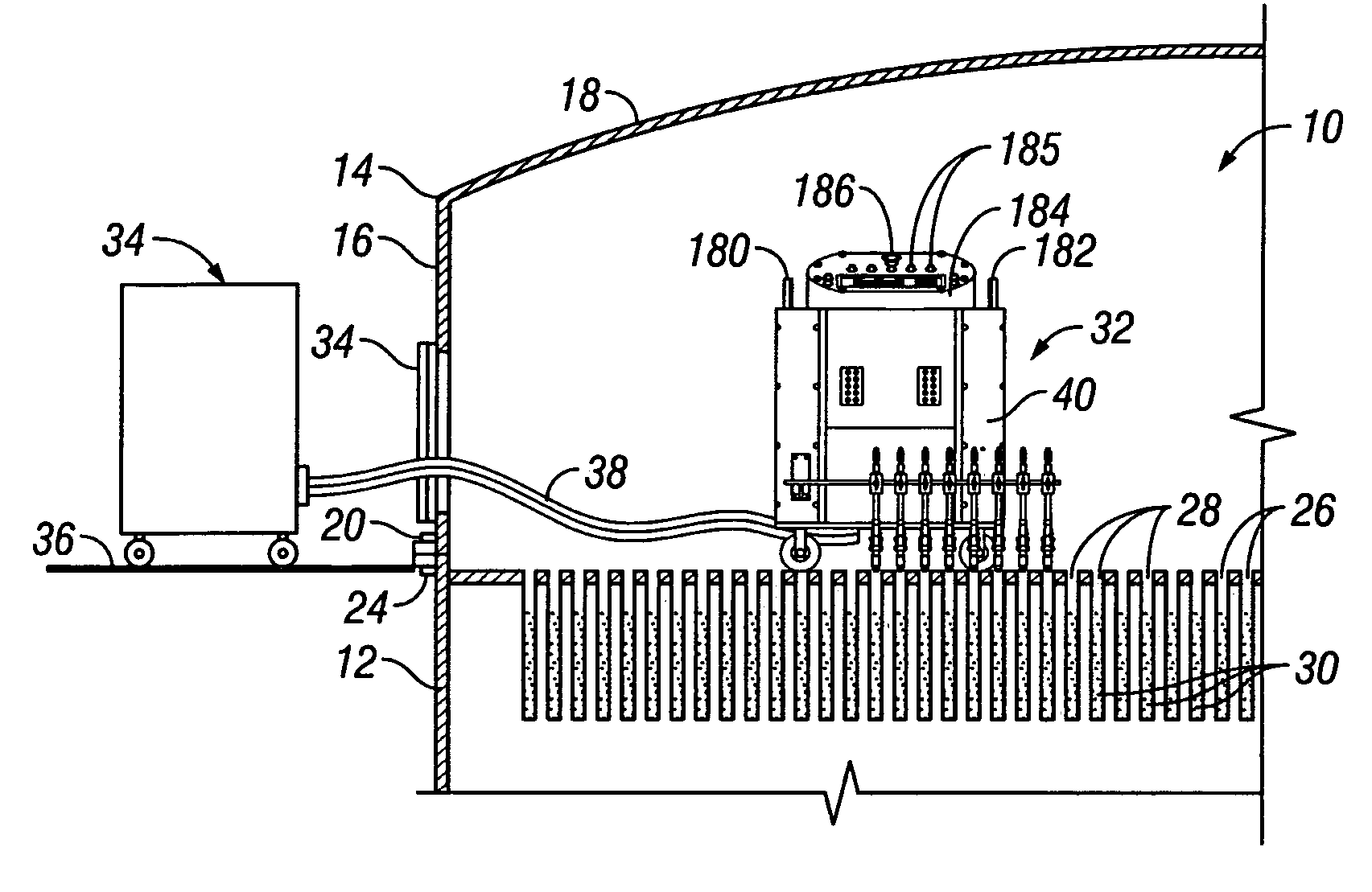

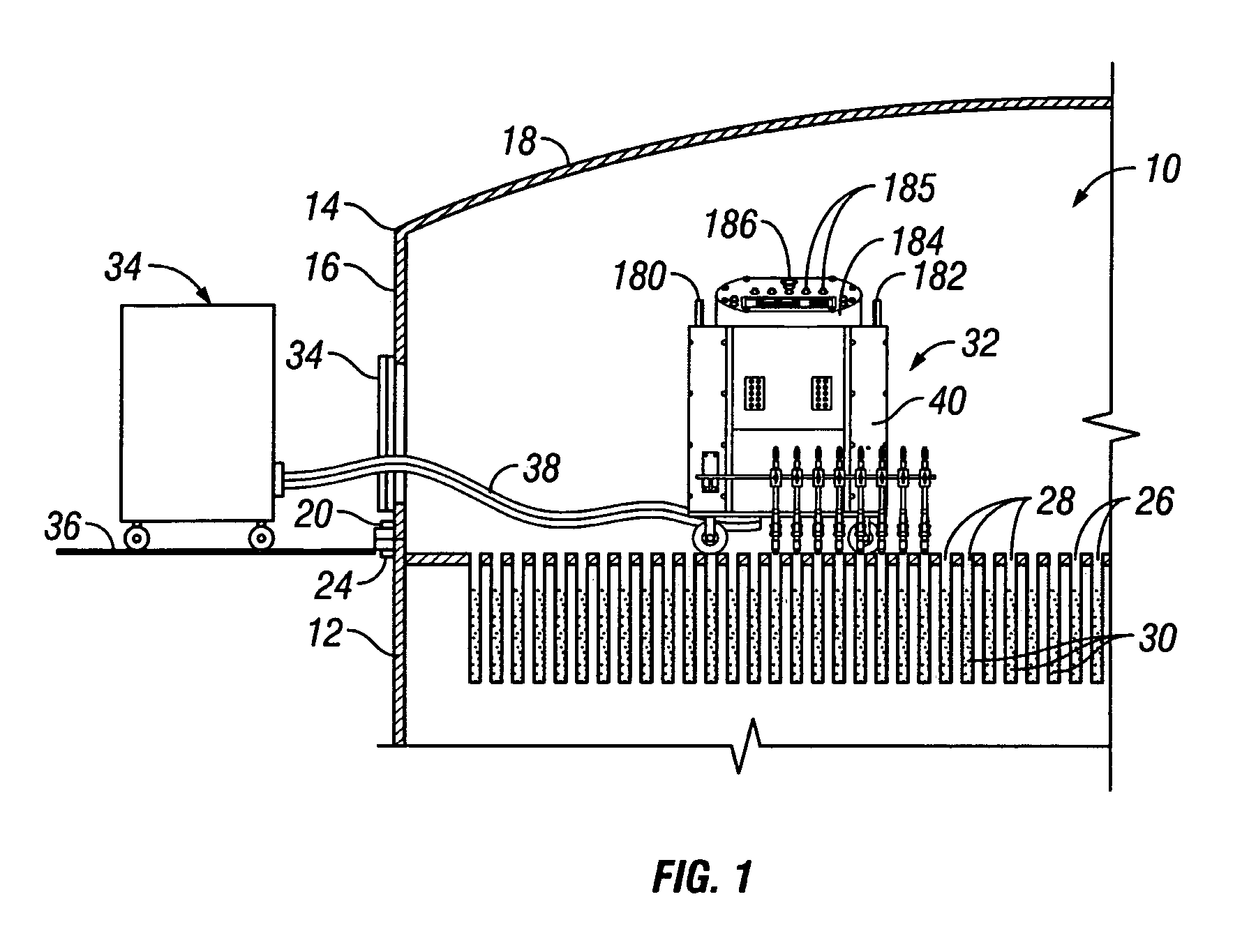

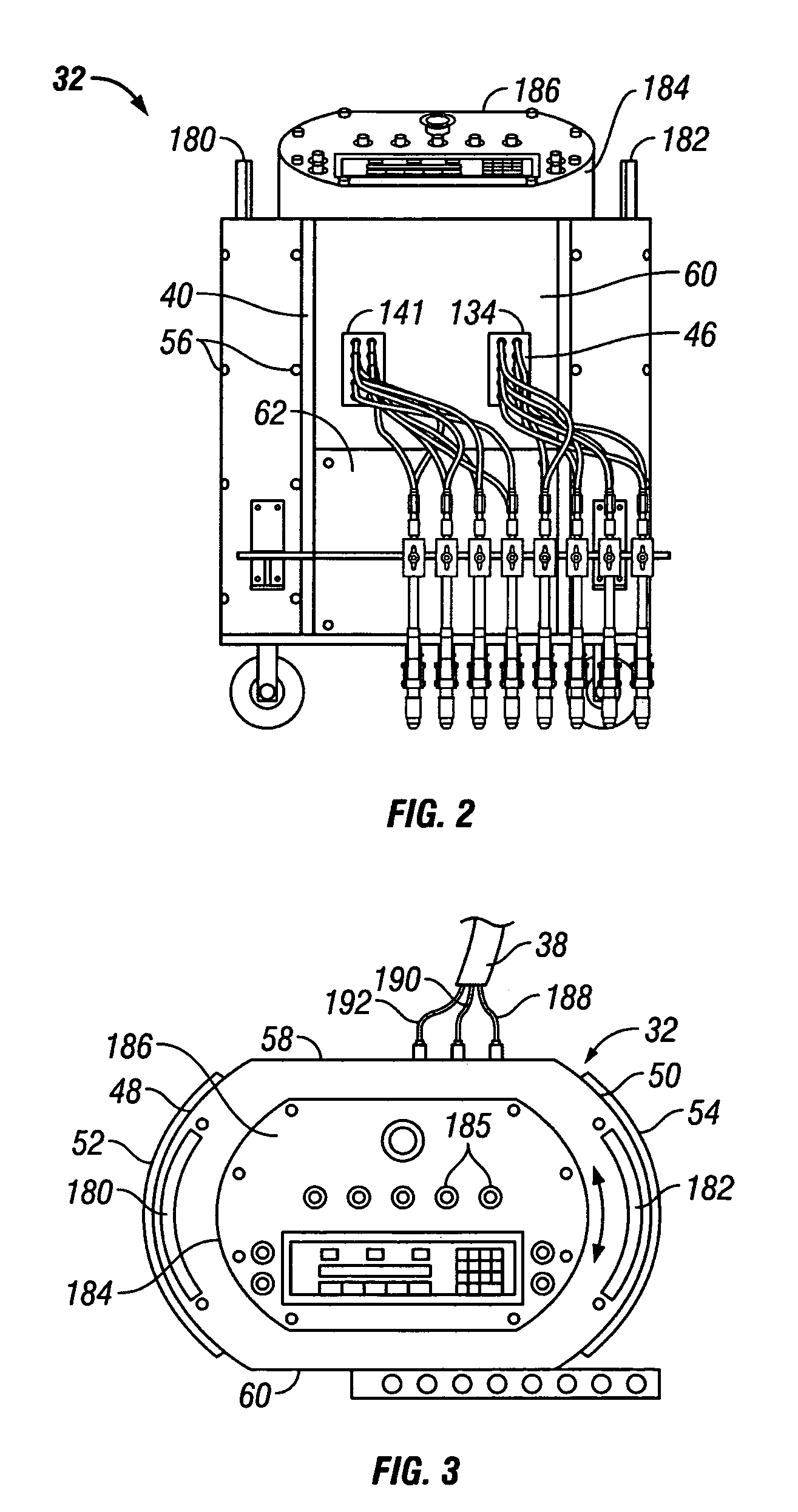

Method and apparatus for differential pressure testing of catalytic reactor tubes

ActiveUS6981422B1Efficient testingMinimizes servicing timeProcess control/regulationMaterial strength using tensile/compressive forcesDifferential pressureEngineering

A multi-tube differential pressure (Delta P) testing system for testing catalyst filled tubes of tube and shell type catalytic reactors has at least one mobile test unit for movement on the upper tube sheet of a catalytic reactor. An array of test probes is mounted to the mobile test unit and is selectively positionable in sealed gas pressure communicating engagement within the upper ends of selected reactor tubes. A pressure testing gas delivery system is interconnected with the test probes and selectively communicates pressurized gas to the testing tubes at a blow-down pressure or selected test pressure determined by restricted orifices. A differential pressure measurement system measures the back-pressure resulting from application of test pressure to individual reactor tubes and having a computer receiving electronic back-pressure measurement data and producing an electronic and / or visual record correlated with a reactor tube numerical sequence and identifying the resulting back-pressure of each reactor tube of the multi-tube test. The testing system is capable of selectively electronically counting in normal sequence and in inverted sequence to accommodate test unit orientation and incorporates a separate manually positioned testing wand to accommodate tube positions of the reactor that cannot be readily accessed by one or more of the array of test probes.

Owner:WINDLASS METALWORKS

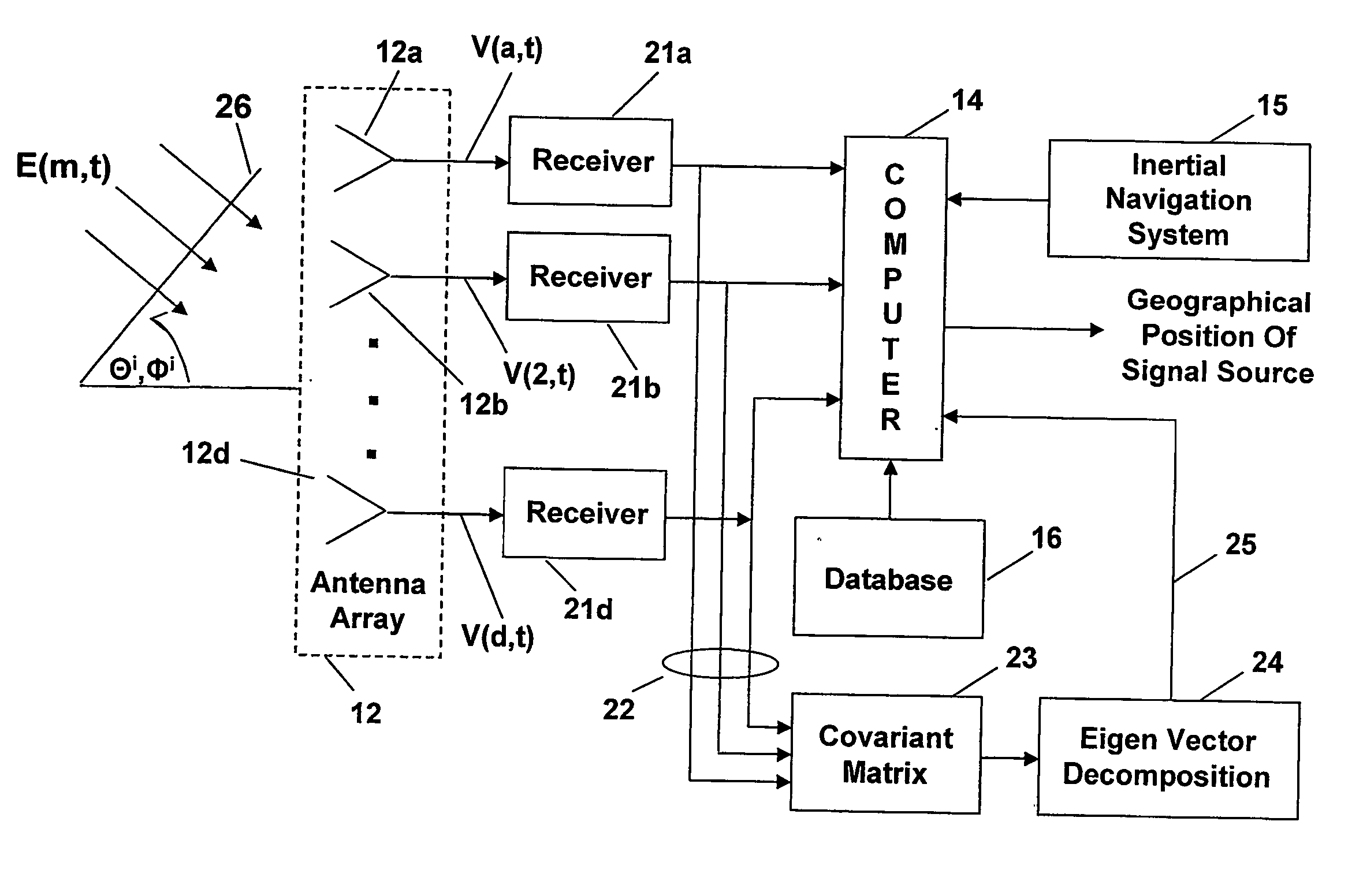

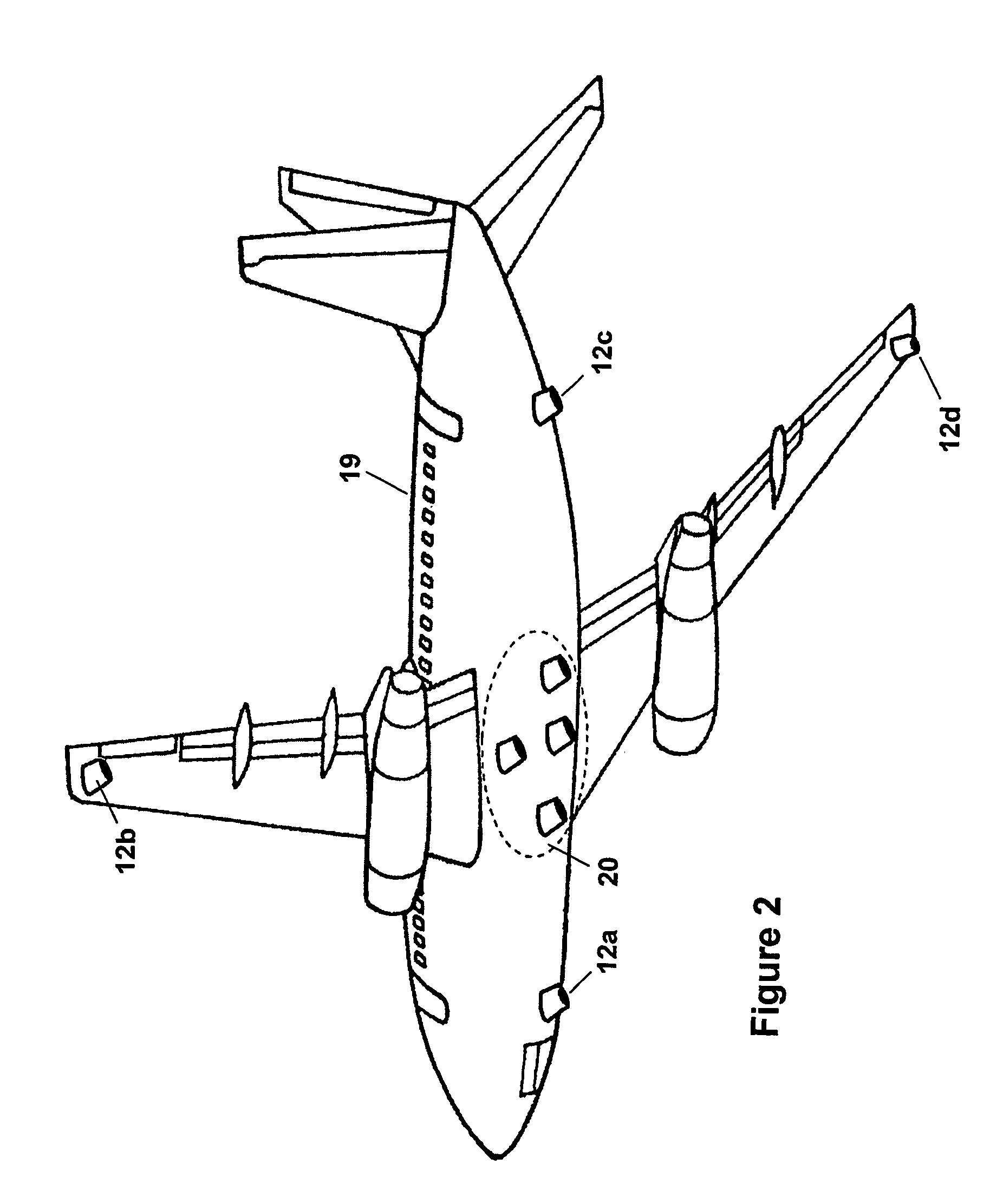

Correlation interferometer geolocation

ActiveUS20060087475A1Accurate identificationReduces extraneous correlation peaksDirection finders using radio wavesPosition fixationGeolocationTest array

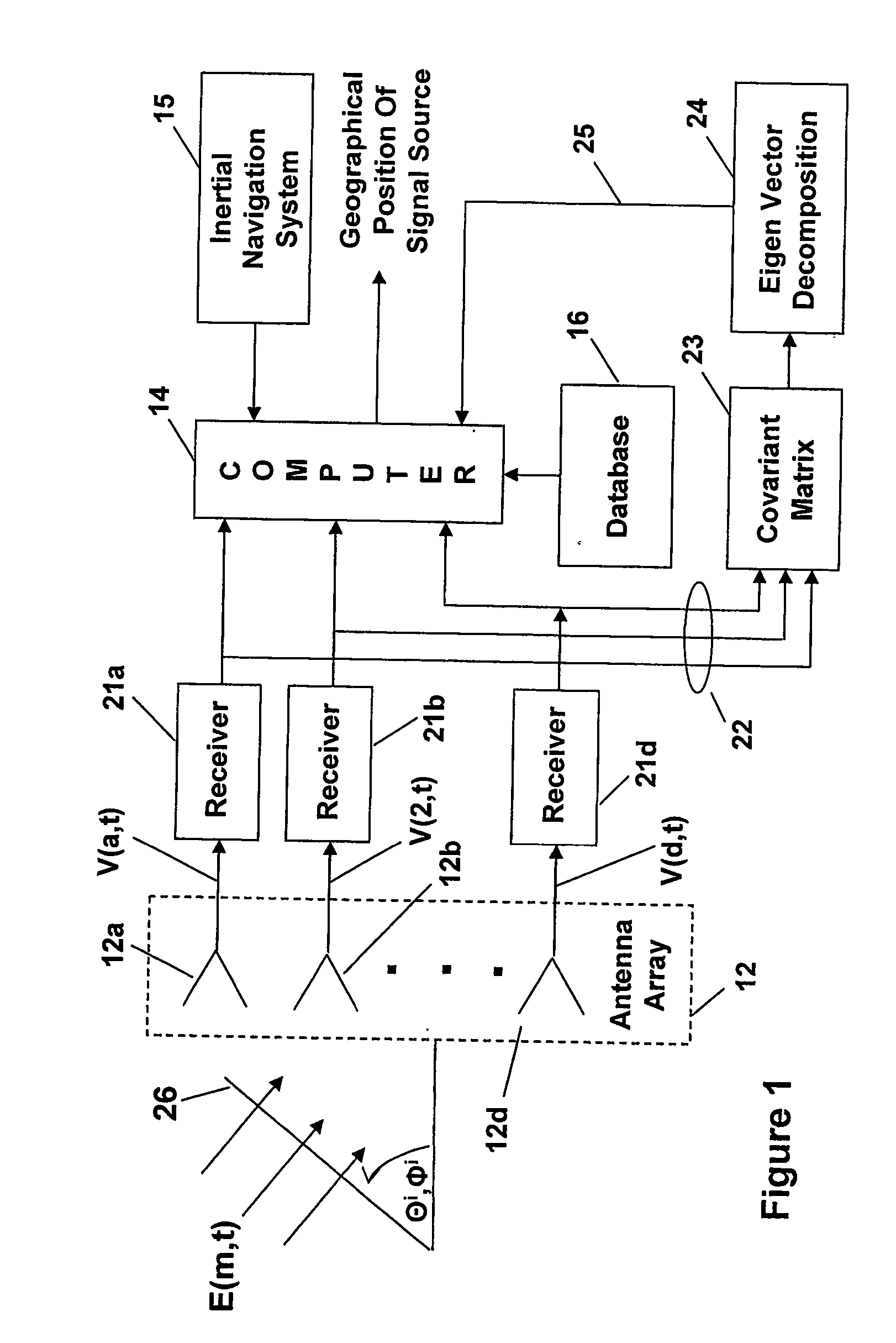

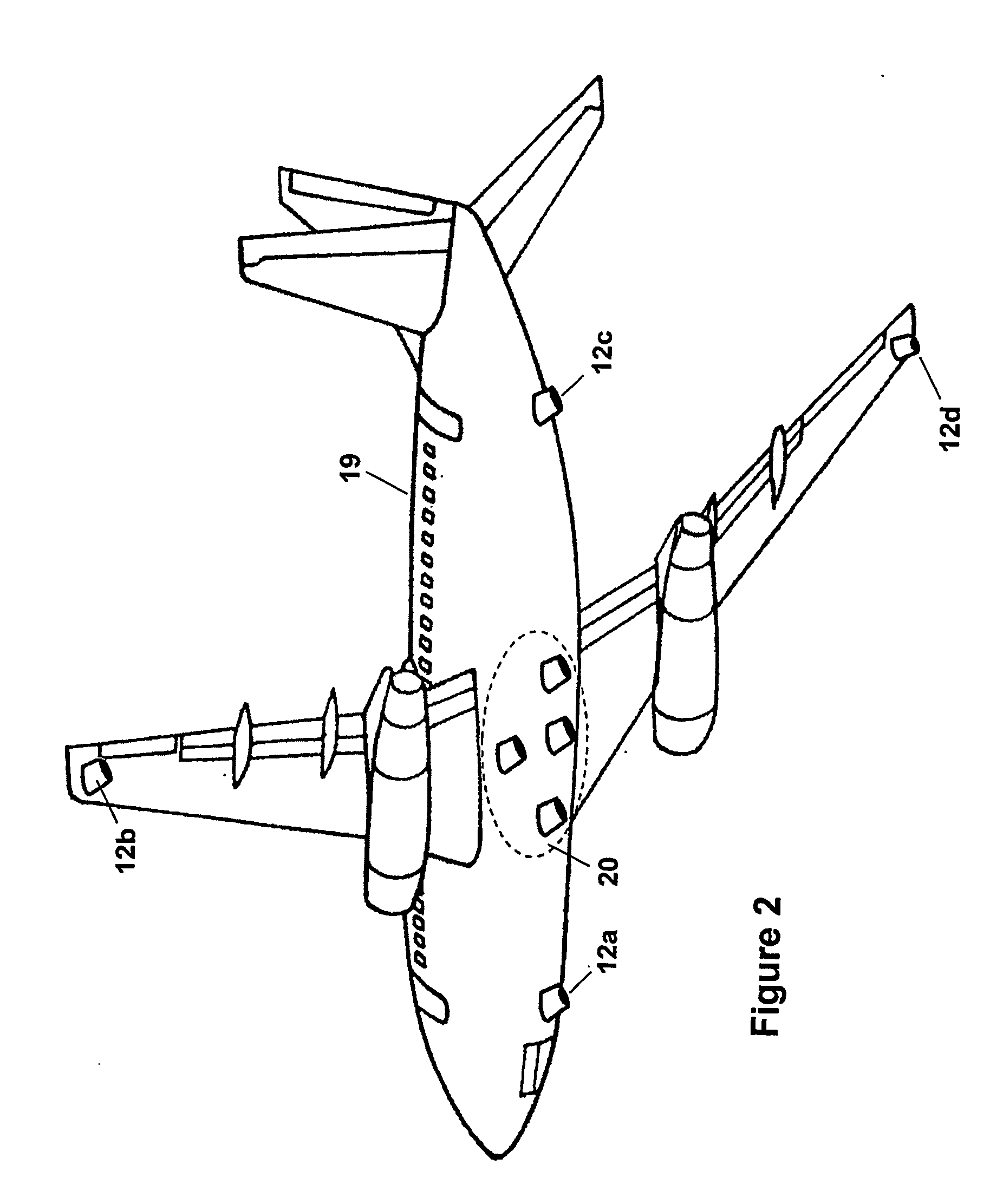

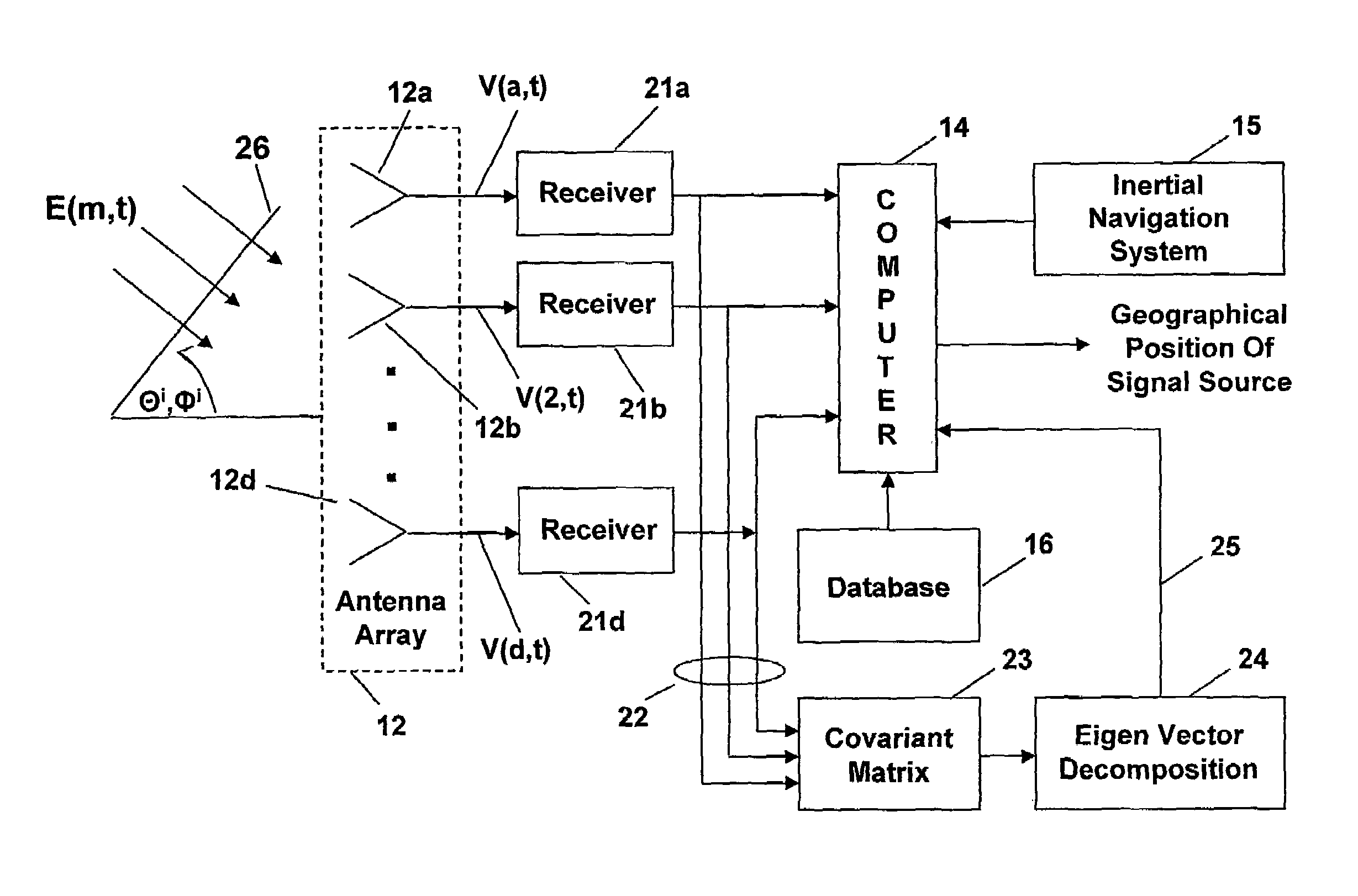

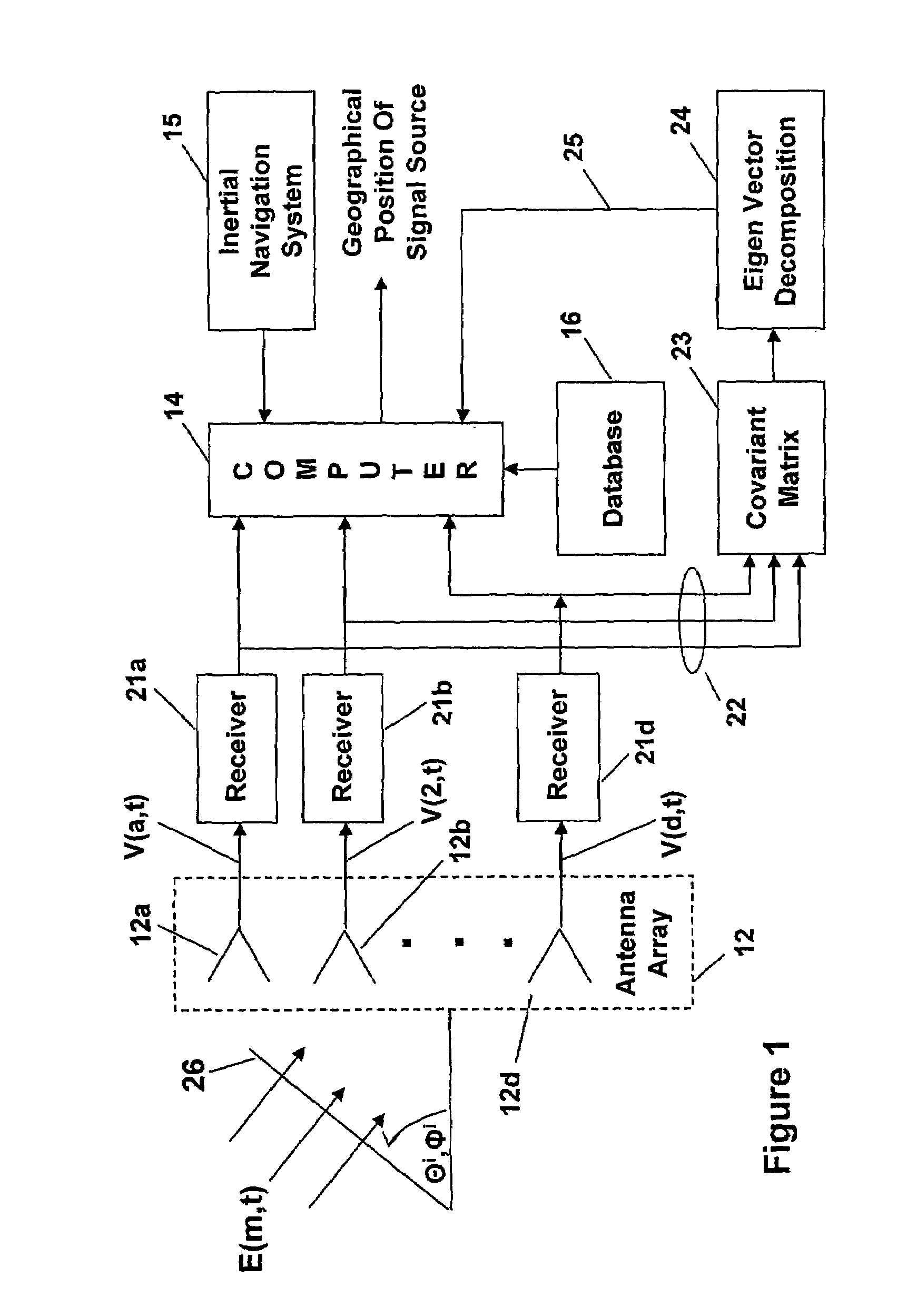

Correlation Interferometer Geo Location (CIGL) uses DF antenna array movement on an aircraft while taking a Plurality of sets of transinitted signal Measurements. Each measurement set is stored as data in a covariance matrix, and the matrices are each decomposed to yield measured array vectors. Using an array manifold table developed during calibration of the CIGI. system, and containing testing array vectors, the measured array vectors are each correlated to testing array vectors to develop a correlation Surface that includes compensation for perturbations Such as aircraft induced electromagnetic scattering, All the correlation surfaces are summed and normalized, with the resultant summation undergoing conjugate gradient processing to more accurately geo-locate the transmitter. Improved accuracy with fewer antennas and polarization independence are also achieved.

Owner:BAE SYST INFORMATION & ELECTRONICS SYST INTERGRATION INC

Correlation interferometer geolocation

ActiveUS7233285B2Accurate identificationReduces extraneous correlation peaksDirection finders using radio wavesPosition fixationGeolocationColatitude

Correlation Interferometer Geo Location (CIGL) uses DF antenna array movement on an aircraft while taking a Plurality of sets of transmitted signal Measurements. Each measurement set is stored as data in a covariance matrix, and the matrices are each decomposed to yield measured array vectors. Using an array manifold table developed during calibration of the CIGI. system, and containing testing array vectors, the measured array vectors are each correlated to testing array vectors to develop a correlation Surface that includes compensation for perturbations Such as aircraft induced electromagnetic scattering, All the correlation surfaces are summed and normalized, with the resultant summation undergoing conjugate gradient processing to more accurately geo-locate the transmitter. Improved accuracy with fewer antennas and polarization independence are also achieved.

Owner:BAE SYST INFORMATION & ELECTRONICS SYST INTEGRATION INC

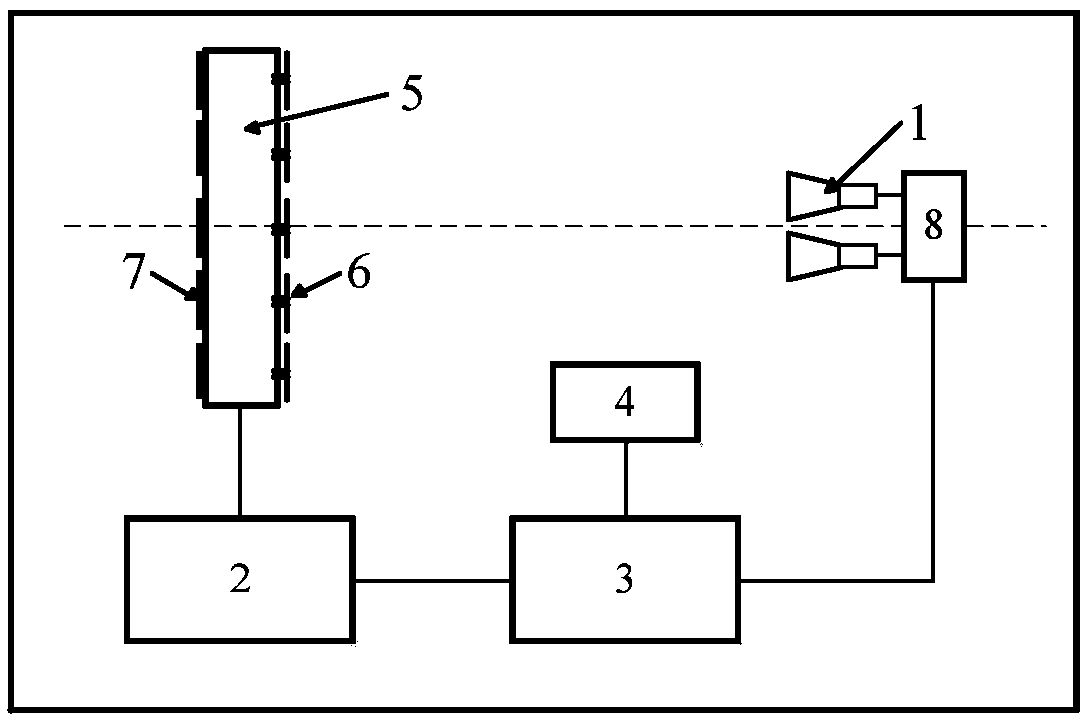

Array antenna channel calibration system for plane wave simulator

ActiveCN109541330ACalibration is flexible and applicableSave calibration timeElectromagentic field characteristicsAntenna radiation diagramsPhase differenceTransmission coefficient

The invention discloses an array antenna channel calibration system for a plane wave simulator, which comprises a plane wave simulator array antenna comprising multiple sub units, a regulating networkfor controlling the amplitude and the phase of each sub unit, a calibration probe antenna or probe array with a fixed and known position, a vector network analyzer, a connector cable and other accessories. The calibration system adopts a vector superposition principle, through control on the phase of the tested array antenna channel, in a far field area of the antenna from the two-dimensional array antenna aperture unit channel, a transmission coefficient (S21) value when the phase of the tested array antenna channel changes is acquired, and thus, the channel amplitude and phase difference isanalyzed. The channel calibration system has a wide application range and can be used for consistency calibration on the unit channels of the array antenna, especially for the unit channel calibration of the planar wave generator array antenna.

Owner:BEIHANG UNIV

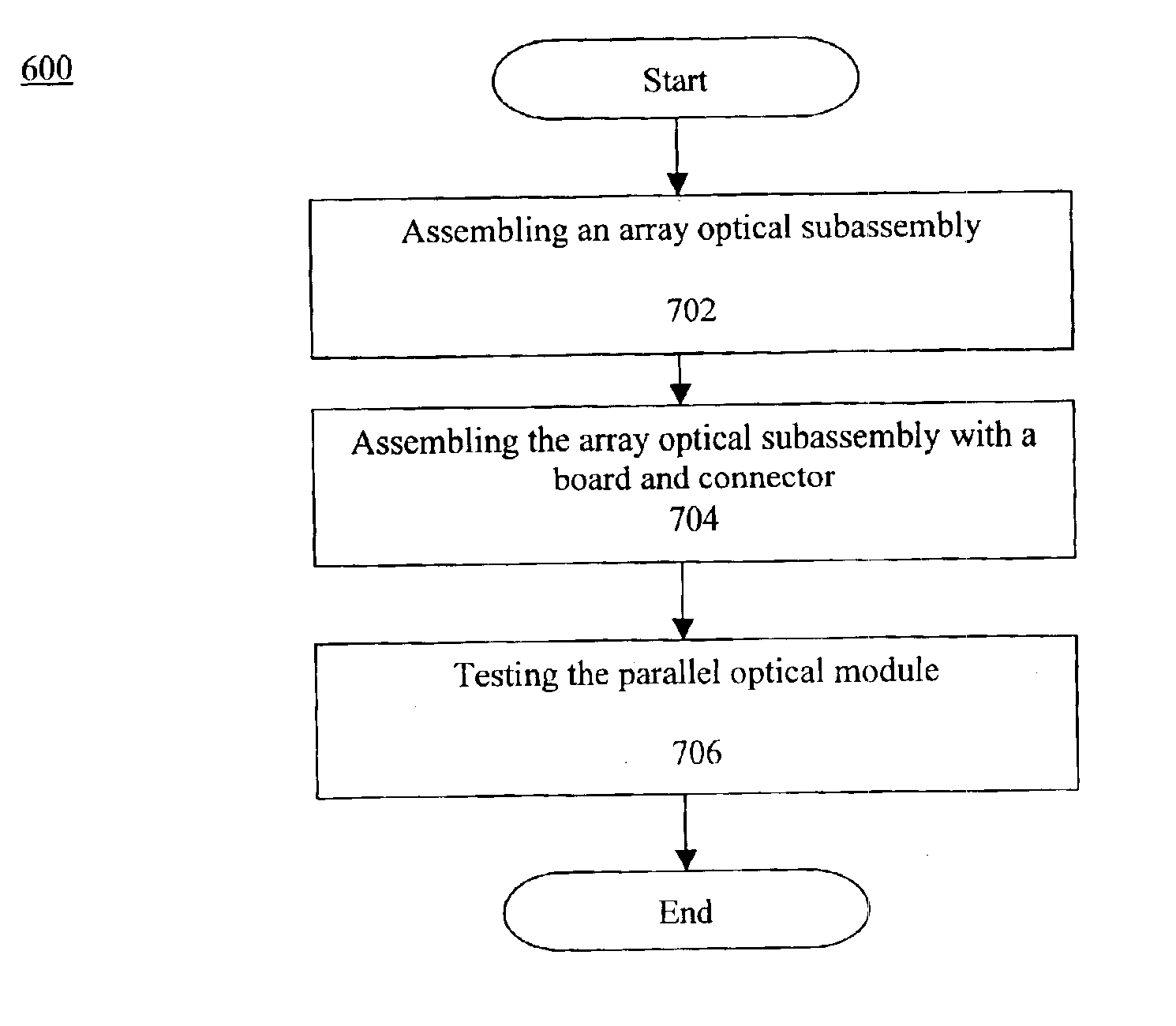

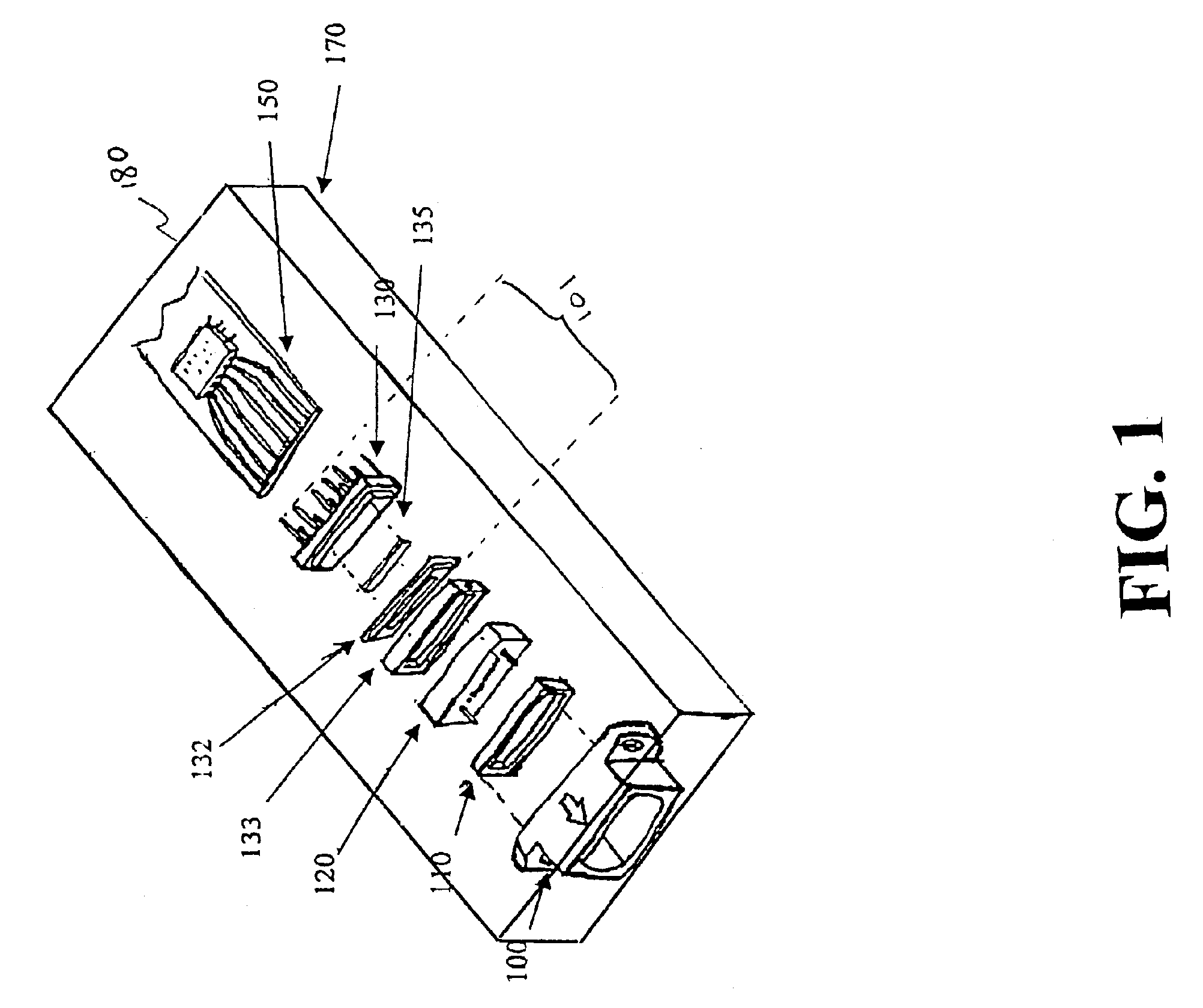

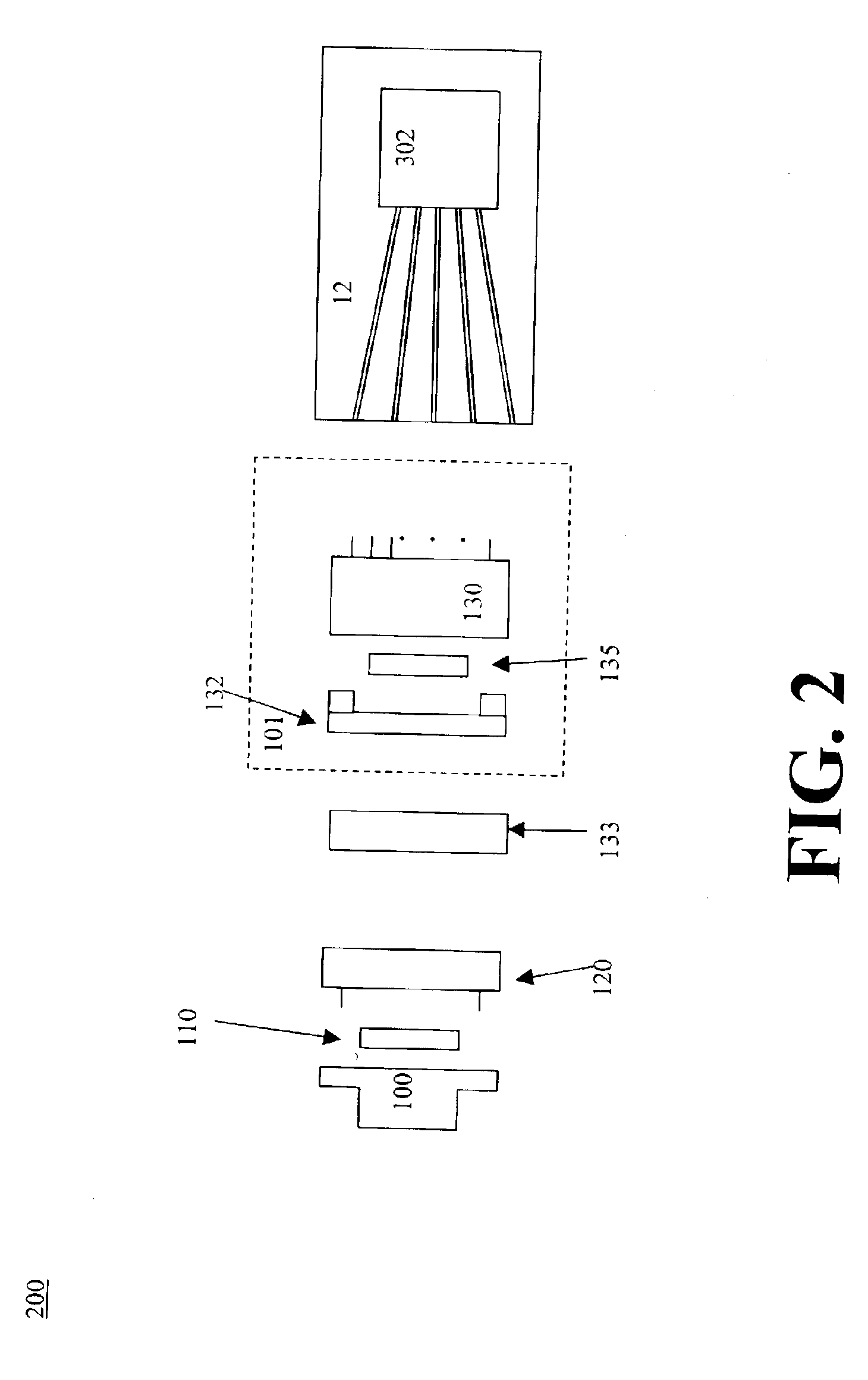

Method and apparatus for parallel optical transceiver module assembly

InactiveUS6863453B2Increase productionImprove equipment reliabilityCoupling light guidesOptical ModuleTransceiver

An apparatus and method of modular manufacturing process for a parallel optical transmitter, receiver and / or transceiver is disclosed. The modular process assembles an array of optoelectronic devices to an array header to form an optoelectronic array package. Once the optoelectronic array package is assembled, it is tested and verified the functionality and alignment between the optoelectronic devices and optical fibers. The optoelectronic array package is subsequently coupled to an optical lens array to form an array optical subassembly. After the array optical subassembly is tested, it is coupled to an optical fiber connector to form an optical module. The optical module is then tested to verify its functionality and alignment.

Owner:SUMITOMO ELECTRIC DEVICE INNOVATIONS U S A

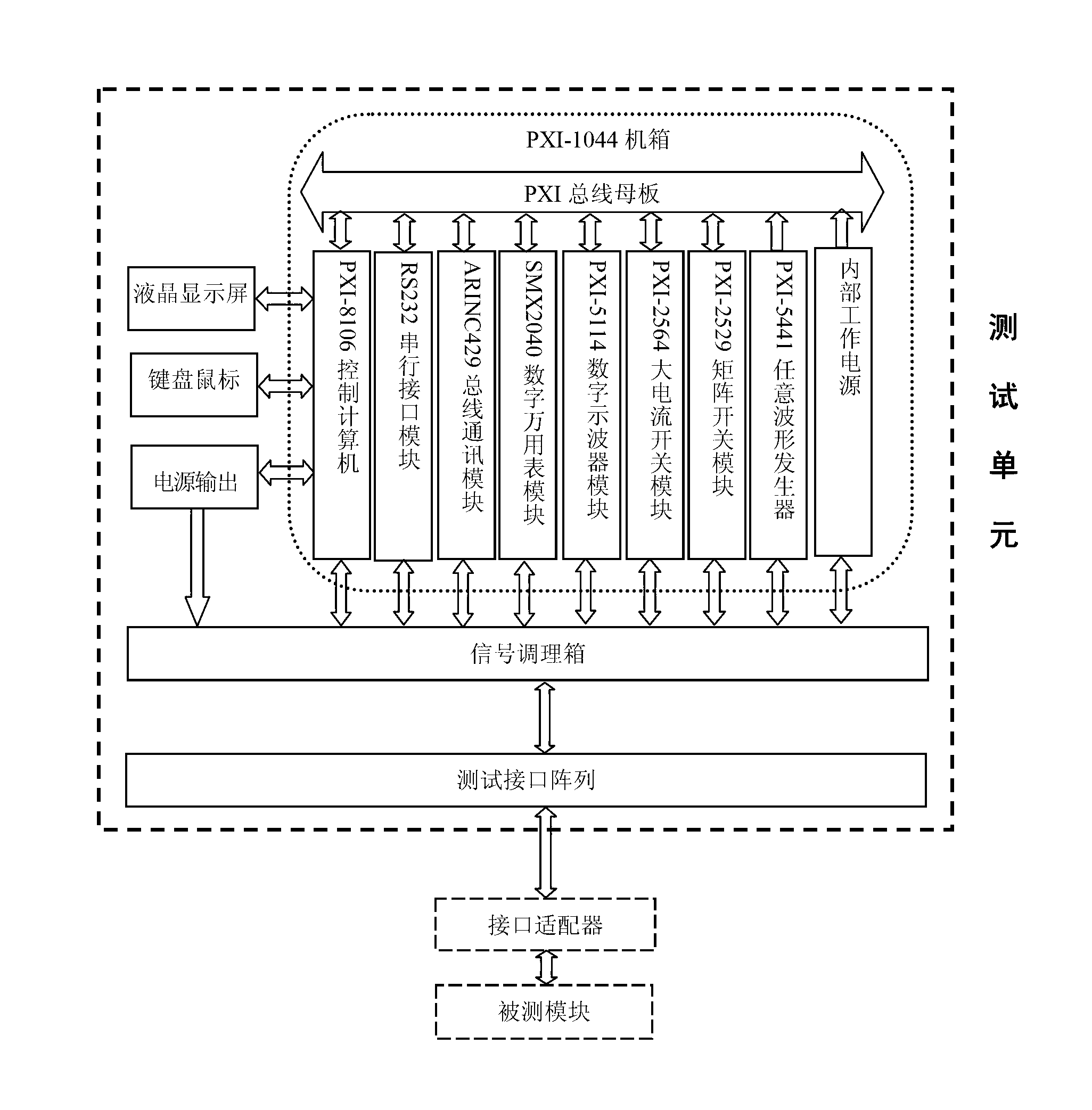

Automatic testing device and automatic testing method of ARINC 429 bus signal performance parameters

InactiveCN103019902AImprove quality levelImprove the level ofFunctional testingQuality levelTest fixture

The invention discloses an automatic testing device and an automatic testing method of ARINC 429 bus signal performance parameters; the device comprises a test unit, a test adapter and corresponding software program, wherein the test unit consists of a power control box, a PXI test case, a signal conditioning box, a test interface array and an input-output device; all resource modules in the test unit can be used for running a test program of the test unit by testing software under the control of a PXI control computer through a PXI bus; the adapter is meshed with an RCV end by an ITA end of a test array, and is connected with test resource modules on the test unit; and the testing software comprises two parts including testing software of the test unit and testing software specially used for the adapter. After the invention is adopted, the quality level of an ARINC 429 bus signal module product can be improved, the development of a special test device is omitted, and the development cost and the maintenance cost of the test device can be greatly lowered.

Owner:CHINESE AERONAUTICAL RADIO ELECTRONICS RES INST

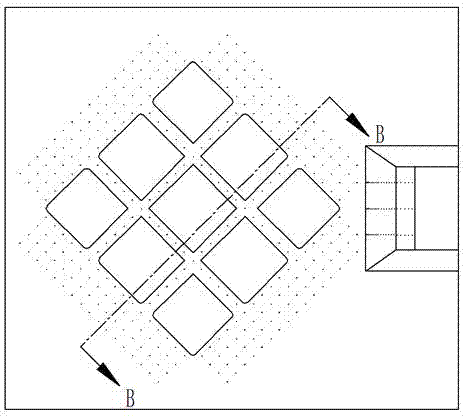

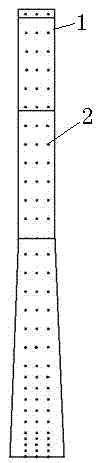

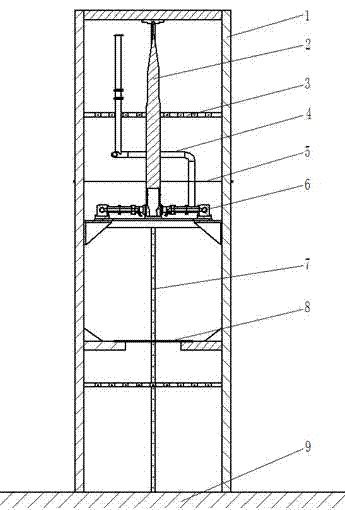

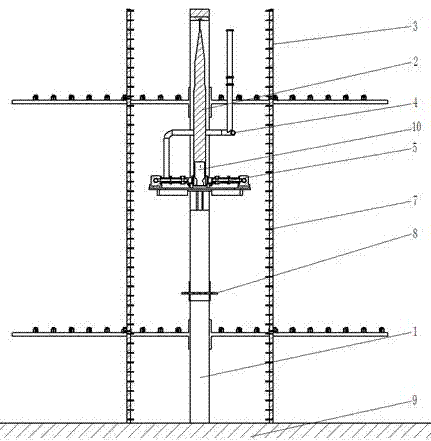

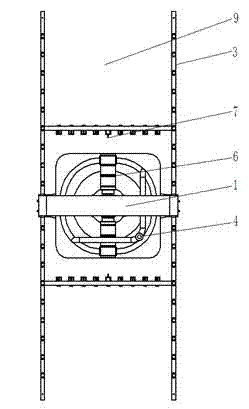

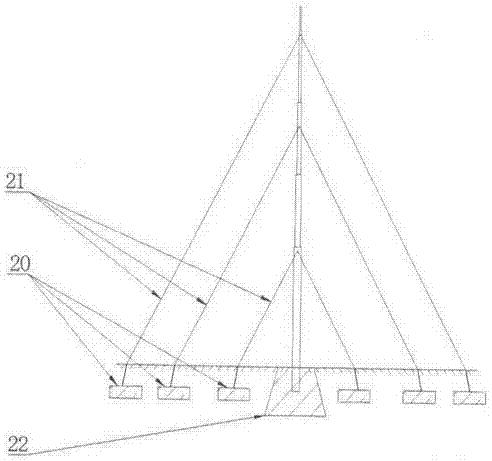

Monitoring system for carrier-rocket launch fuel-gas flow field

The invention discloses a monitoring system for a carrier-rocket launch fuel-gas flow field. The monitoring system includes a first test main array group and a second test main array group, wherein the first test main array group includes an in-diversion-hole fuel-gas flow field test array, a table-board fuel-gas flow field test array and an on-cross-beam fuel-gas flow field test array. The second test main array group includes a near-diversion-trench-entrance fuel-gas flow field parameter test array, a diversion-trench-drainage-guide-face fuel-gas flow field parameter test array, a guide-trench-top fuel-gas flow field parameter test array and a diversion-trench-side-face fuel-gas flow field parameter test array. The test scheme of the carrier-rocket launch fuel-gas flow field is applicable to carrier-rocket launch fuel-gas flow field testing and fuel-gas-flow ablation characteristic assessment and capable of being transplanted conveniently into a shrinkage-scale launch simulation test or fuel-gas flow field testing and fuel-gas ablation characteristic assessment in a special simulation test.

Owner:BEIJING INST OF SPACE LAUNCH TECH +1

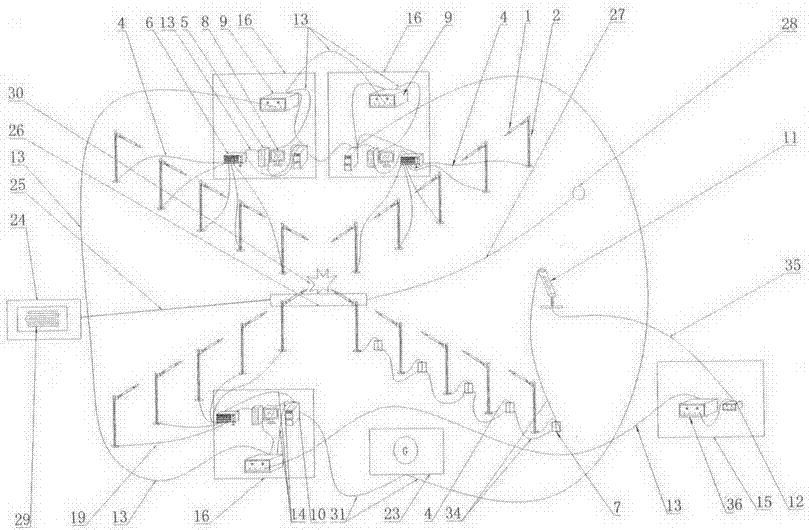

Detection system for single-jet-pipe rocket launch water-spray cooling noise-reduction effect

The invention discloses a detection system for a single-jet-pipe rocket launch water-spray cooling noise-reduction effect. The system includes a portal frame, a simulating rocket, a rocket positioning and adjustment device, a water-spray device, a noise detection device and a fuel-gas flow field and fuel-gas-flow ablation intensity detection device. The water-spray device is installed around an engine jet pipe of the simulating rocket. The noise detection device includes a noise test array frame installed around the simulating rocket and noise array sensors installed on the noise test array frame. The fuel-gas flow field and fuel-gas-flow ablation intensity detection device includes a jet-flow field and ablation intensity test board installed under the simulating rocket and a jet-flow field and ablation intensity sensor array installed on the jet-flow field and ablation intensity test board. Based on the system, researches of a rocket launch water-spray cooling noise-reduction mechanism and effect evaluation can be carried out and a reference is also supplied to the water-spray cooling noise-reduction effect of follow-up complete simulating rocket launch technical conditions.

Owner:BEIJING INST OF SPACE LAUNCH TECH +1

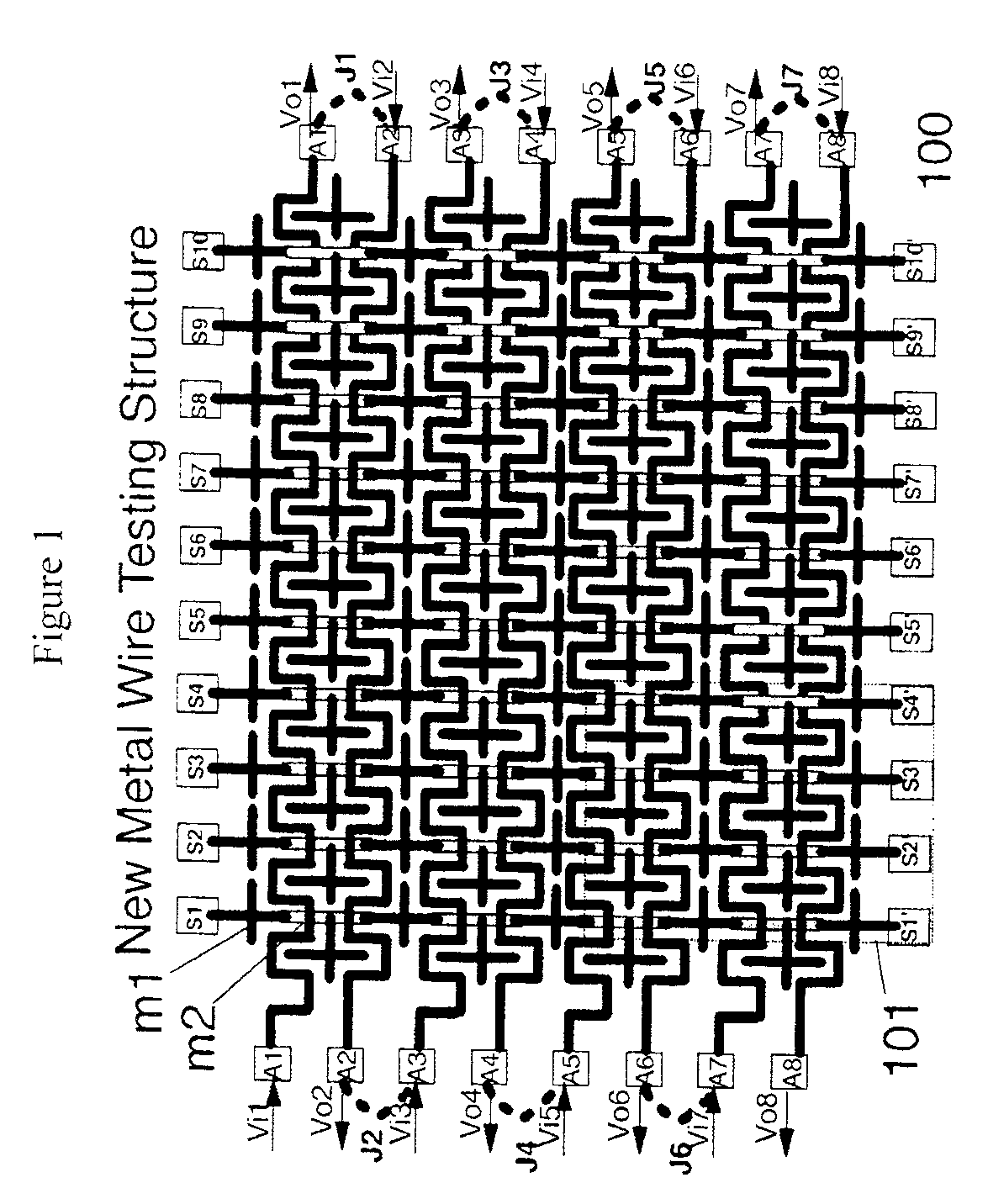

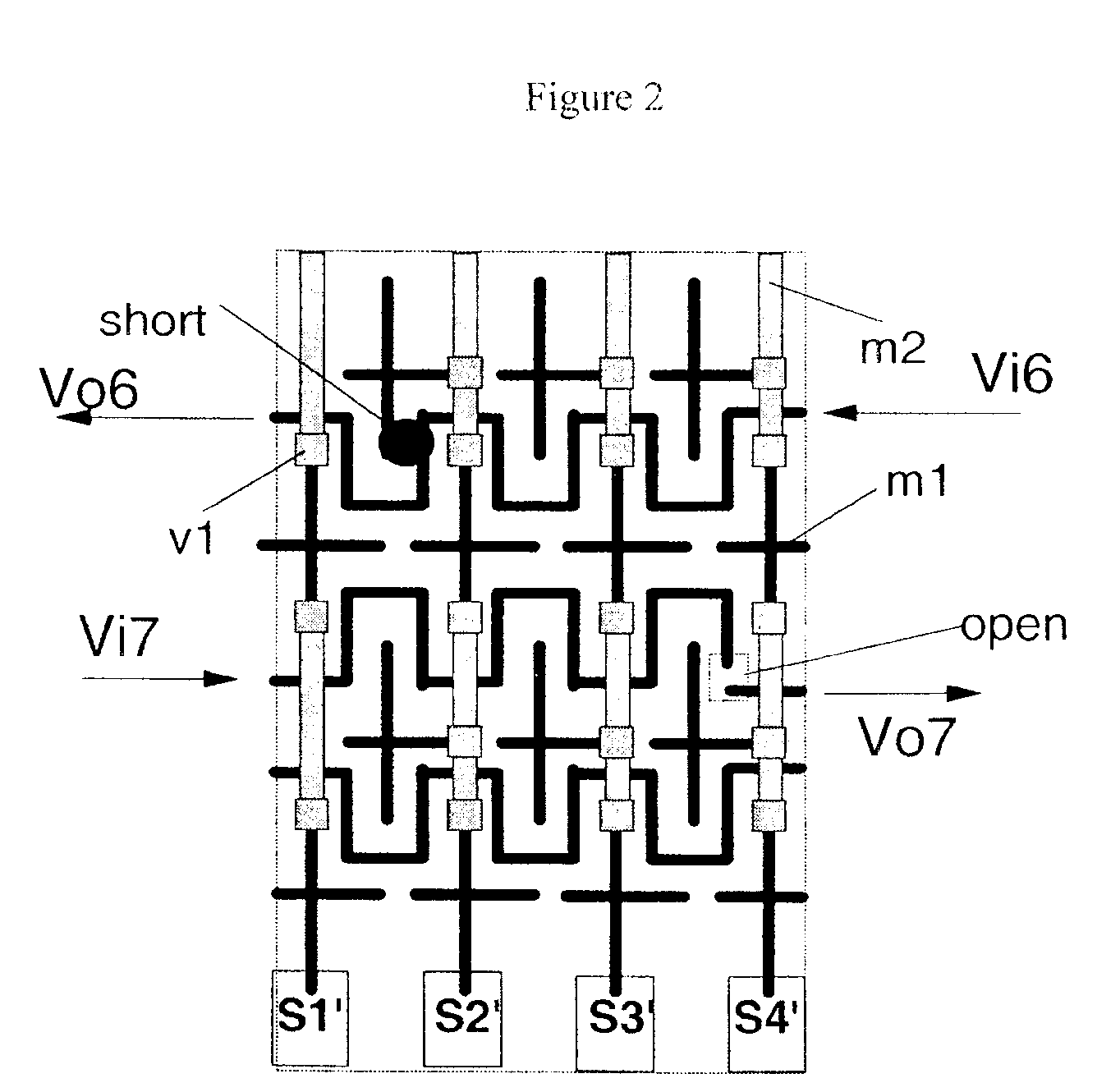

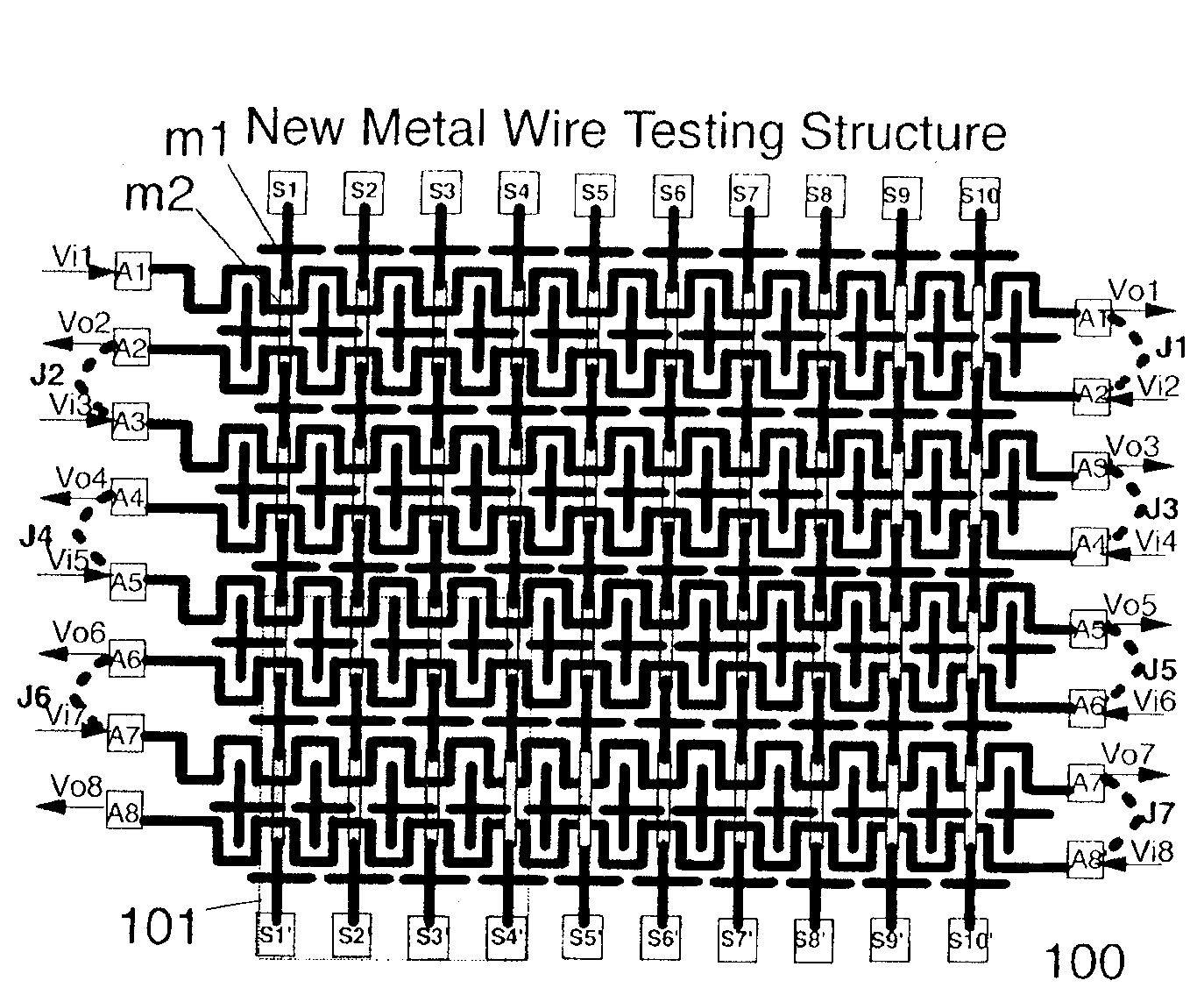

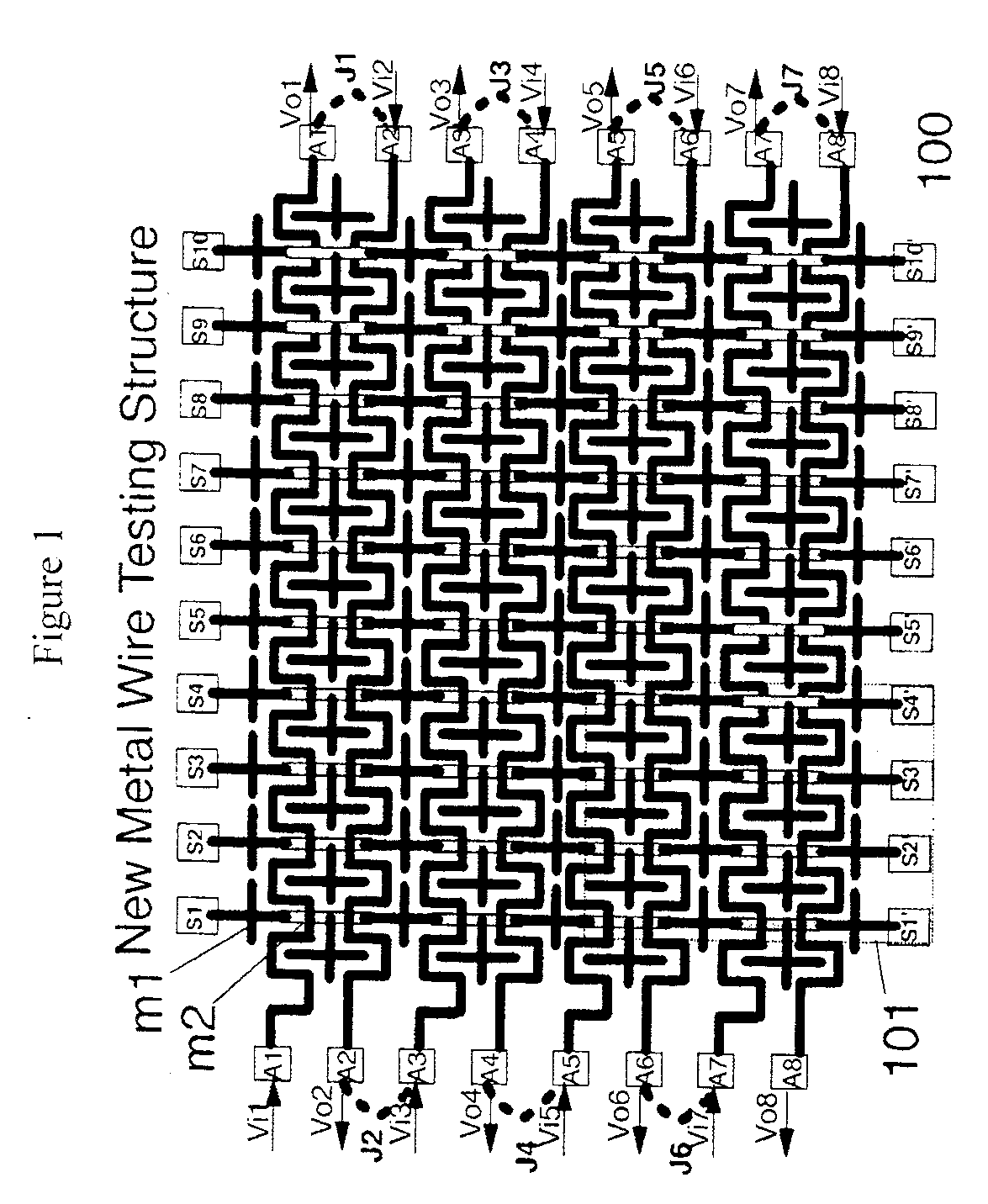

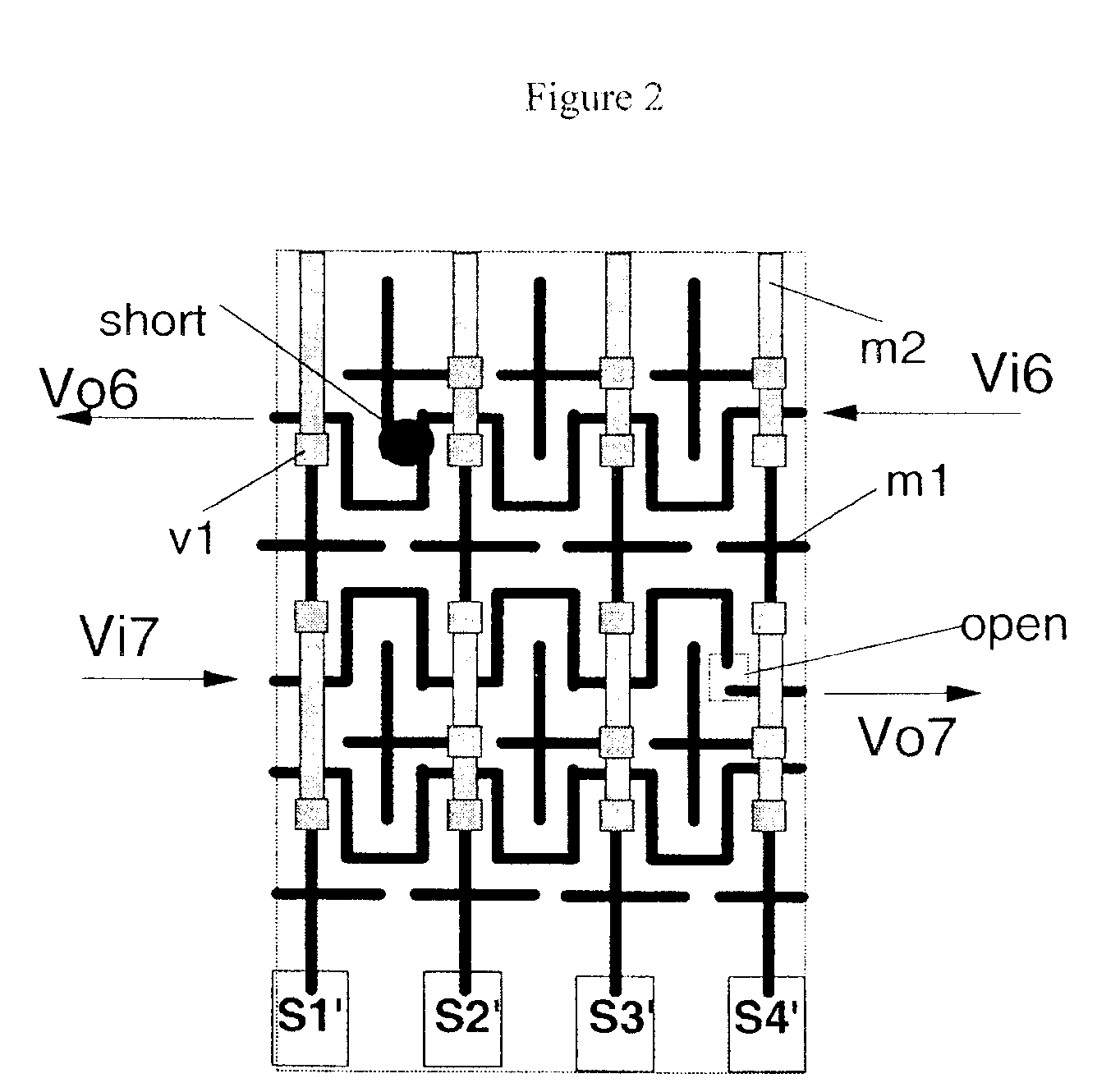

Addressable hierarchical metal wire test methodology

InactiveUS7749778B2Low costSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsElectrical resistance and conductanceEngineering

A method of monitoring and testing electro-migration and time dependent dielectric breakdown includes forming an addressable wiring test array, which includes a plurality or horizontally disposed metal wiring and a plurality of segmented, vertically disposed probing wiring, performing a single row continuity / resistance check to determine which row of said metal wiring is open, performing a full serpentine continuity / resistance check, and determining a position of short defects.

Owner:GLOBALFOUNDRIES INC

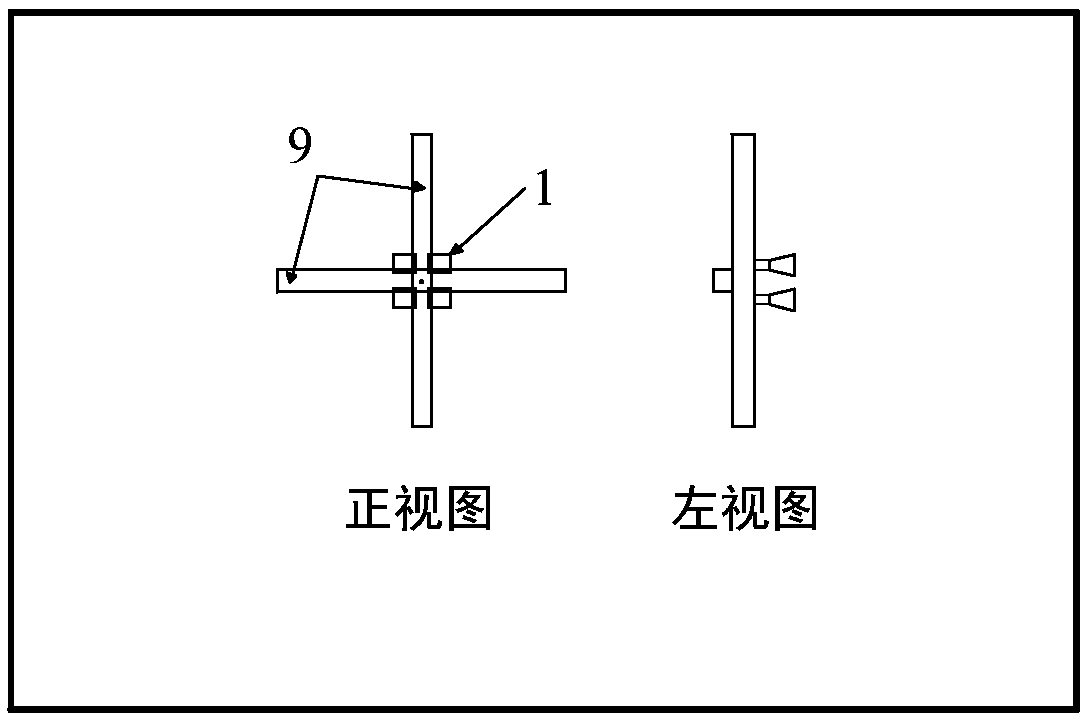

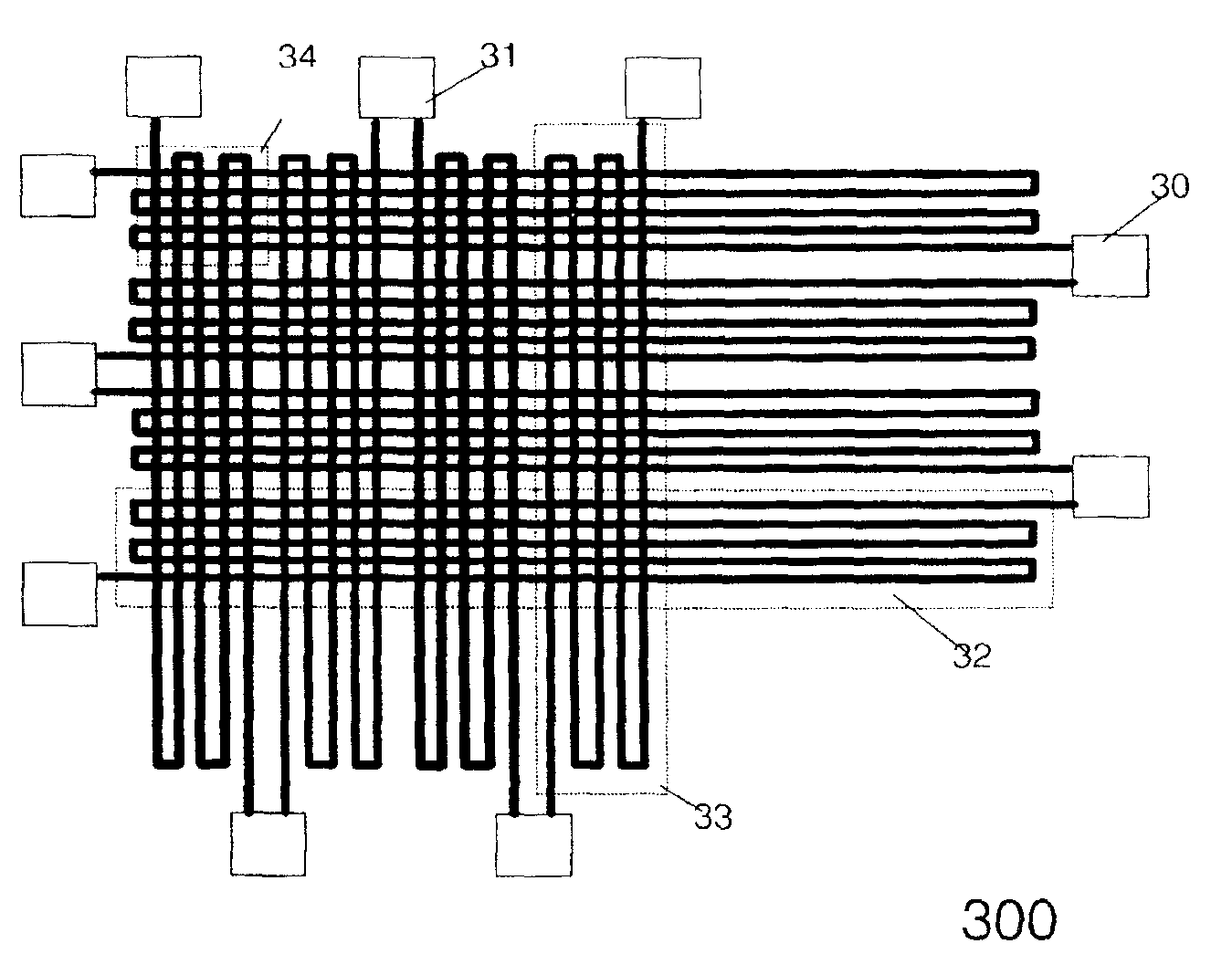

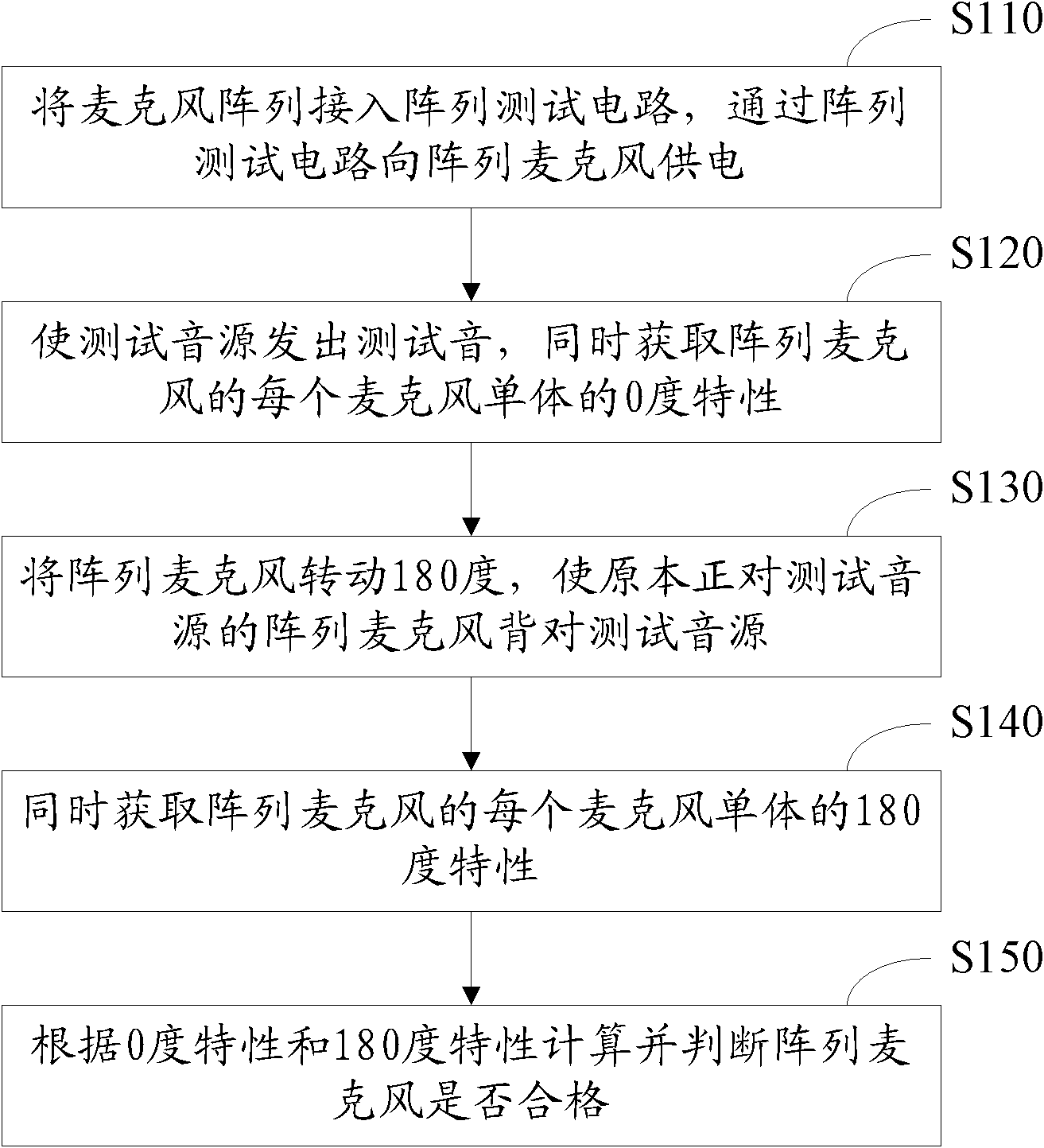

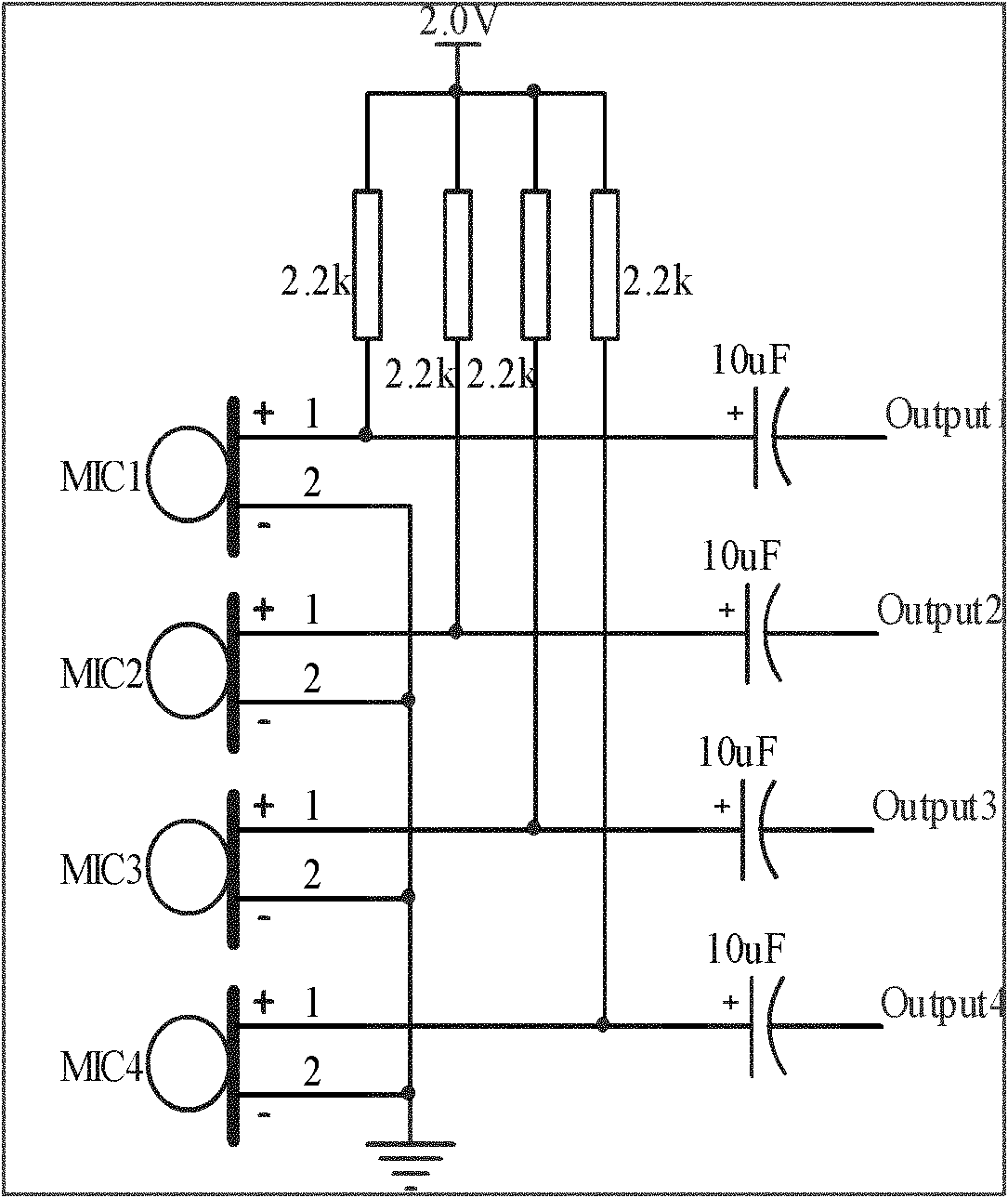

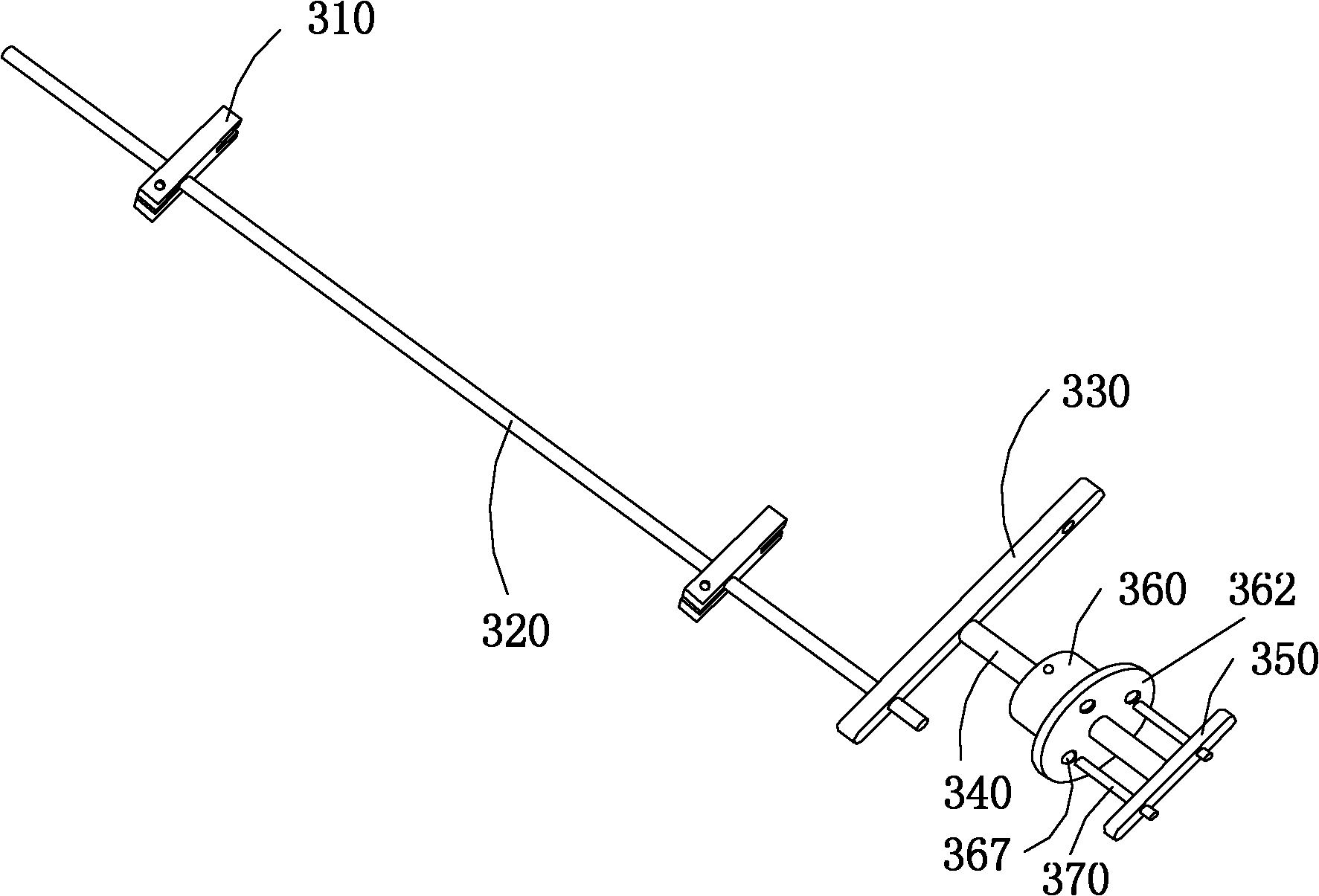

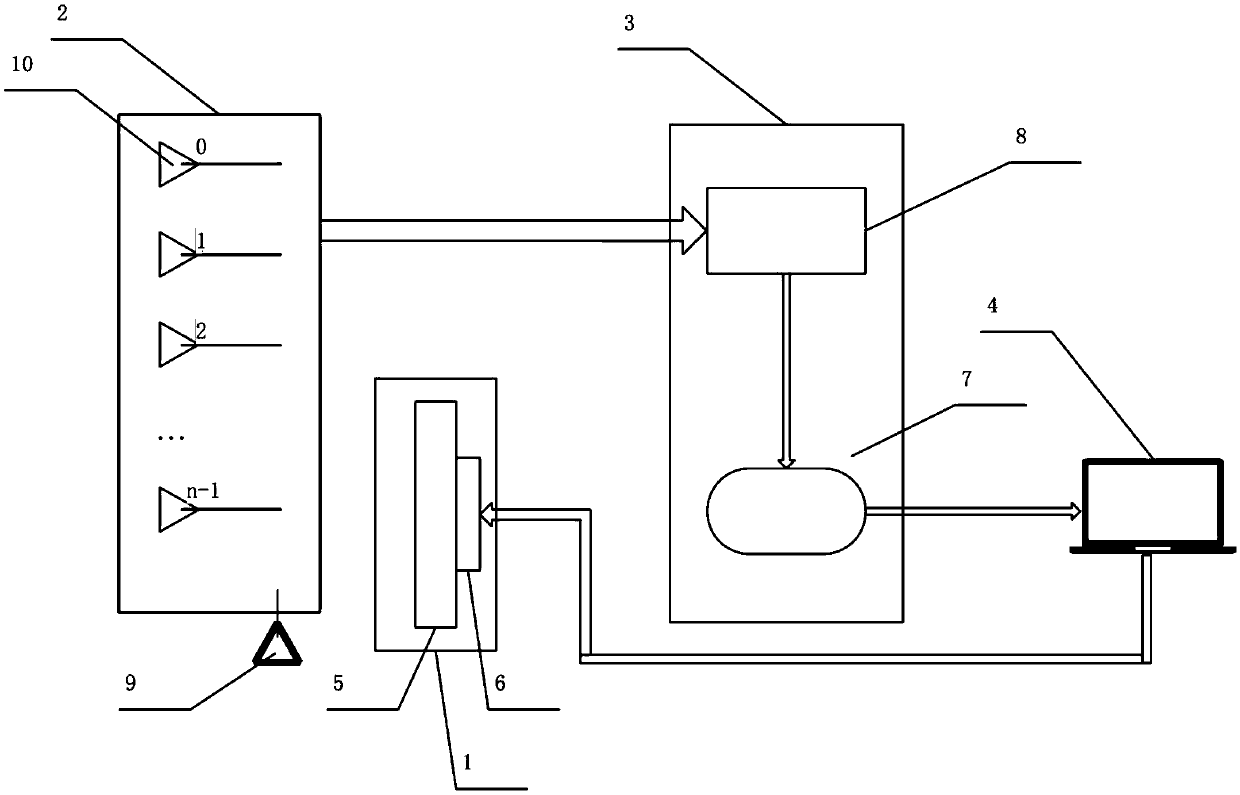

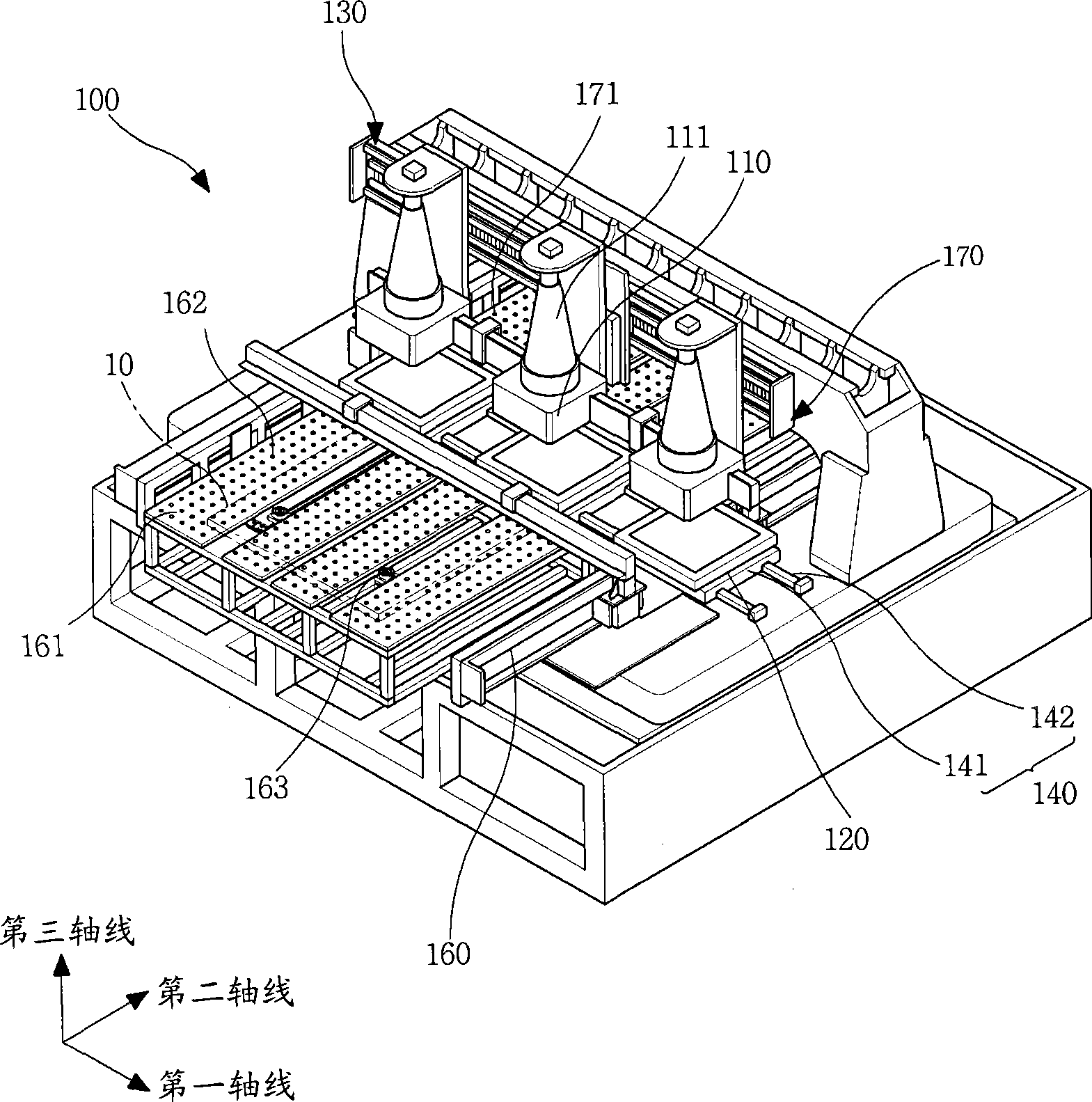

Method and system for testing array microphone and rotating device

The invention relates to a method for testing an array microphone. The method comprises the following steps of: accessing a microphone array to an array test circuit, and supplying electricity to the array microphone by using the array test circuit; making a test tone source give off a test tone, and acquiring 0-degree characteristic of each microphone monomer of the array microphone at the same time; rotating the array microphone 180 degrees to ensure that the array microphone facing the test tone source originally turns back to the test tone source; acquiring the 180-degree characteristic of each microphone monomer of the array microphone at the same time; and calculating, and judging whether the microphone is qualified according to the 0-degree characteristic and the 180-degree characteristic. The invention also relates to a system for testing the array microphone and a rotating device. Multi-channel synchronous input and output are realized, the array microphone is tested under the condition of not sequentially replacing microphone monomers, efficiency is high and test escape and false test are avoided. The unintuitive electroacoustic performance test is also automatically finished by a program so that the manual calculation is not needed and the confidence is high. The method and the device for testing the array microphone and the rotating device make the large-batch audio test possible.

Owner:SHENZHEN HORN AUDIO

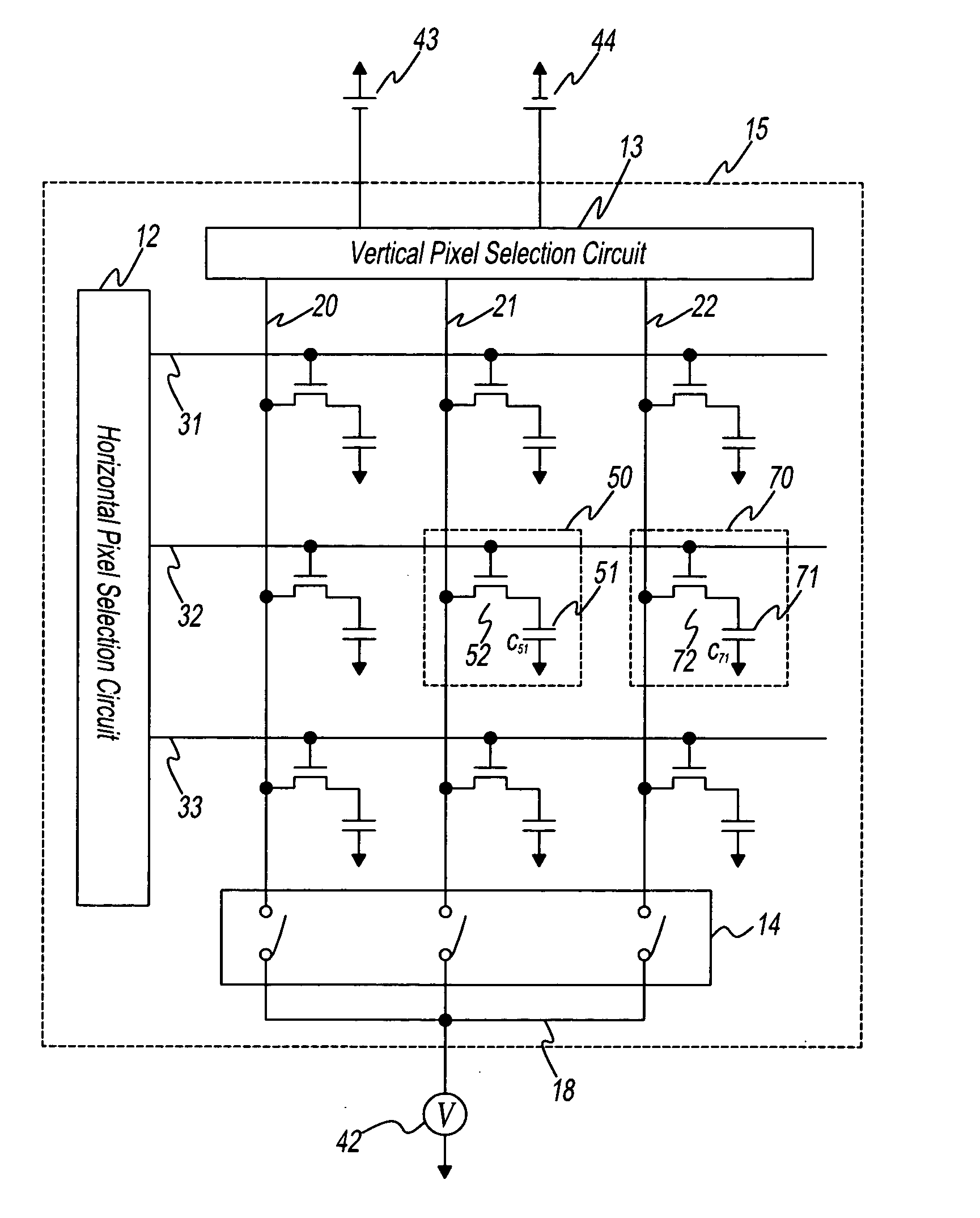

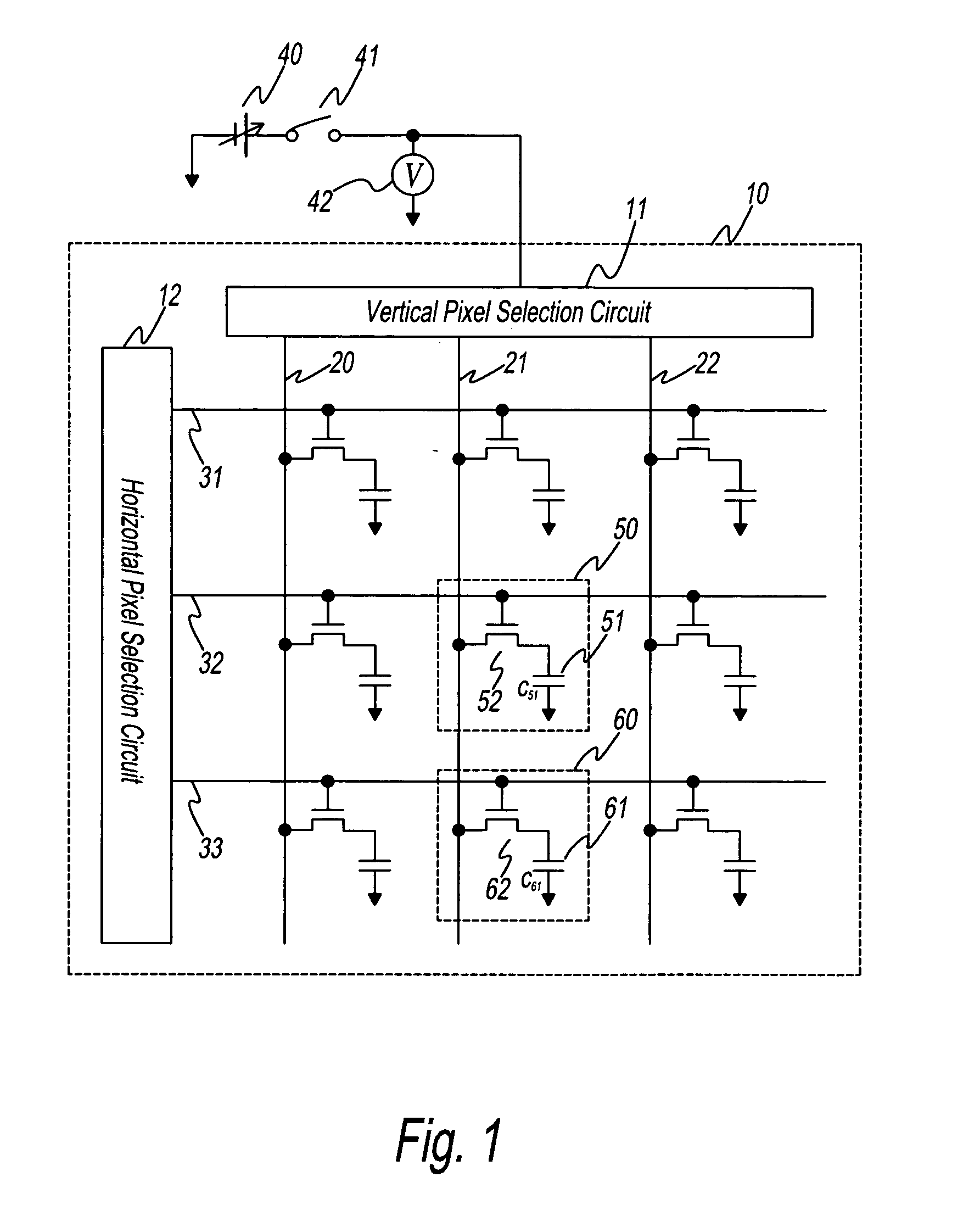

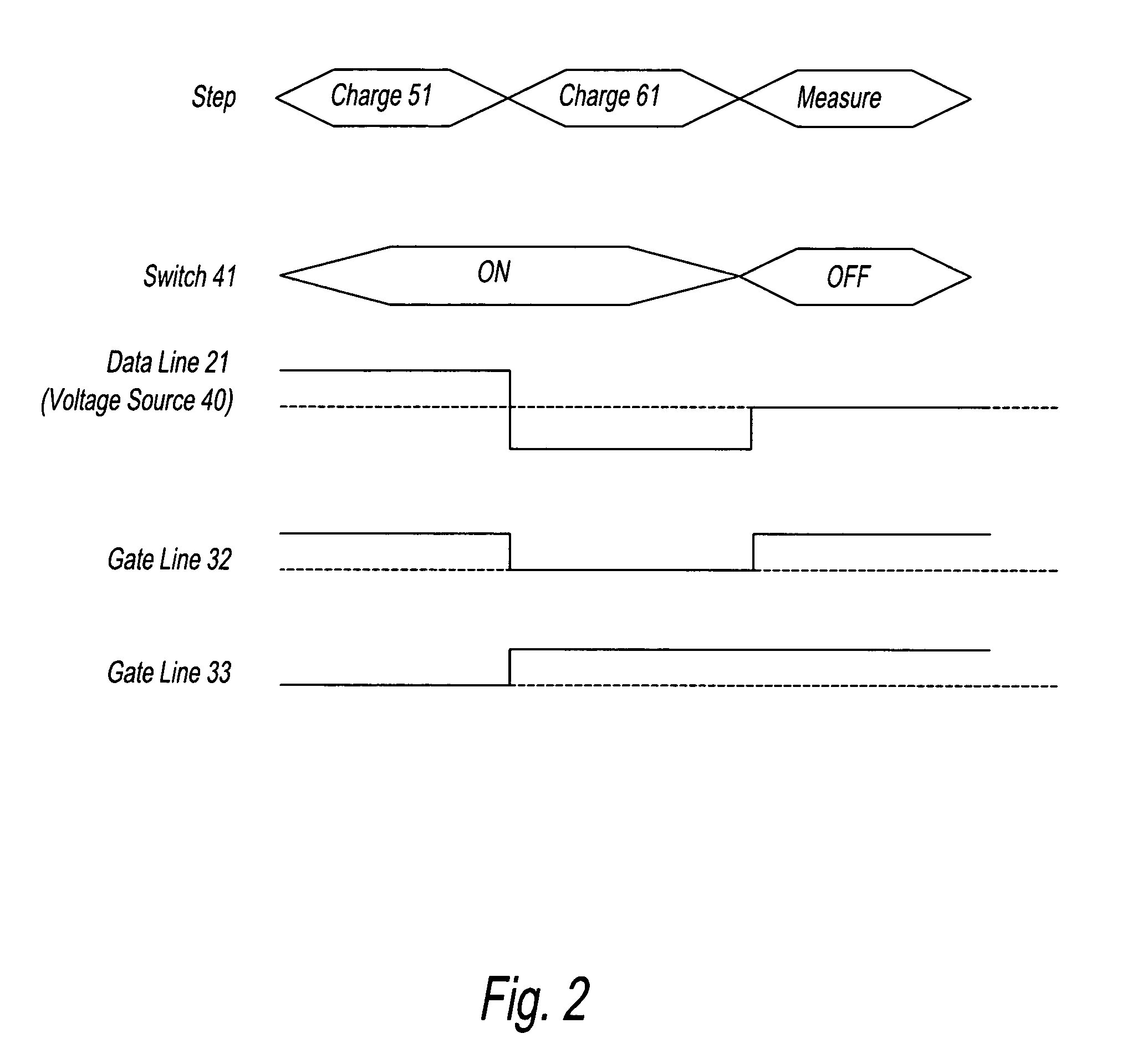

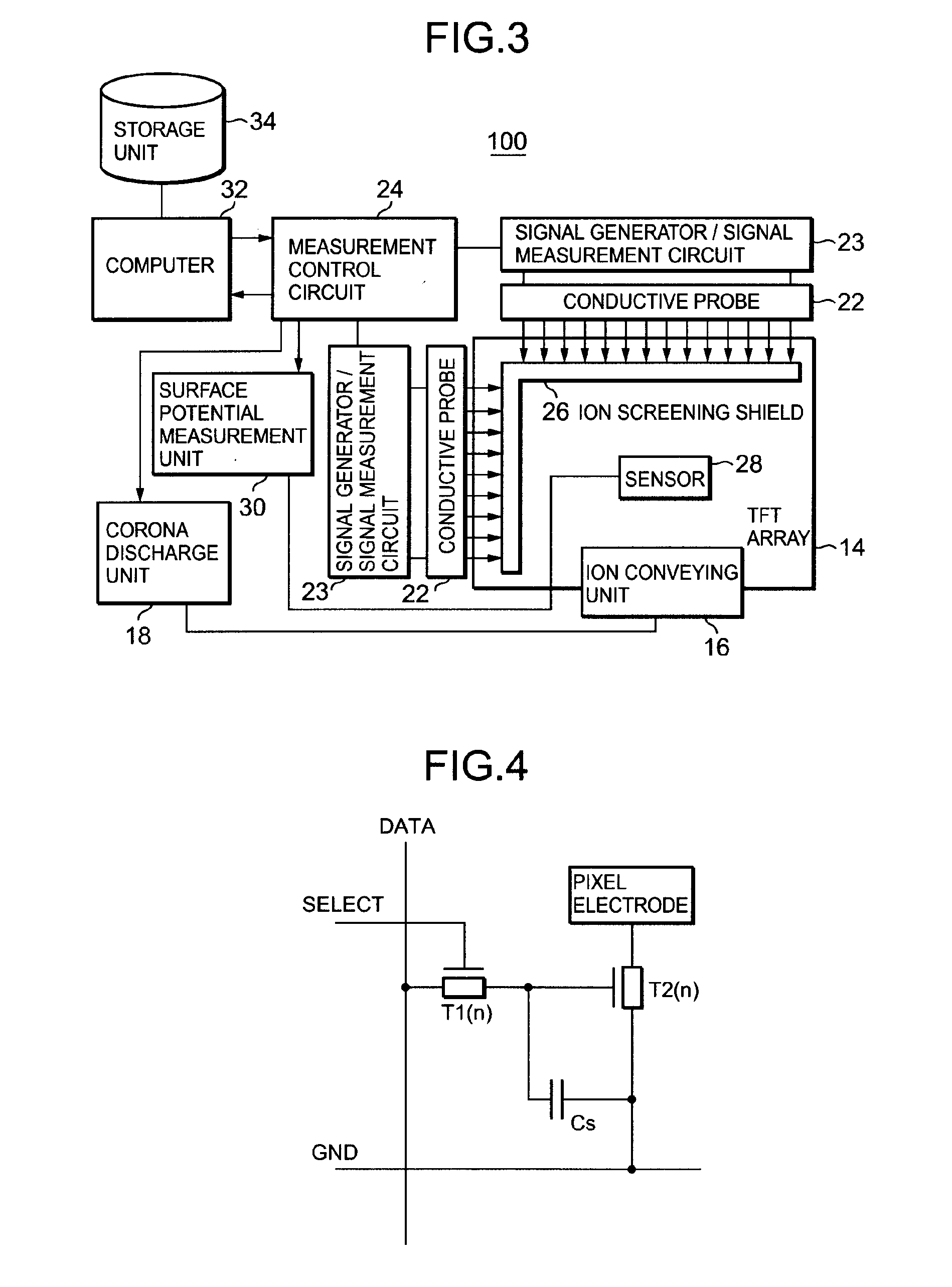

Method for testing a TFT array

InactiveUS20050206404A1Shorten the timeShorten test timeCurrent/voltage measurementStatic indicating devicesTest arrayComputer science

A method for testing a TFT array that comprises one or a plurality of first pixels including capacitors connected to one terminal of pixel selection switches, one or a plurality of second pixels including capacitors connected to one terminal of pixel selection switches, and data lines connected to the other terminals of the pixel selection switches of the first pixels and the other terminals of the pixel selection switches of the second pixels, wherein the method for testing comprises a step for charging the capacitors of the first pixels to a first voltage, a step for charging the capacitors of the second pixels to a second voltage, a step for turning on both the pixel selection switches of the first pixels and the pixel selection switches of the second pixels, and a step for measuring either one or both of the voltage of a data line or the charge flowing through the data line.

Owner:AGILENT TECH INC

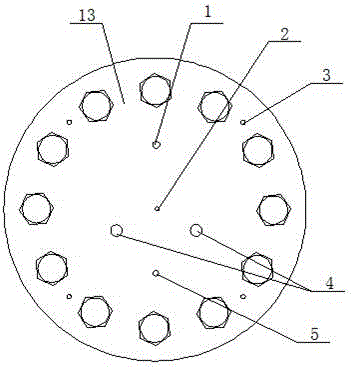

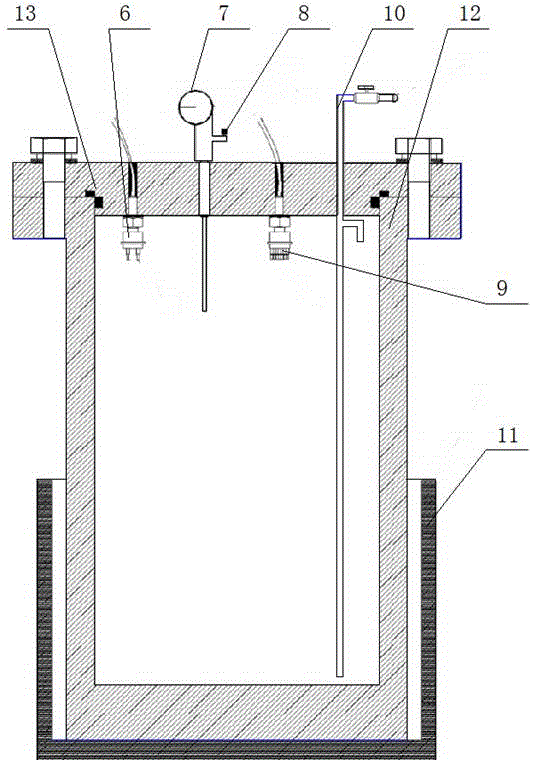

Device and method for testing local corrosion in deep-sea simulation environments

InactiveCN106501168ASimple structureEasy to installWeather/light/corrosion resistanceButt jointAuxiliary electrode

The invention provides a device and a method for testing local corrosion in deep-sea simulation environments, and belongs to the field of simulation test equipment for deep-sea environments. The device comprises a test cabin, a test cabin cover and an electrode assembly. The electrode assembly is based on a three-electrode system and is fixed onto the test cabin cover by the aid of an electrode water-tight connector, the electrode water-tight connector is provided with a wire-wire butt-joint needle bed, a working electrode is an electrode array, the electrode array comprises a plurality of micro-electrodes, and the micro-electrodes are matched with a working electrode water-tight connector; a reference electrode is fixedly connected onto a plug-in cable matched with a reference electrode water-tight connector, and an auxiliary electrode is fixedly connected onto a plug-in cable matched with an auxiliary electrode water-tight connector. The method is based on the device. The device and the method have the advantages that the device is simple in structure, convenient to mount and high in universality, requirements on testing array electrodes in simulation deep-sea high-pressure environments can be met, and-sealing requirements of test environments can be met; the device and the method can be used for research on local corrosion behavior and mechanisms in the deep-sea simulation environments.

Owner:725TH RES INST OF CHINA SHIPBUILDING INDAL CORP

Addressable hierarchical metal wire test methodology

InactiveUS20080160656A1Low costSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsElectrical resistance and conductanceEngineering

A method of monitoring and testing electro-migration and time dependent dielectric breakdown includes forming an addressable wiring test array, which includes a plurality or horizontally disposed metal wiring and a plurality of segmented, vertically disposed probing wiring, performing a single row continuity / resistance check to determine which row of said metal wiring is open, performing a full serpentine continuity / resistance check, and determining a position of short defects.

Owner:GLOBALFOUNDRIES INC

Automatic positioning and calibrating device for infrared modulation photoluminescence (PL) bi-dimensional imaging light path

ActiveCN104181131ASuitable for in-plane spatial uniformity detectionImprove efficiencyAnalysis by material excitationPhotoluminescenceLight spot

The invention discloses an automatic positioning and calibrating device for an infrared modulation photoluminescence (PL) bi-dimensional imaging light path. The device comprises a long-time stable working laser source, an isometric long-focus light focusing module, a perpendicular light axis calibrating system, a focal plane calibrating system and a feedback self-calibrating control unit. The positions of relevant light instruments are mainly calibrated according to a position drift rate of an interference pattern formed by a Fresnel bi-prism on a high-precision complementary metal oxide semiconductor photoelectric element array, and a charge coupling element laser test array is used for measuring the size of light spots with micron precision. The device has the characteristics of high stability, high sensitivity, high automation degree and the like, and is effective technical guarantee for researching narrow bandage semiconductors comprising large-area infrared detector area array materials.

Owner:上海济物光电技术有限公司

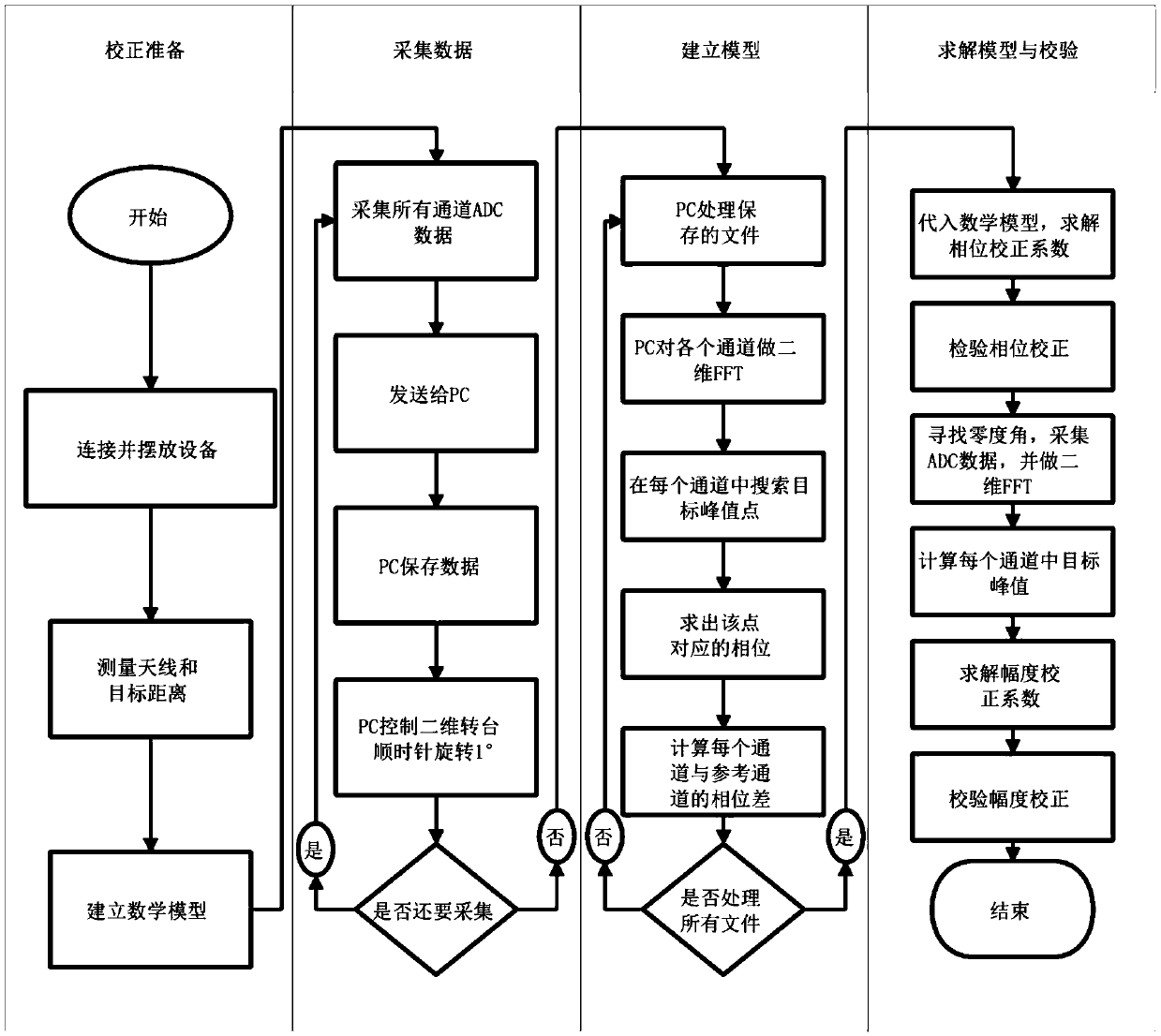

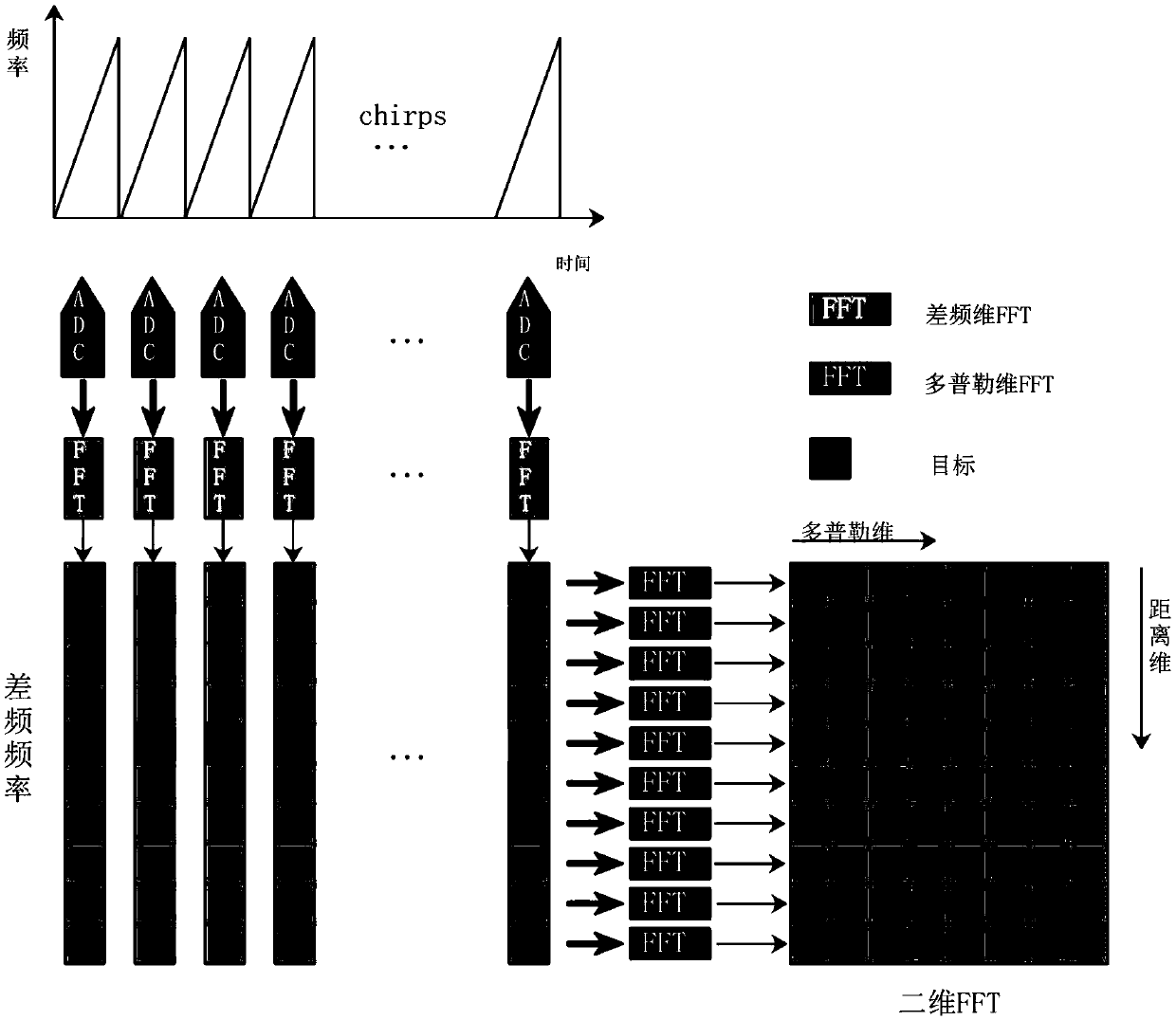

Vehicle-mounted millimeter wave radar multi-channel array antenna amplitude and phase correction device and method

ActiveCN109633650ASimple methodHigh degree of automationRadio wave reradiation/reflectionPhase correctionWave detection

The invention discloses a vehicle-mounted millimeter wave radar multi-channel array antenna amplitude and phase correction device and method and belongs to the advanced driving auxiliary system fieldand the millimeter wave detection technology field. The device comprises a controllable rotation turntable module, a tested array antenna, a digital processing module, and a computer. The digital processing module comprises a network interface module and an ADC sampling module. The tested array antenna receives a target echo signal. After AD sampling, the sampling signal sequence of each channel is acquired. Two-dimensional FFT transformation is performed to solve the phase and amplitude of a target in each channel. The phase and amplitude are substituted into an established amplitude and phase correction mathematical model, and the amplitude and phase characteristics of all channels can be corrected to be consistent. Data can be automatically collected, channel correction can be performed, zero angle does not need to be searched before correction, and the device and the method are suitable for a equal-distance array antenna and a non-equidistance array antenna.

Owner:NANJING UNIV OF SCI & TECH

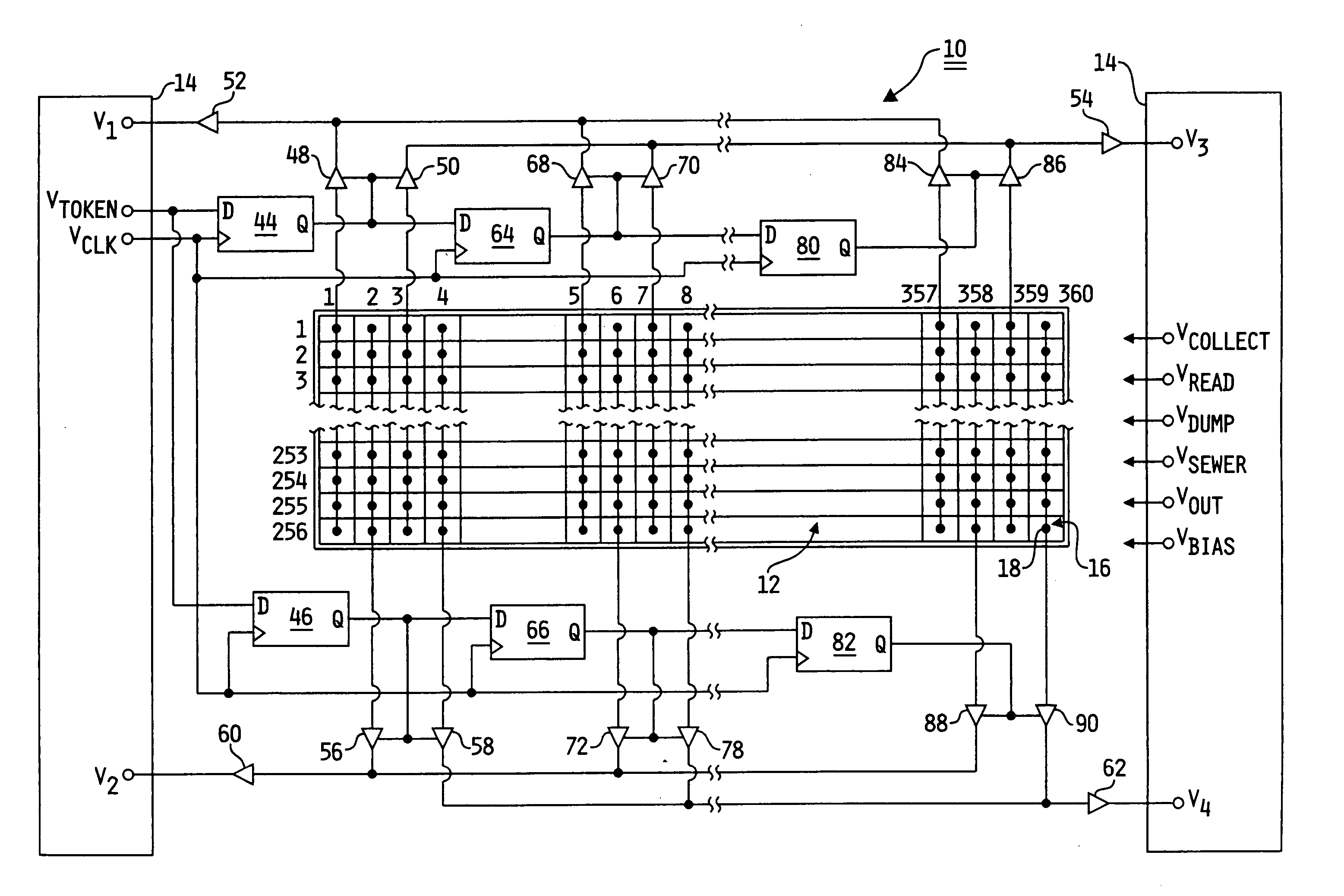

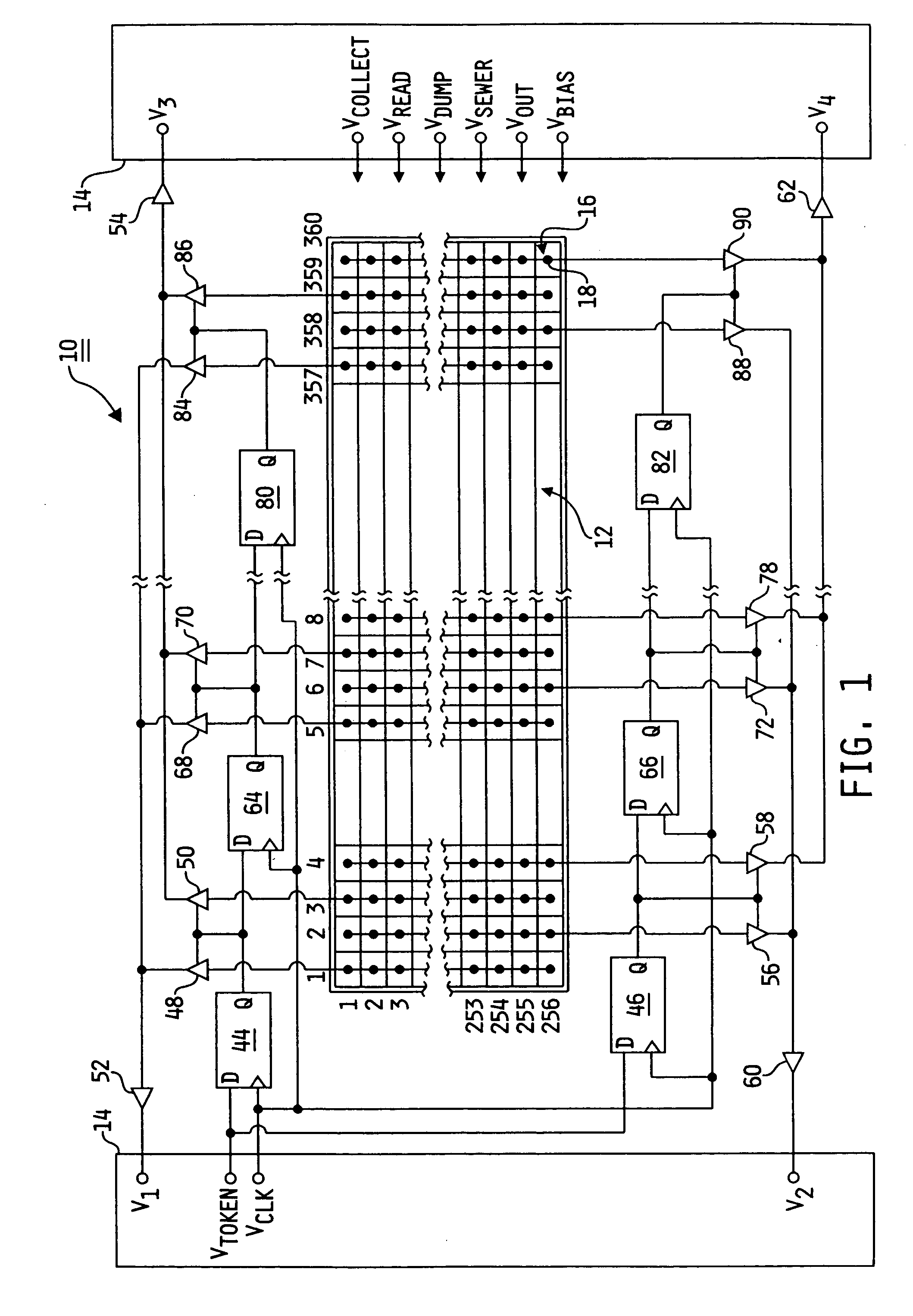

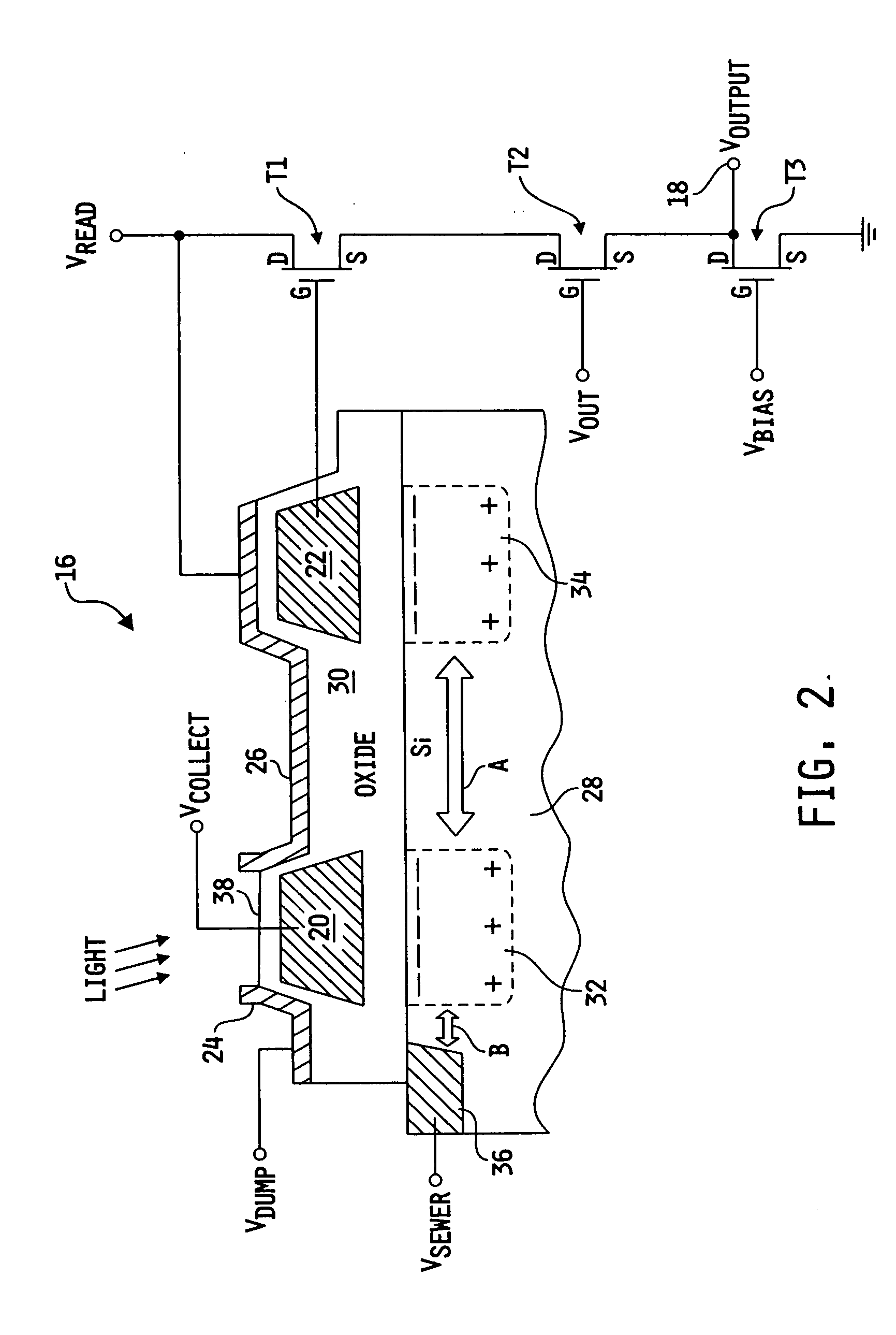

Self testing CMOS imager chip

ActiveUS20050184218A1Reduce Fixed Pattern NoiseEasy to operateTelevision system detailsTelevision system scanning detailsCMOSCharge injection

A self testing CMOS imager chip includes a controller which outputs a sewer signal, a dump signal, a collect signal, and a read signal, and a pixel array connected to the controller including a plurality of pixels arranged in an array of rows and columns, each pixel having a collect gate disposed adjacent a collect well for receiving a charge in response to application of the collect signal to the collect gate, a sewer for injecting a charge into the collect well in response to the concurrent application of the sewer signal to the sewer and the collect signal to the collect well, a read gate disposed adjacent a read well for receiving the injected charge from the collect well in response to application of the read signal to the read gate and the absence of the collect signal at the collect gate, and a transistor having a gate coupled to the read well, a source for receiving the read signal, and a drain coupled to an output node connected to the controller. The read signal is modulated by the injected charge at the gate of the transistor, thereby generating an injected output signal at the output node representing the injected charge. The controller, through read-out circuitry, comparing the injected output signal to an expected output signal to test the operation of each pixel of the array.

Owner:DELPHI TECH IP LTD

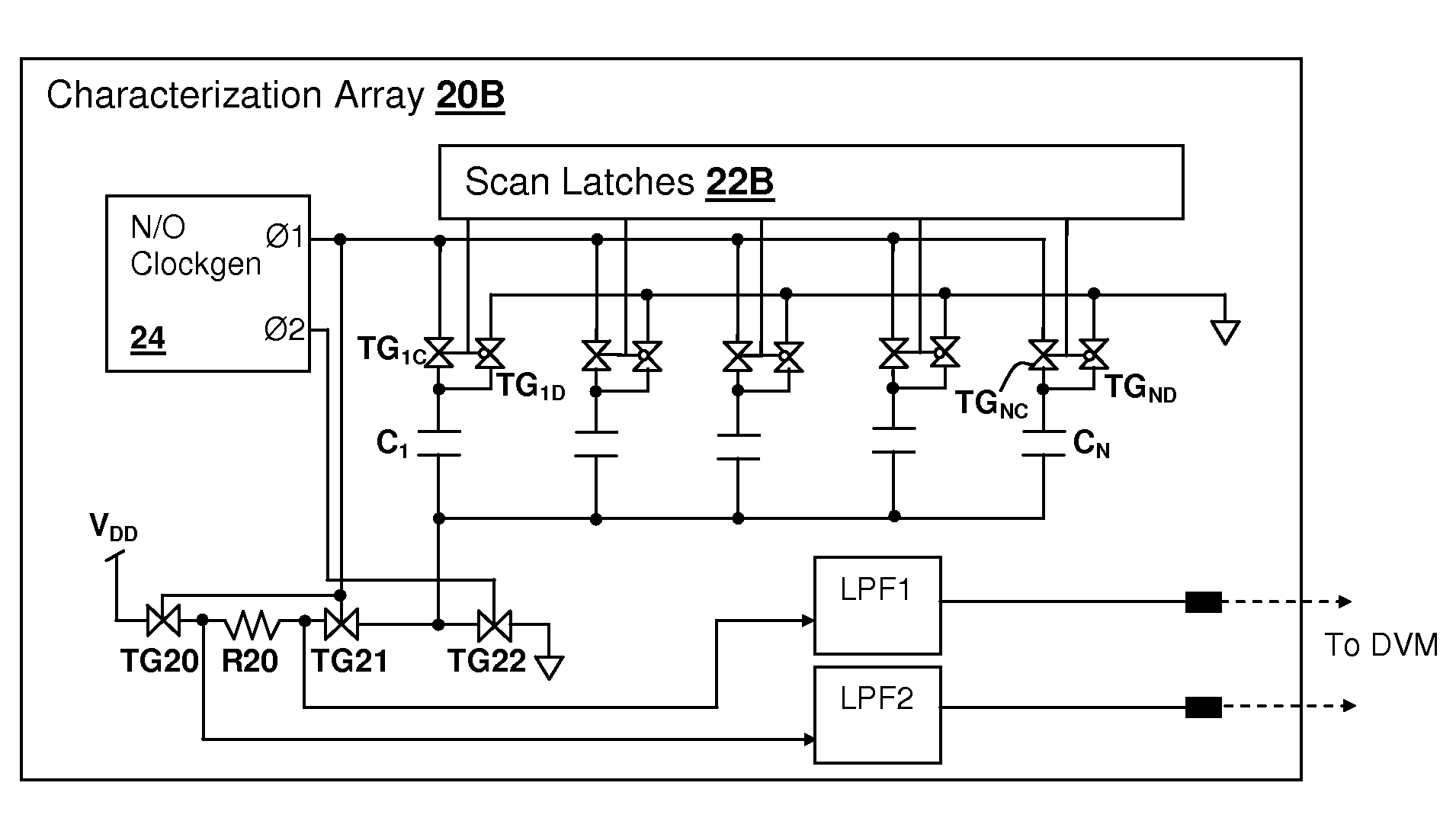

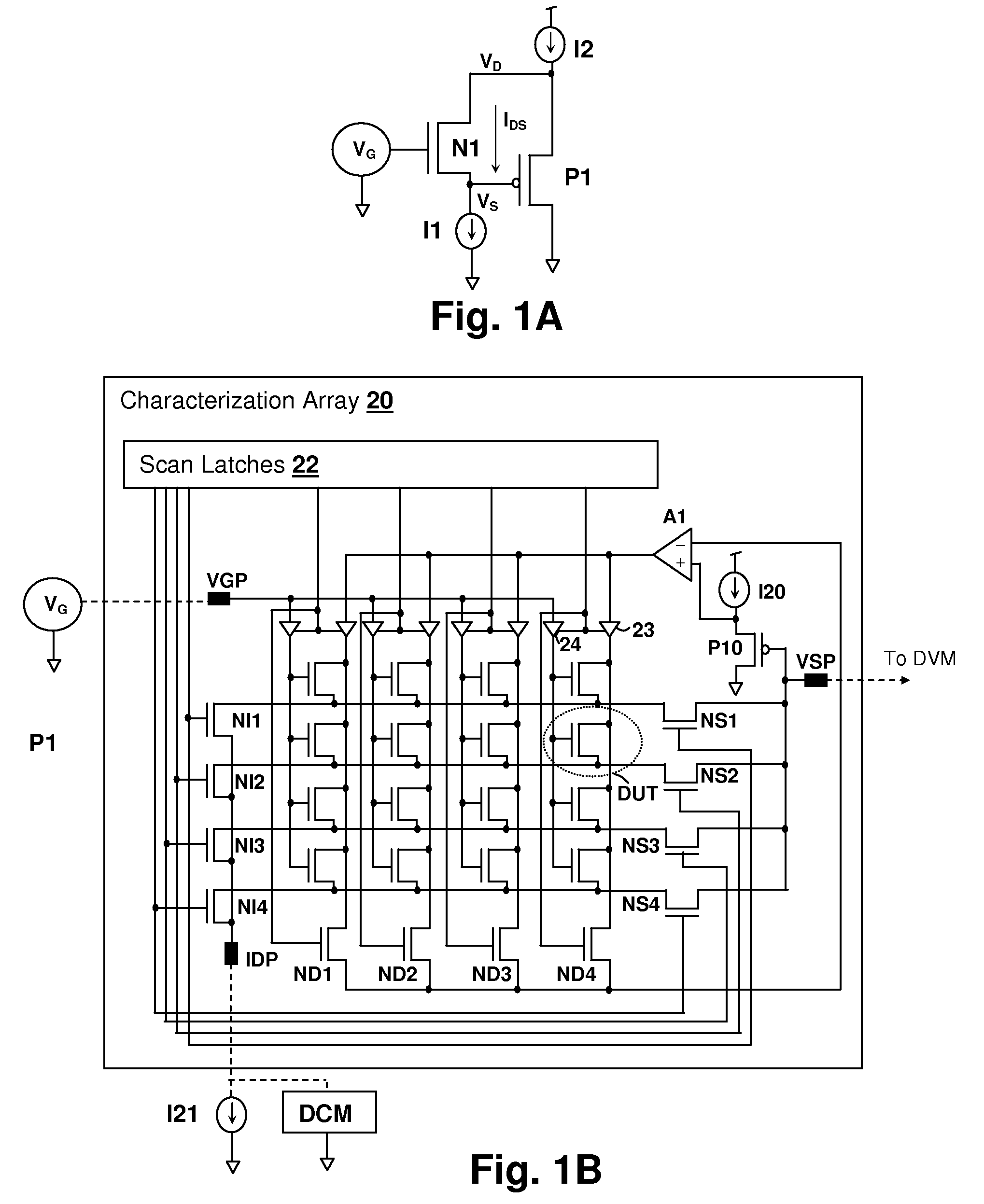

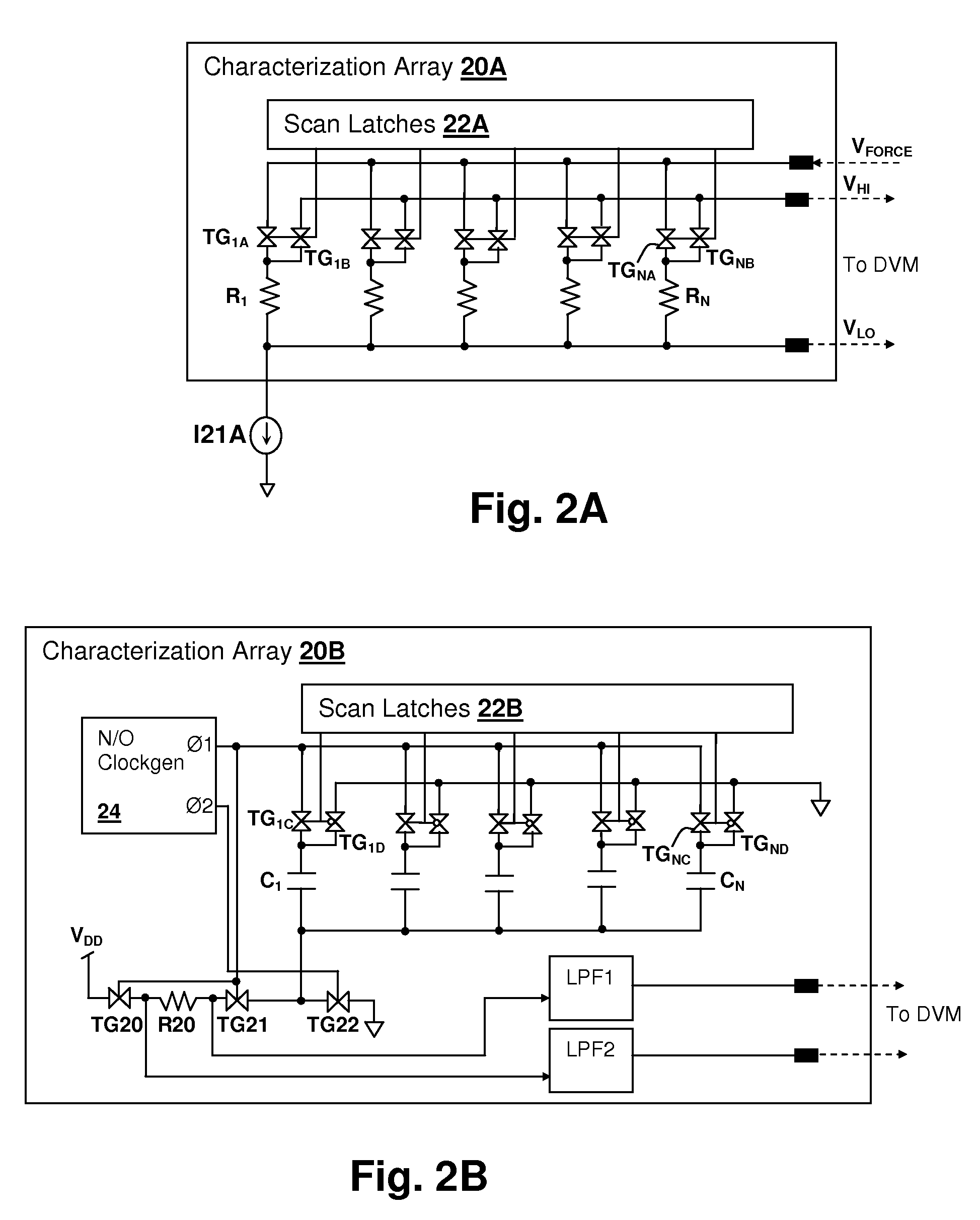

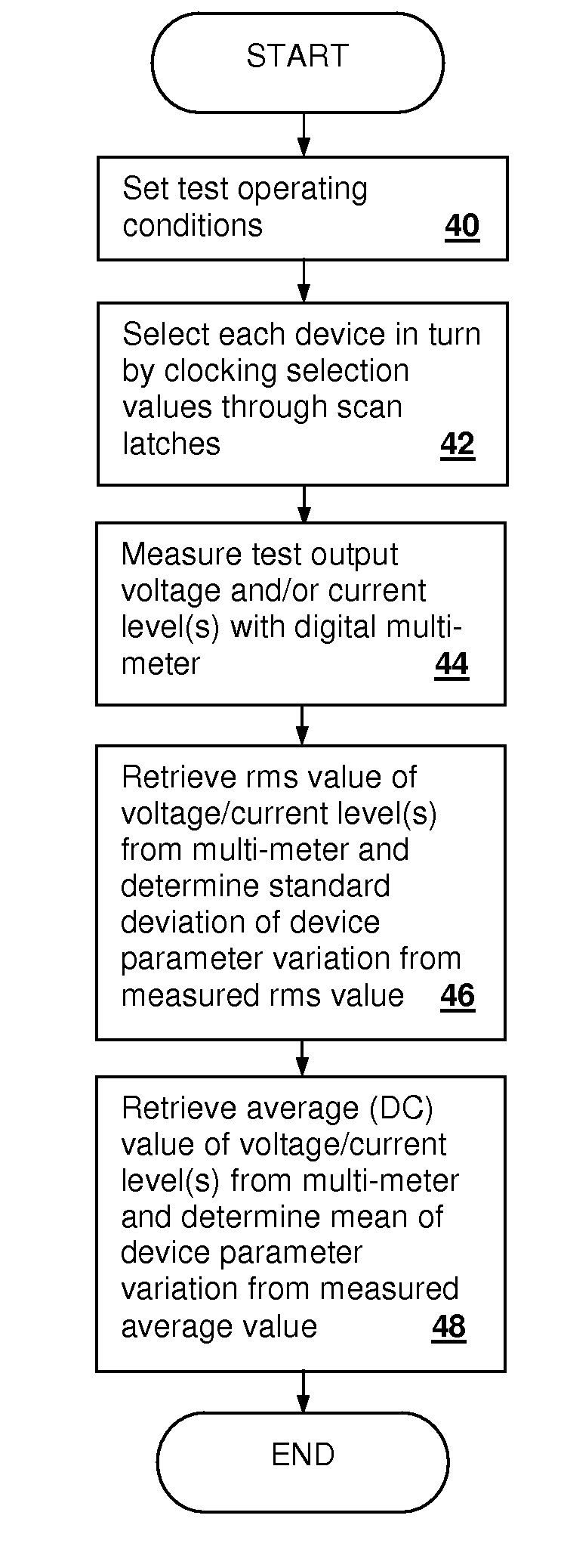

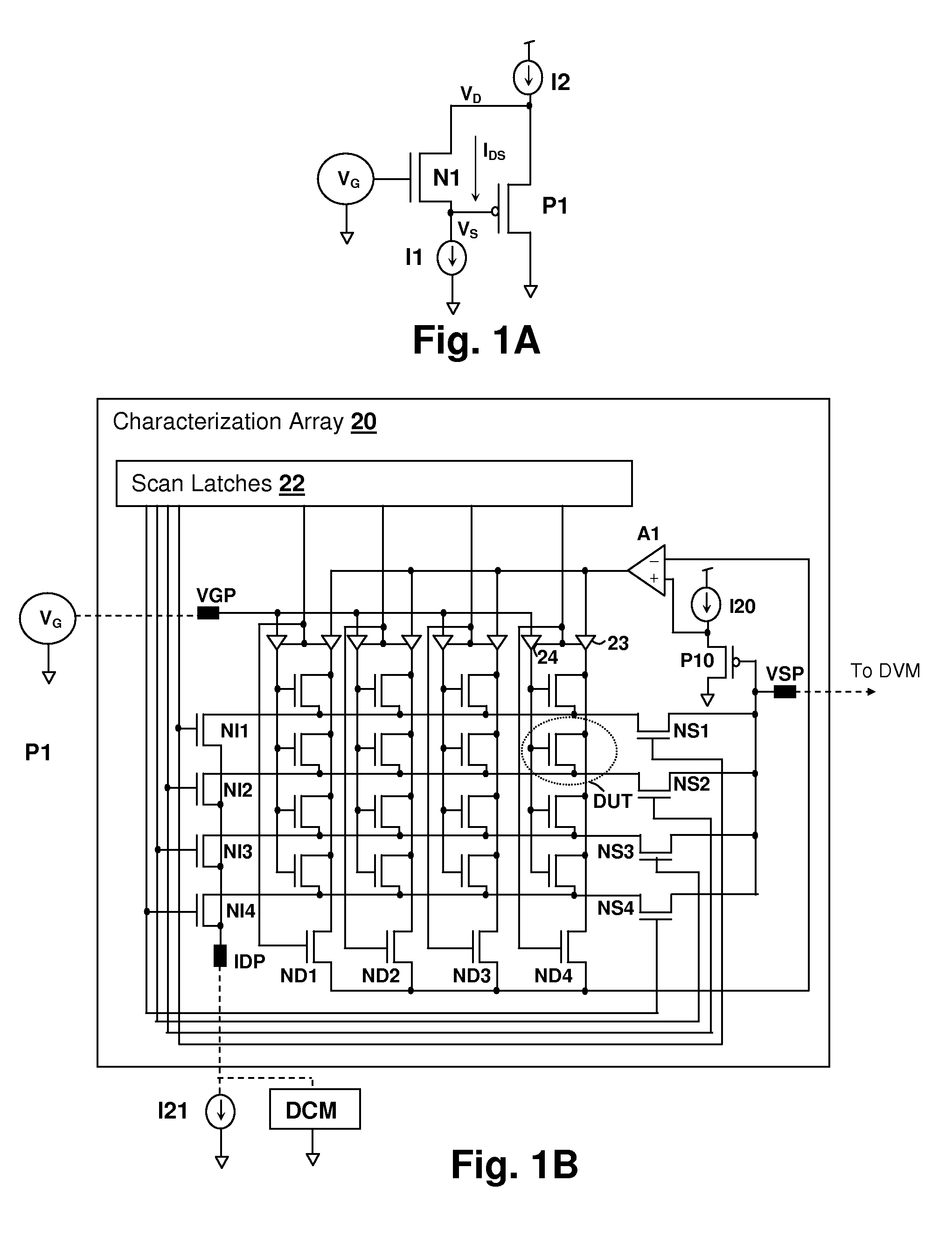

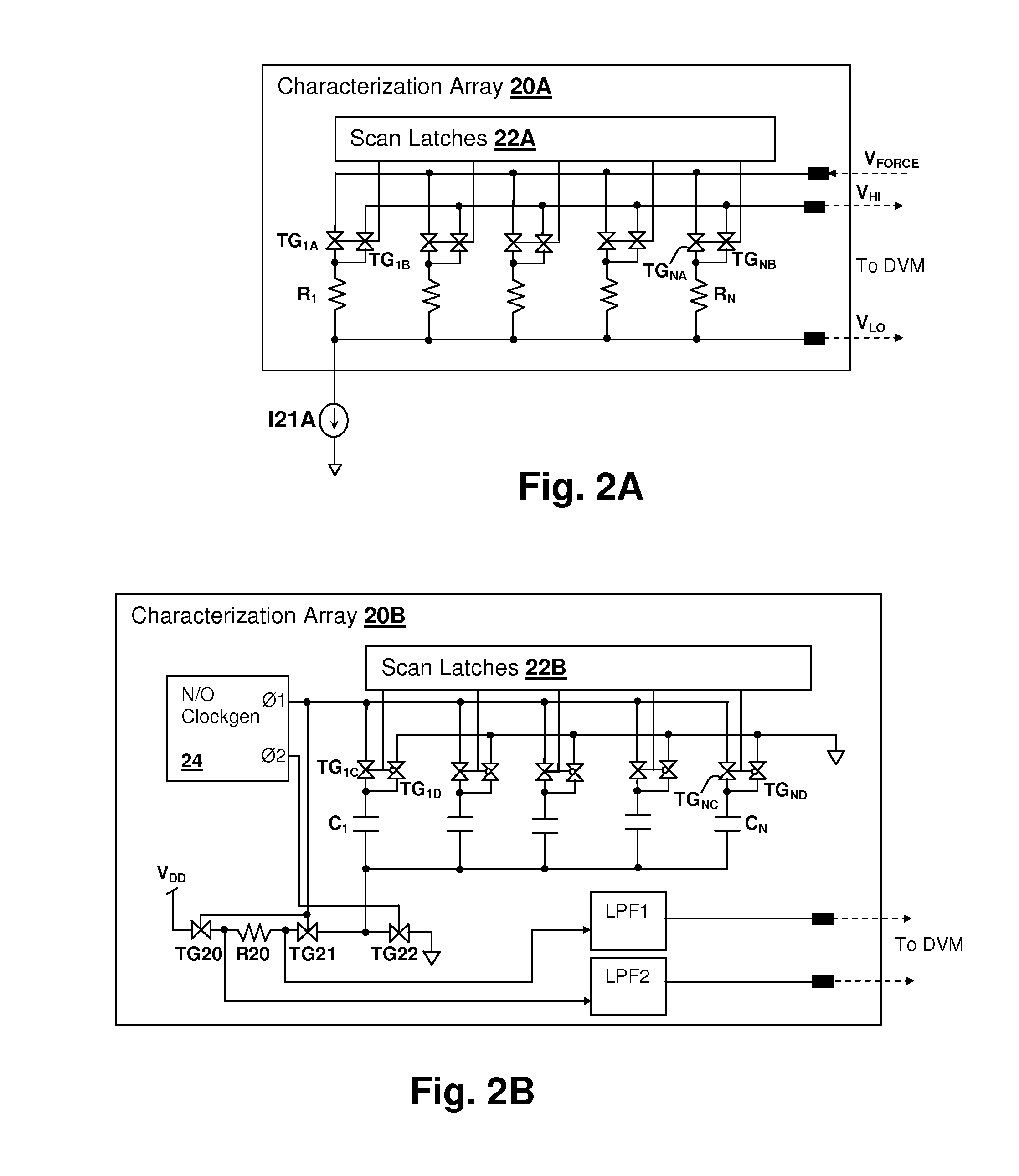

Characterization circuit for fast determination of device capacitance variation

A test circuit for fast determination of device capacitance variation statistics provides a mechanism for determining process variation and parameter statistics using low computing power and readily available test equipment. A test array having individually selectable devices is stimulated under computer control to select each of the devices sequentially. A test output from the array provides a current or voltage that dependent on a particular device parameter. The sequential selection of the devices produces a voltage or current waveform, characteristics of which are measured using a digital multi-meter that is interfaced to the computer. The rms value of the current or voltage at the test output is an indication of the standard deviation of the parameter variation and the DC value of the current or voltage is an indication of the mean value of the parameter.

Owner:IBM CORP

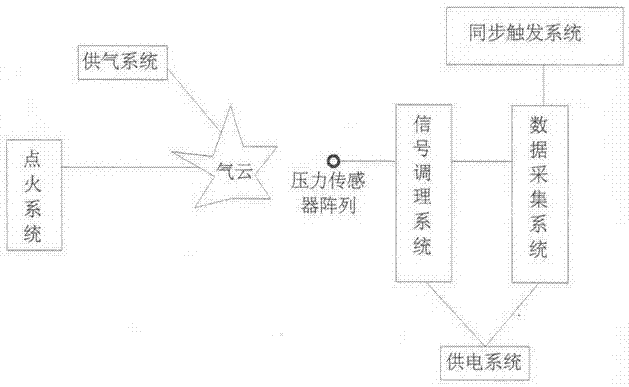

Test method of open space large-sized combustible gas cloud explosion three-dimensional overpressure field

The invention provides a test method of an open space large-sized combustible gas cloud explosion three-dimensional overpressure field. The method comprises a three-dimensional pressure sensor array establishment method, a pressure data acquisition method, a synchronous triggering method and a gas supply system establishment and combustible gas cloud forming method; and the open space large-sized combustible gas cloud explosion three-dimensional overpressure field consists of a three-dimensional pressure sensor array, a synchronous triggering system, a signal regulation system, a pressure data acquisition system, a power supply system and a gas supply system. A three-dimensional multipoint pressure sensor test array is established in multiple directions at different heights by surrounding a gas cloud center. Two pressure data acquisition ways, i.e., a pressure data self-acquisition way and a synchronous triggering pressure data acquisition way are adopted, and the field is synchronously triggered by the synchronous triggering system and an ignition apparatus. The gas supply system is used for forming combustible gas cloud at a certain height, an ignition ball shot by the ignition and shooting apparatus is used for igniting the combustible gas cloud to form the overpressure for test, so that data support is provided for inverting and reestablishing the three-dimensional overpressure field, and data evidence is provided for formulating a safety distance and standard.

Owner:PIPECHINA SOUTH CHINA CO +1

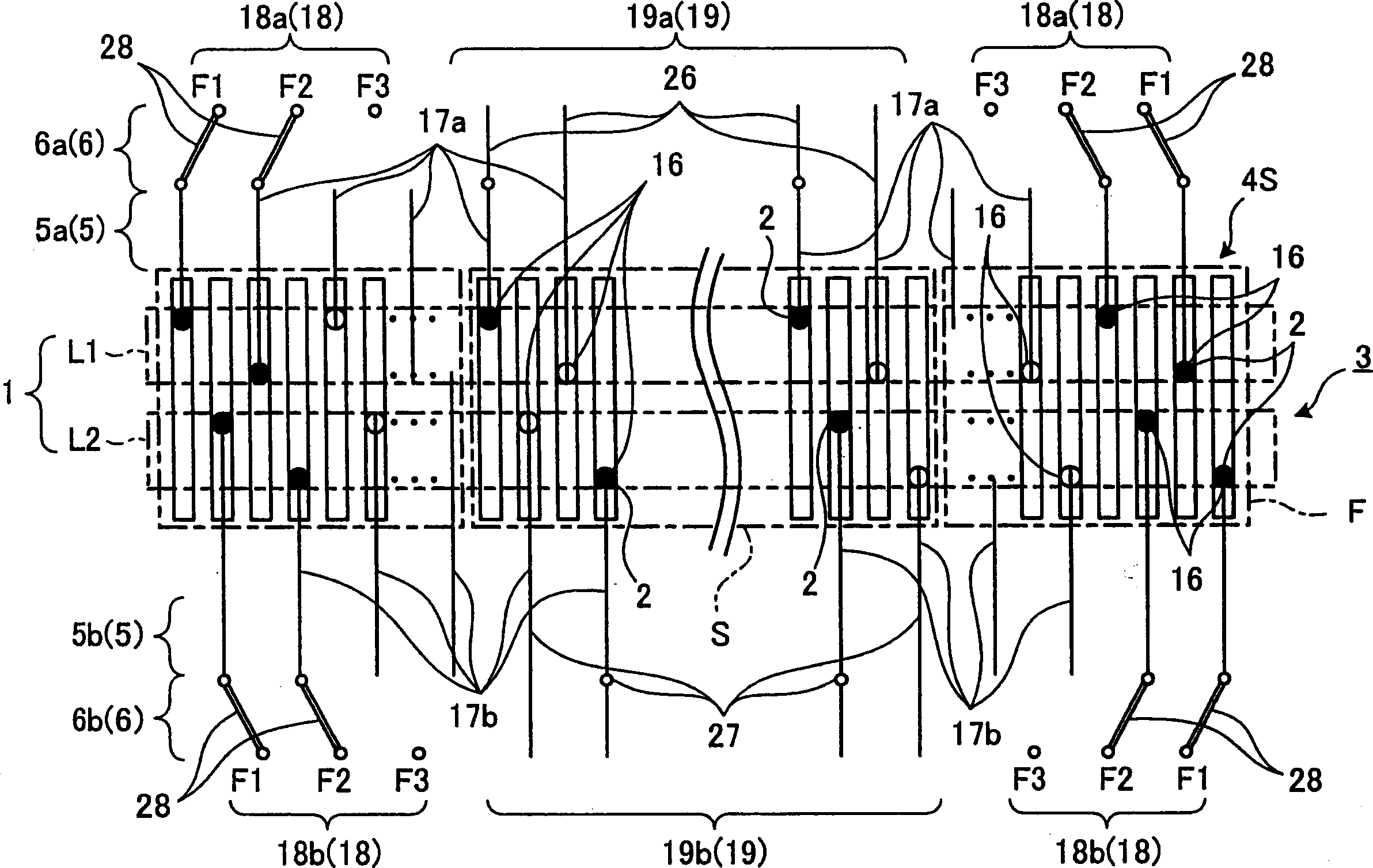

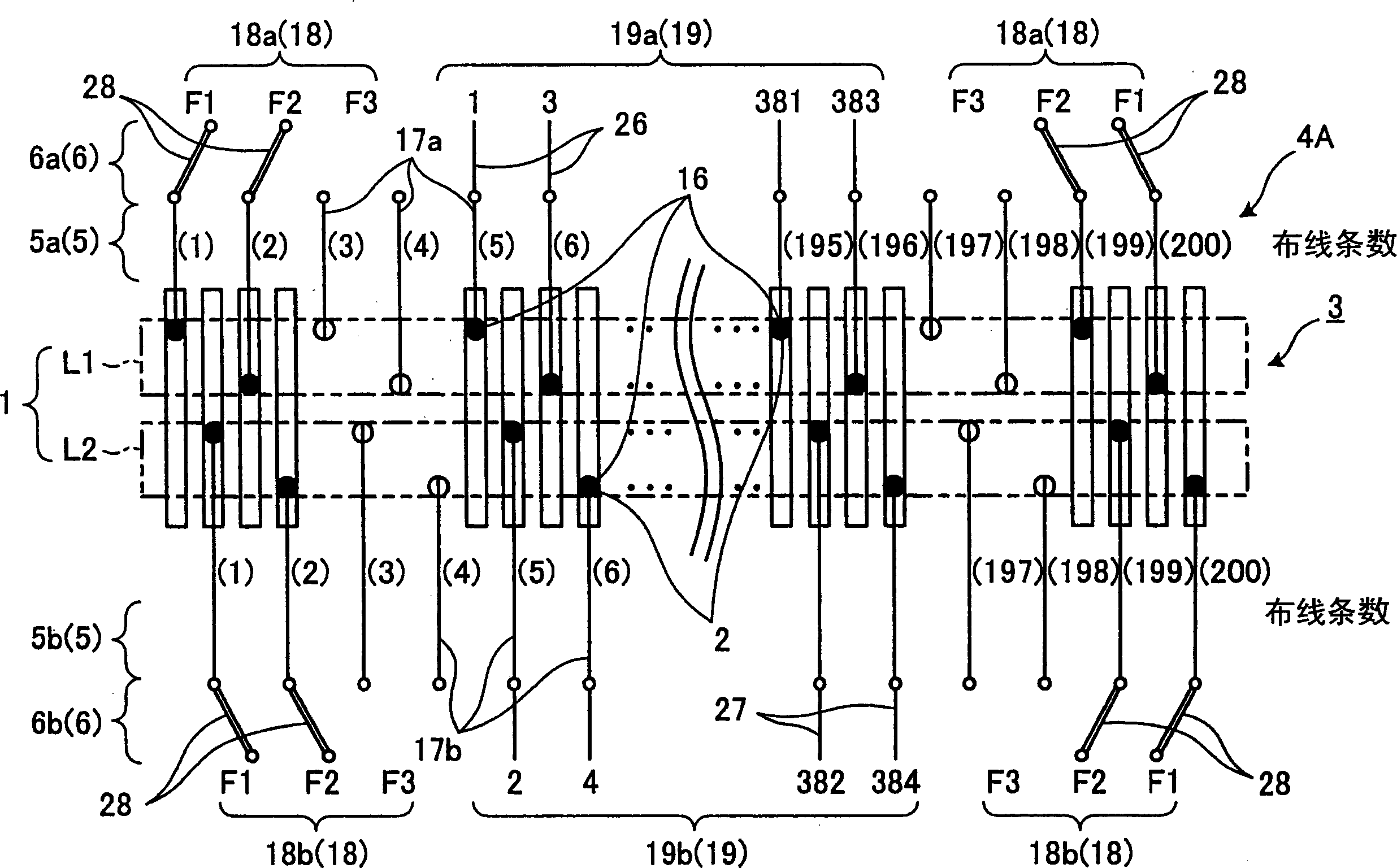

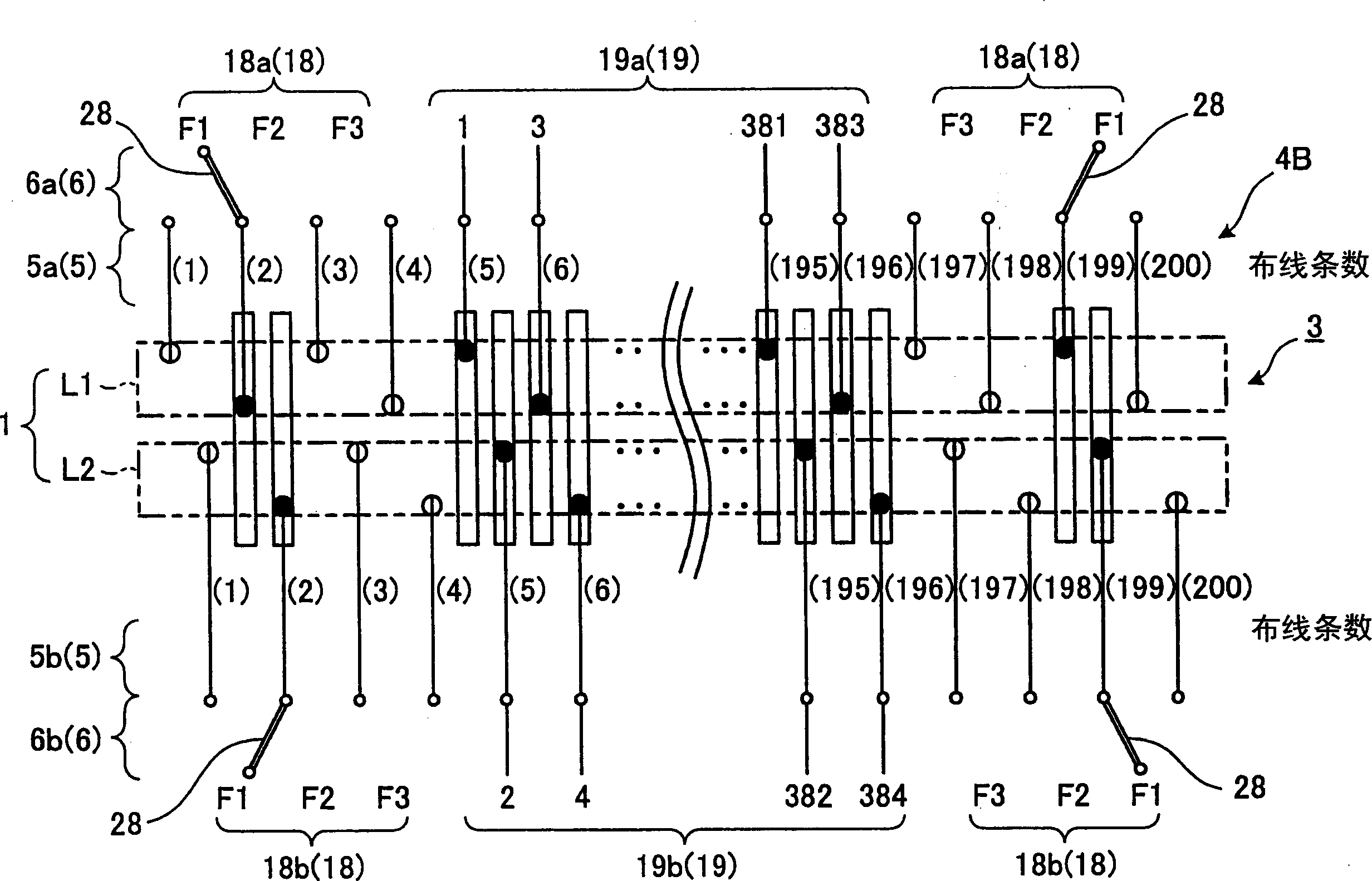

Liquid crystal panel testing device

InactiveCN1764868ACoupling contact membersElectric connection structural associationsLiquid-crystal displayEngineering

An inspection device for a liquid crystal panel, which is an inspection device for a liquid crystal panel in which a probe (2) of a probe block (1) is brought into contact with a conductive pattern (4) for a terminal of an array glass (3) for a liquid crystal panel for inspection Among them, when the probe block (1) is based on the maximum number of functional lines (F) and signal lines (S) made according to the required specifications of the liquid crystal panel to form the basic terminal conductive pattern (4S), it corresponds to the overall The mode of each wiring forms a plurality of insertion holes (16) for inserting the probes (2), and through inserting the probes (2) in the plurality of insertion holes (16), and forming the array glass ( The terminal of 3) is constituted by the insertion hole (16) in which the wirings of the conductive pattern (4) coincide, while the insertion hole (16) where the probe (2) is not inserted remains empty.

Owner:NHK SPRING CO LTD

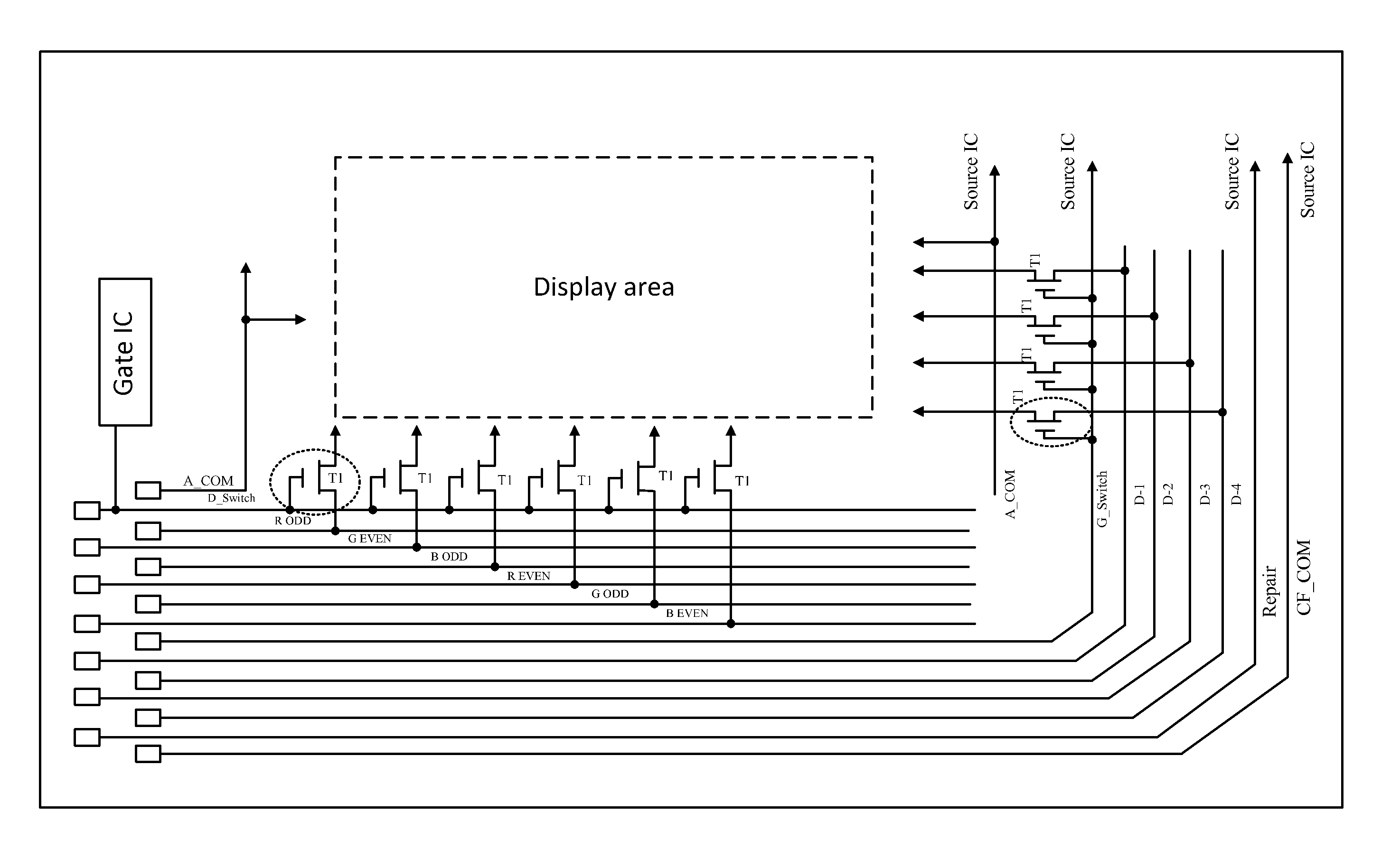

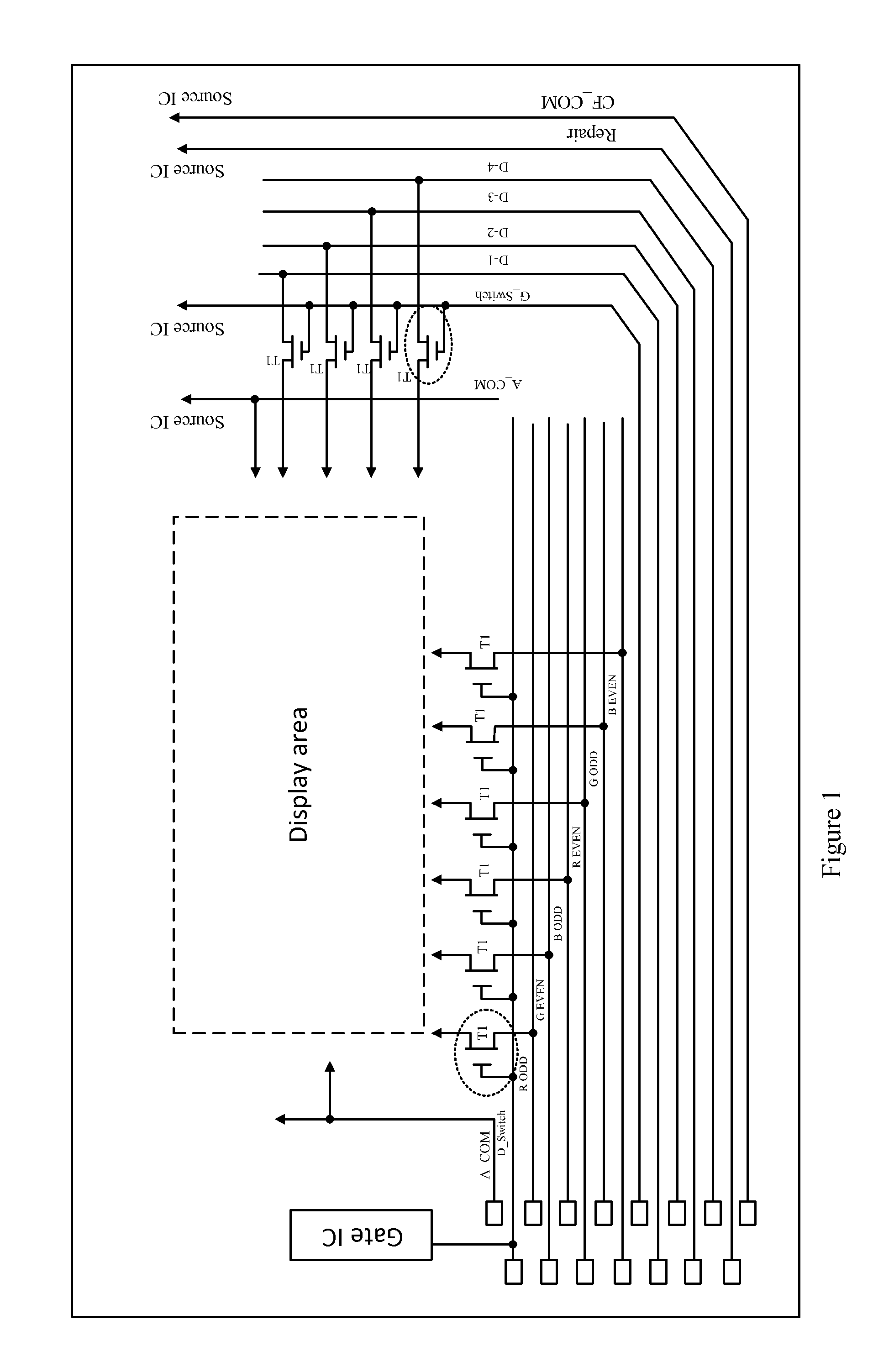

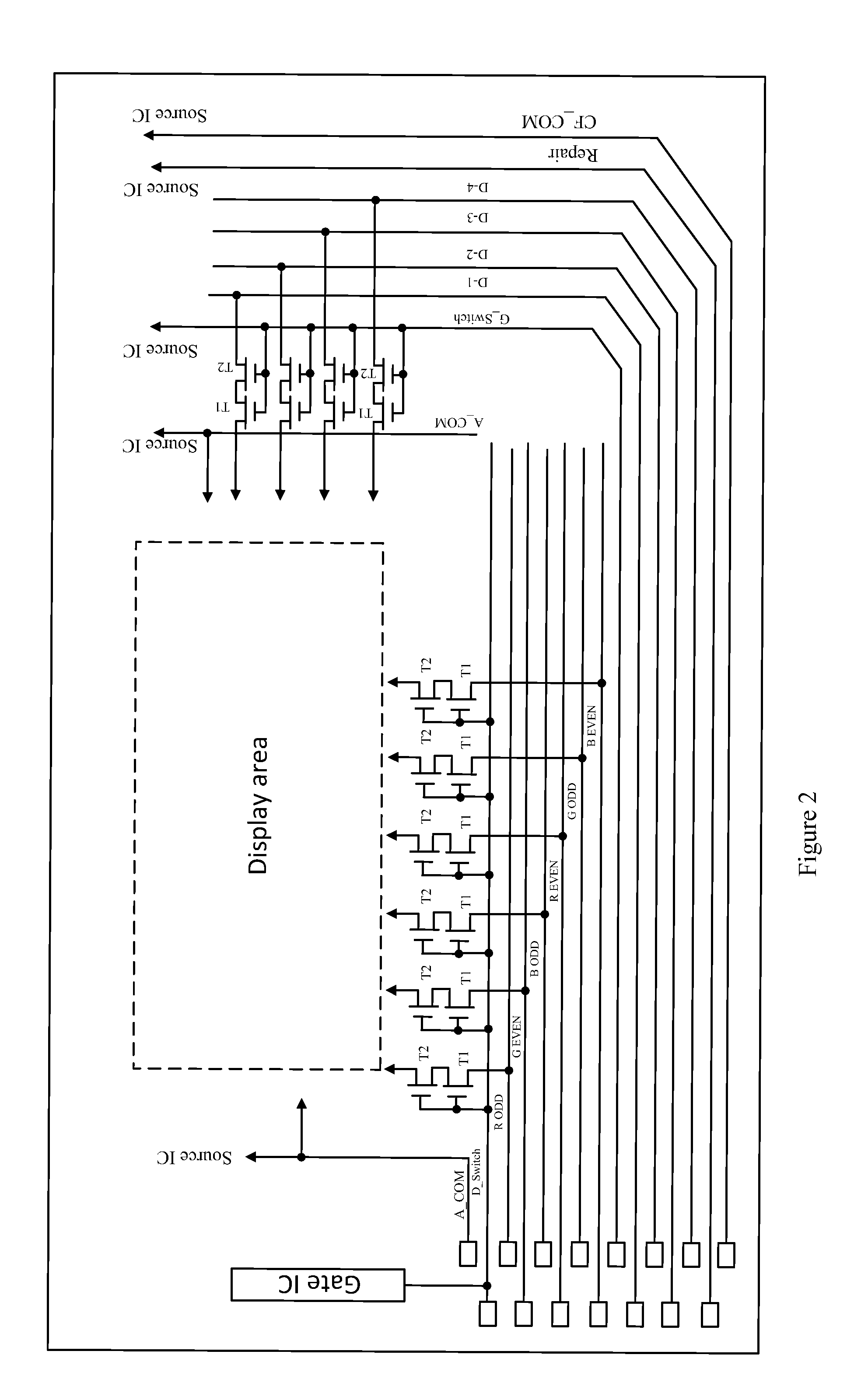

Fast testing switch device and the corresponding tft-lcd array substrate

ActiveUS20150014686A1Improve yieldAvoid crosstalkSemiconductor/solid-state device testing/measurementStatic indicating devicesControl signalEngineering

A fast testing switch device arranged on a TFT-LCD array substrate is disclosed. The fast testing switch device switches the testing signals for testing a display area of the TFT-LCD array substrate. The fast testing switch device includes at least a first switch TFT. The gate of the first switch TFT connects to one control chip and a testing block for receiving the switch control signals from the testing block or the turn-off control signals from the control chip. The source of the first switch TFT connects to one data testing line or one gate testing line, and the drain of the first switch TFT connects to the corresponding data line or gate line of the display area. In addition, a corresponding TFT-LCD array substrate is also disclosed. The above configuration not only can achieve the narrow-bezel design but also can enhance the yield rate of the TFT-LCD array substrate.

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS TECH CO LTD

Method and test system for fast determination of parameter variation statistics

A method and test system for fast determination of parameter variation statistics provides a mechanism for determining process variation and parameter statistics using low computing power and readily available test equipment. A test array having individually selectable devices is stimulated under computer control to select each of the devices sequentially. A test output from the array provides a current or voltage that dependent on a particular device parameter. The sequential selection of the devices produces a voltage or current waveform, characteristics of which are measured using a digital multi-meter that is interfaced to the computer. The rms value of the current or voltage at the test output is an indication of the standard deviation of the parameter variation and the DC value of the current or voltage is an indication of the mean value of the parameter.

Owner:IBM CORP

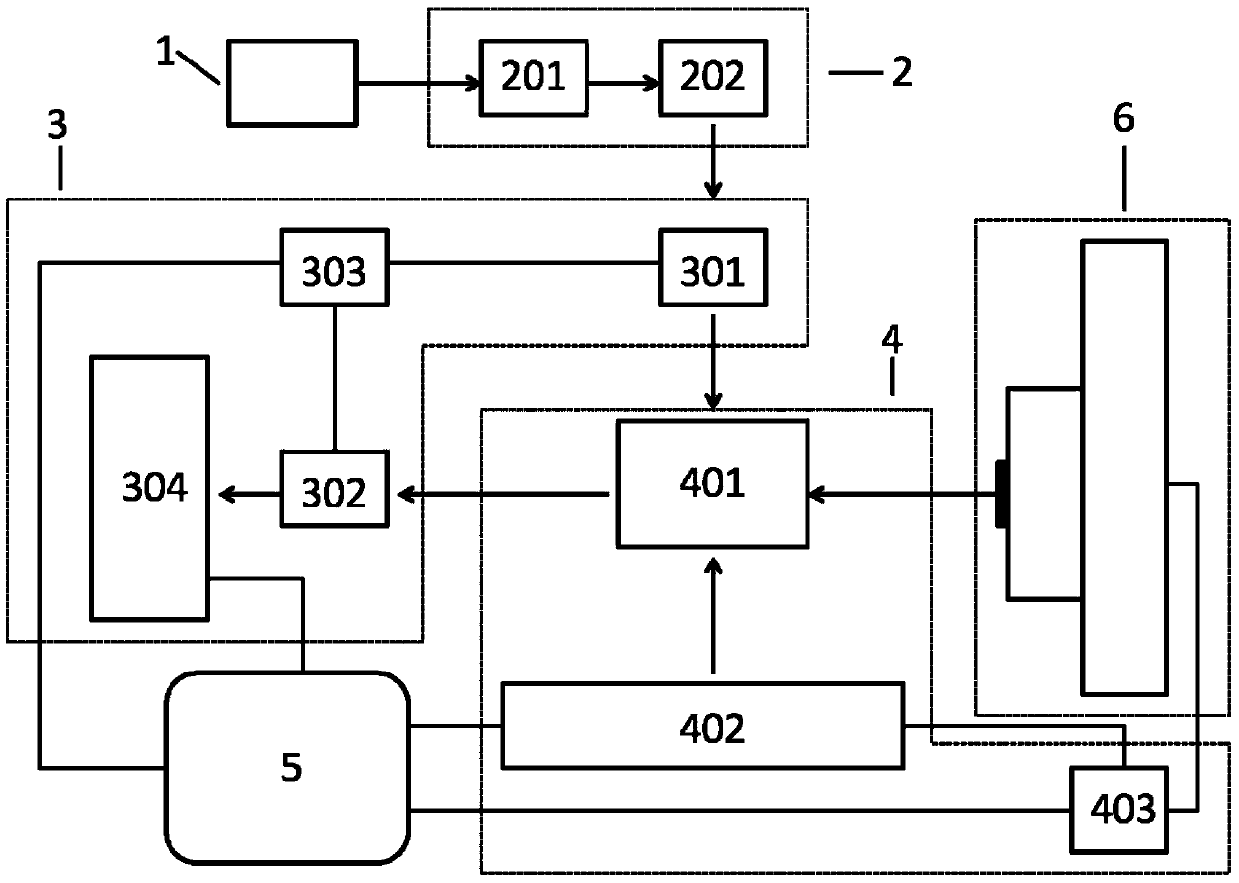

Test method and device of memory

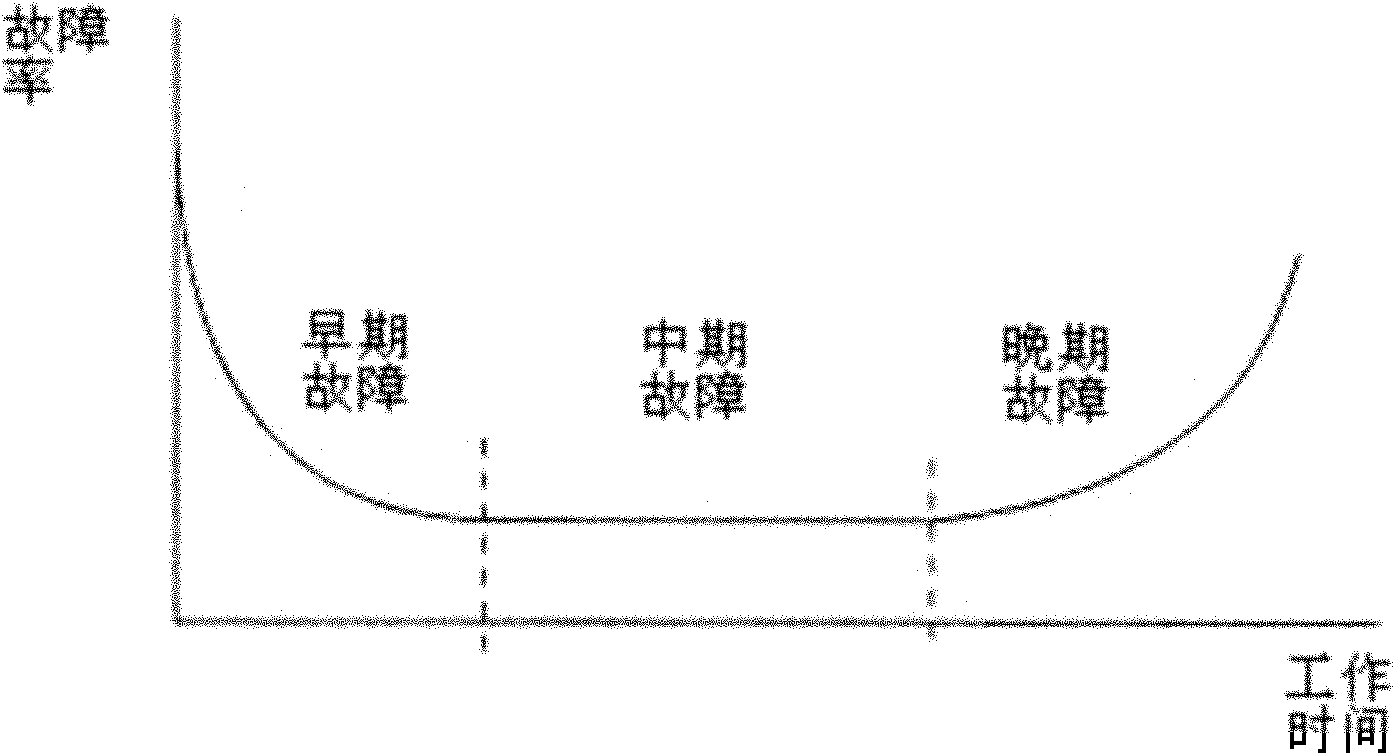

ActiveCN102467973AThe reliability test results are accurateSimple processStatic storageElectricityTemperature control

The invention discloses a test method of a memory, which comprises the following steps that: a controller issues a test command, so that a tested array of the memory is in a test state; after a signal generator receives the test command, a corresponding test signal is generated; after an actuator receives the test signal, the test signal is inputted into the tested array; the tested array generates the power consumption to form the test temperature required by the test of the tested array, so that a test result is obtained, i.e. an aging test is carried out by the temperature generated by the self power consumption of the tested array, and the tested array is not required to be externally heated, thereby the situations that test errors are produced by the inaccurate control of external temperature, the nonuniform distribution of internal temperature, only the self power consumption of the tested array is considered, the test errors caused by power consumption of the tested array is not considered and other factors are avoided, and the memory has more accurate reliability test result, simpler processes and lower cost.

Owner:PEKING UNIV SHENZHEN GRADUATE SCHOOL

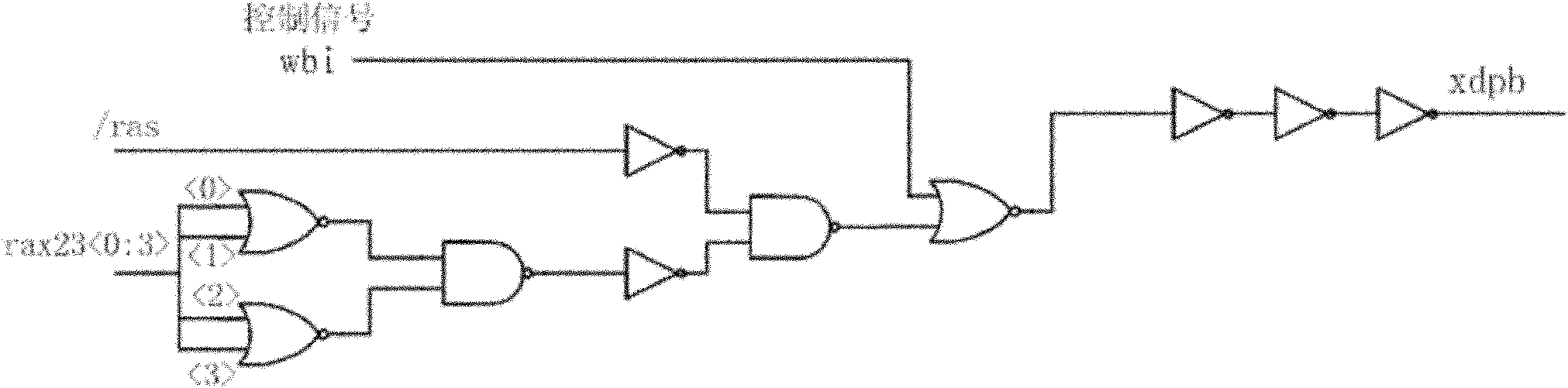

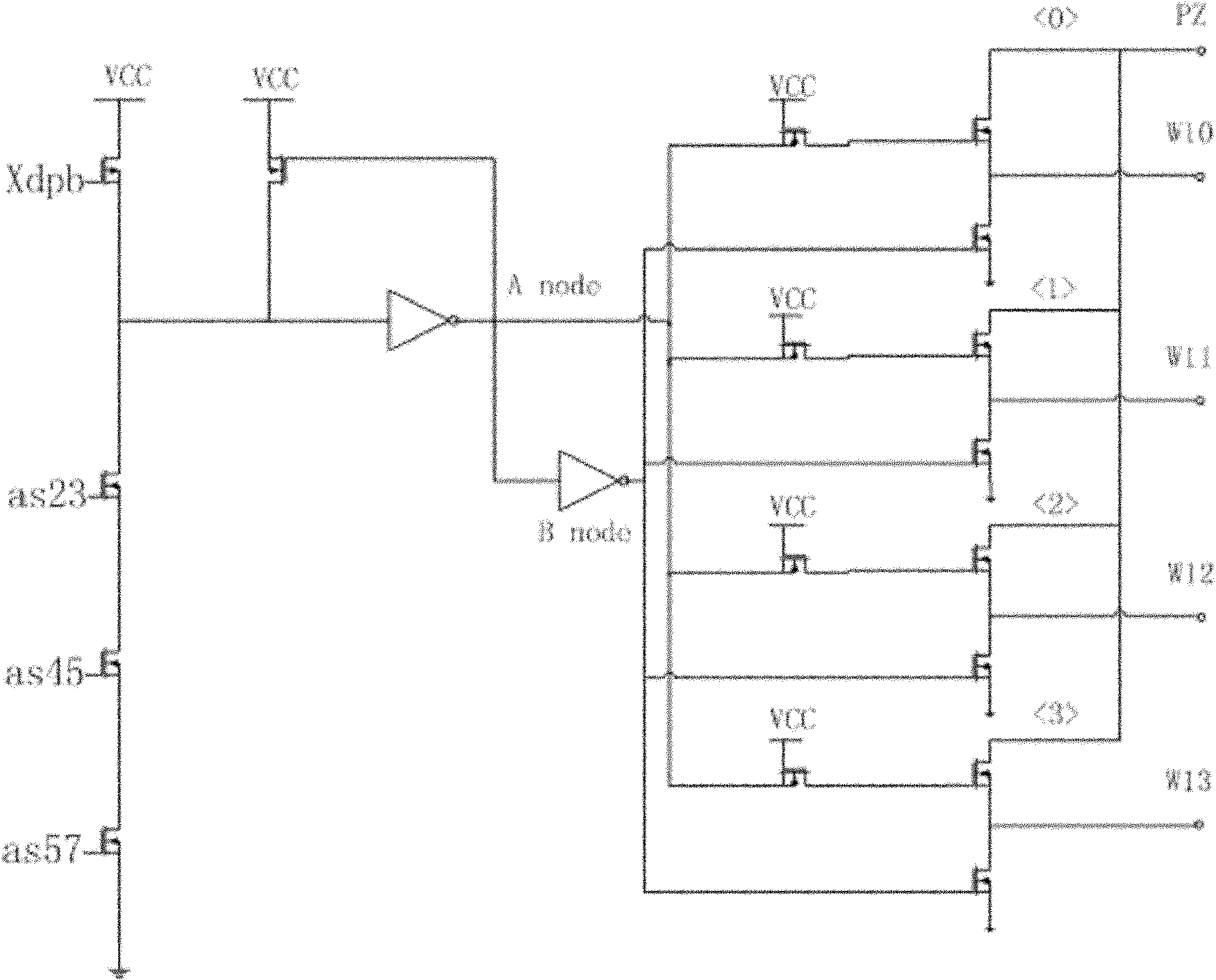

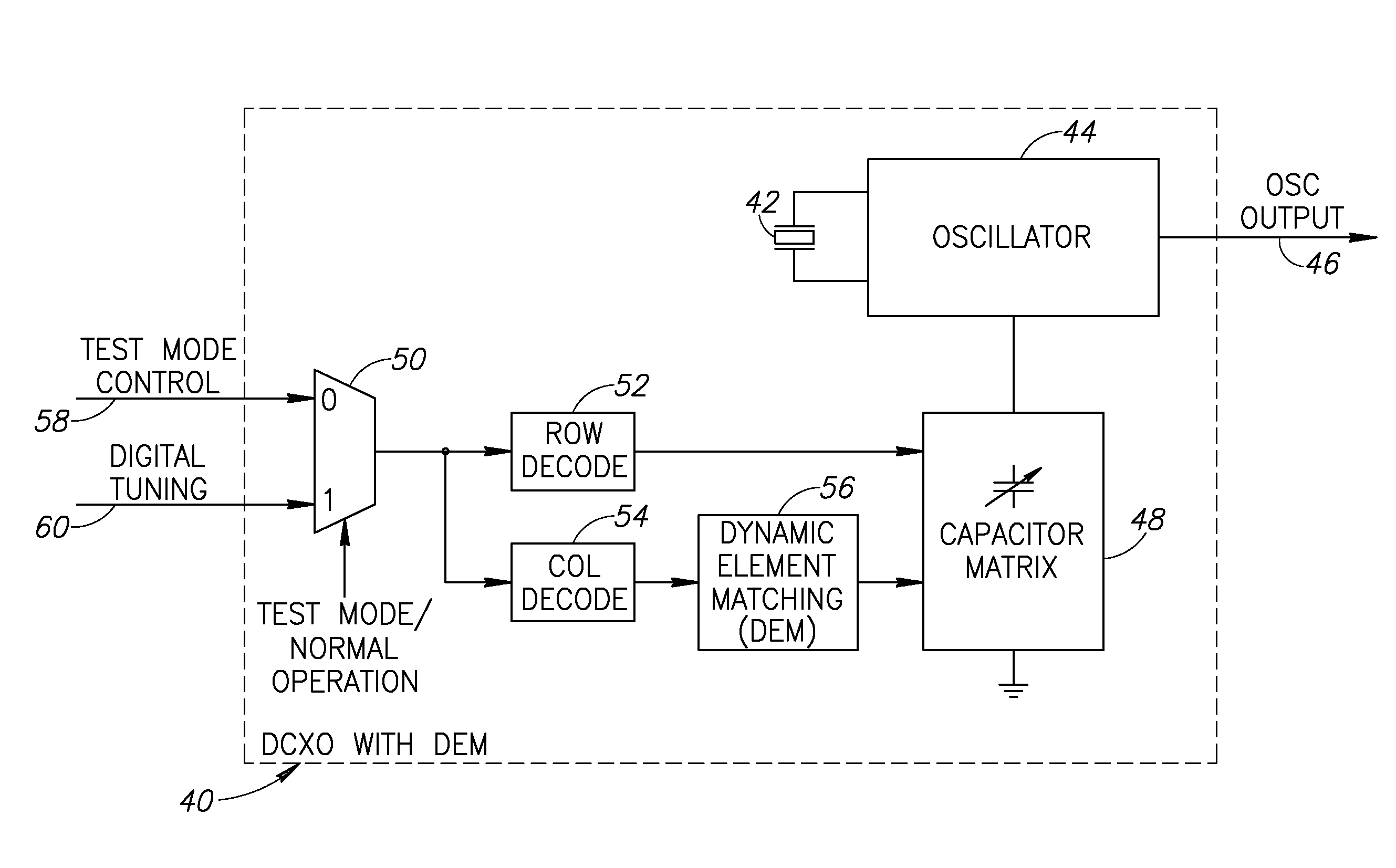

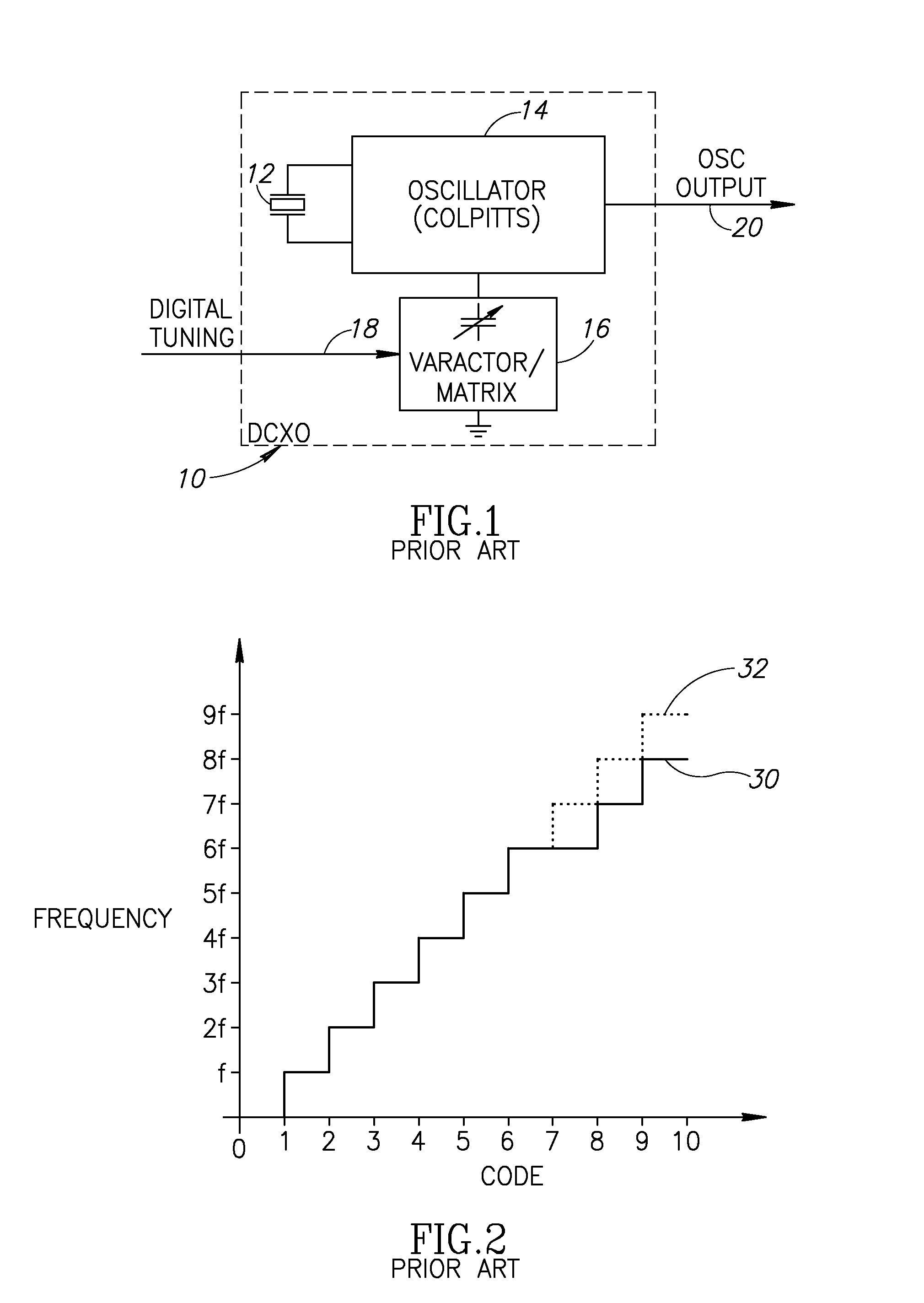

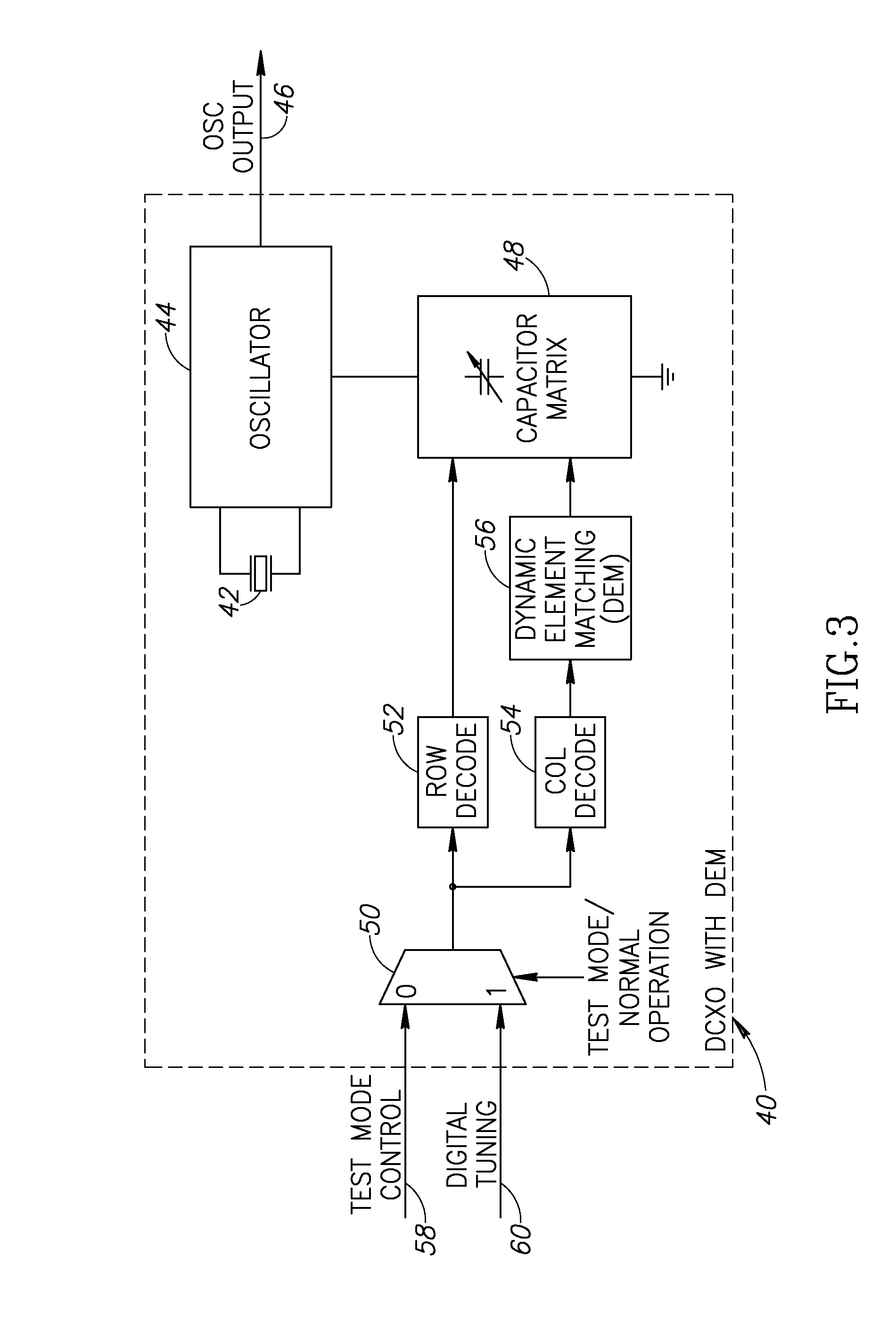

Built-in self test method for a digitally controlled crystal oscillator

ActiveUS20070182496A1Long and costlyShorten test timeAnalogue/digital conversionElectric signal transmission systemsCapacitanceEngineering

A novel testing mechanism operative to test large capacitor arrays such as those used in a digitally controlled crystal oscillator (DCXO). The invention is adapted for use in DCXO circuits that employ dynamic element matching in their array decoding circuits. The invention combines the use of DEM during regular operation of the DCXO with a testing technique that greatly reduces the number of tests required. The invention tests the capacitors in the array on a row by row, wherein all the capacitors in a row are tested lumped together and treated as a single entity, which results in significantly reduced testing time. This permits the measurement of significantly higher frequency deviations due to the larger capacitances associated with an entire row of capacitors being tested

Owner:TEXAS INSTR INC

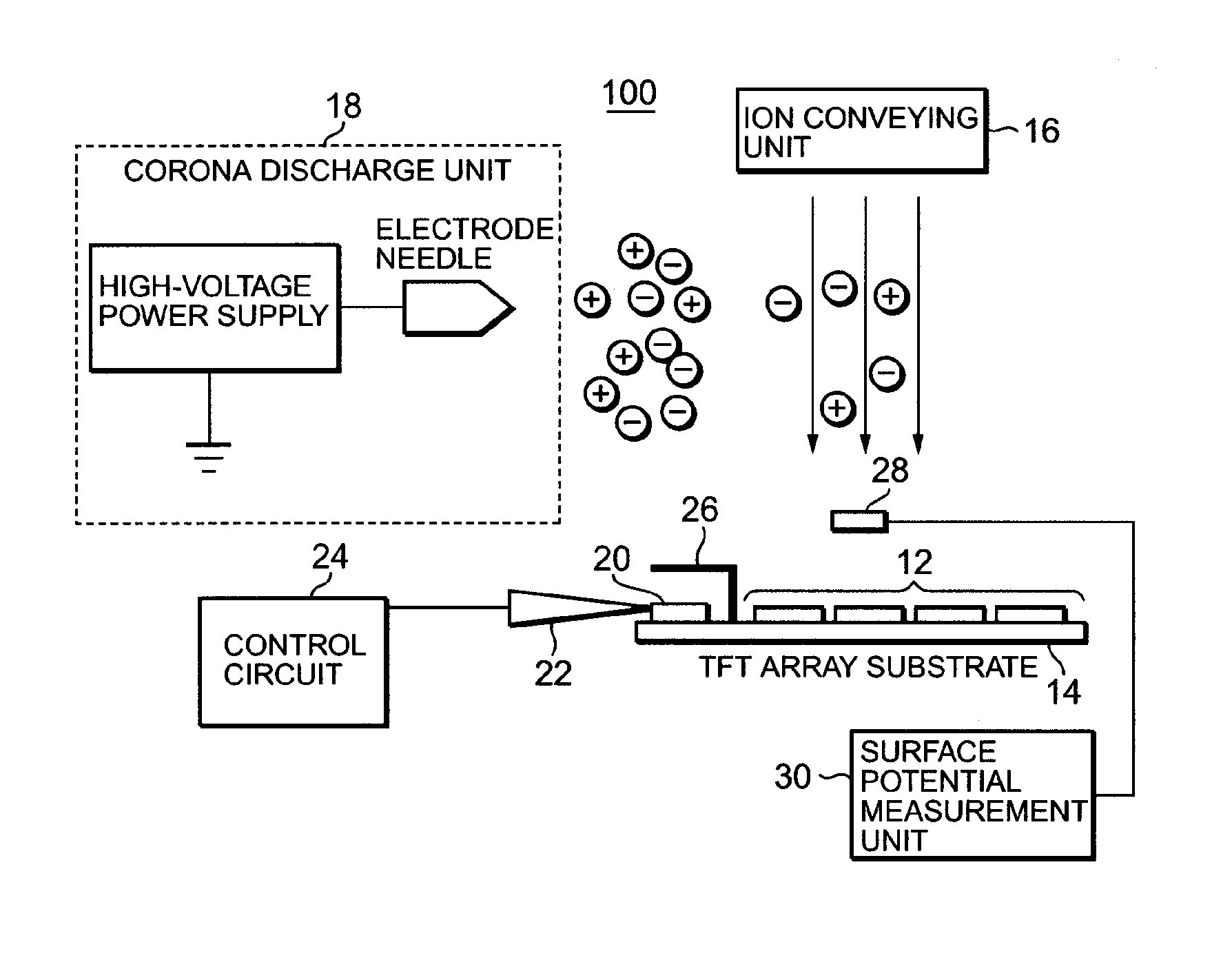

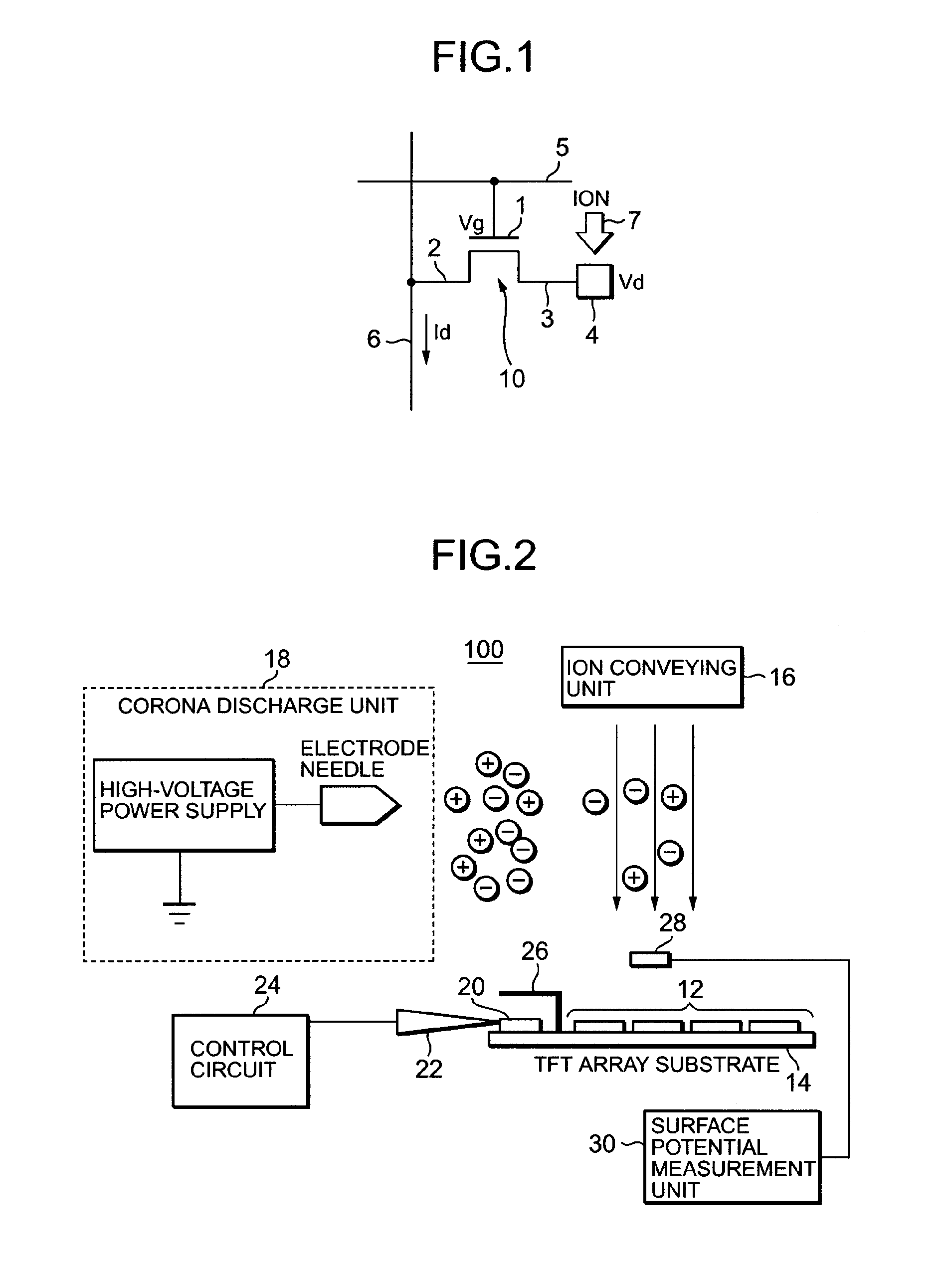

Thin film transistor tester and corresponding test method

InactiveUS20060097745A1Static indicating devicesIndividual semiconductor device testingTester deviceEngineering

To test electrical characteristics of a Thin Film Transistor (TFT) with a source or drain terminal left open and exposed, using a non-contact current source and protecting the TFTs from adverse effects, such as contamination, destruction, and the like. A tester 100 is provided to test a TFT array substrate 14, the tester including ion flow supply devices 16 and 18 for supplying an ion flow onto the surface of a substrate 14. Thereon, an array 12 of TFTs is formed, each TFT being connected to an electrode having a source or a drain left open and exposed; a control circuit 24 for supplying an operating voltage to a gate electrode of the TFT to be tested in the array; and a measurement circuit 24 for measuring an operating current via the testing TFT source or drain that remain in a non open state.

Owner:GOOGLE LLC

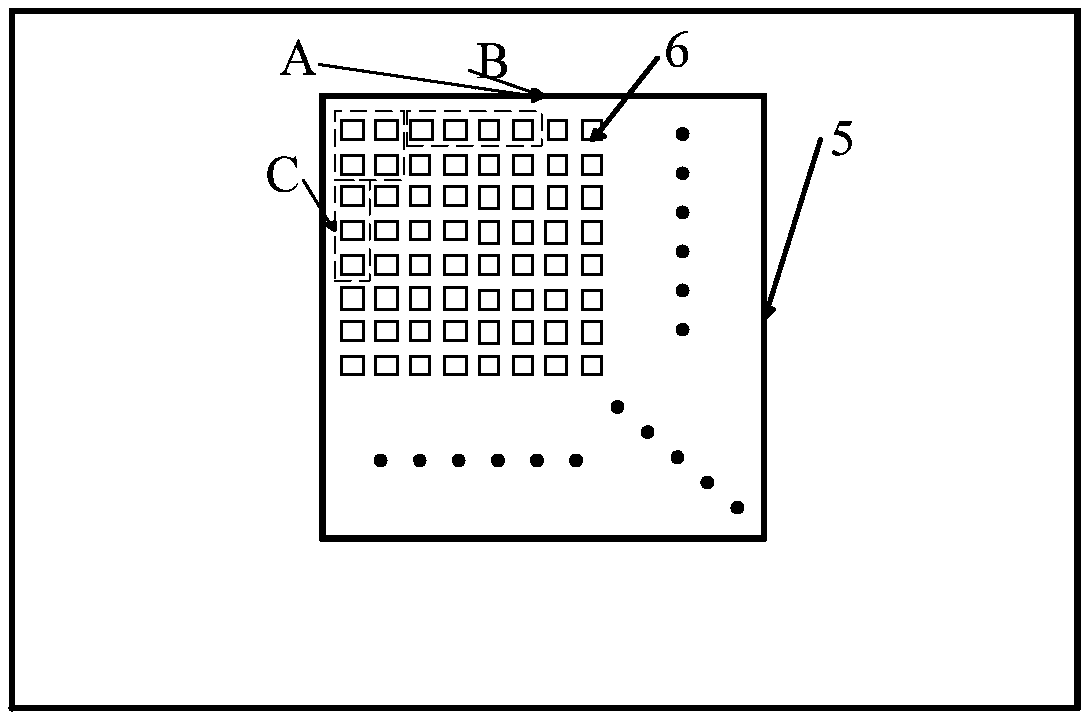

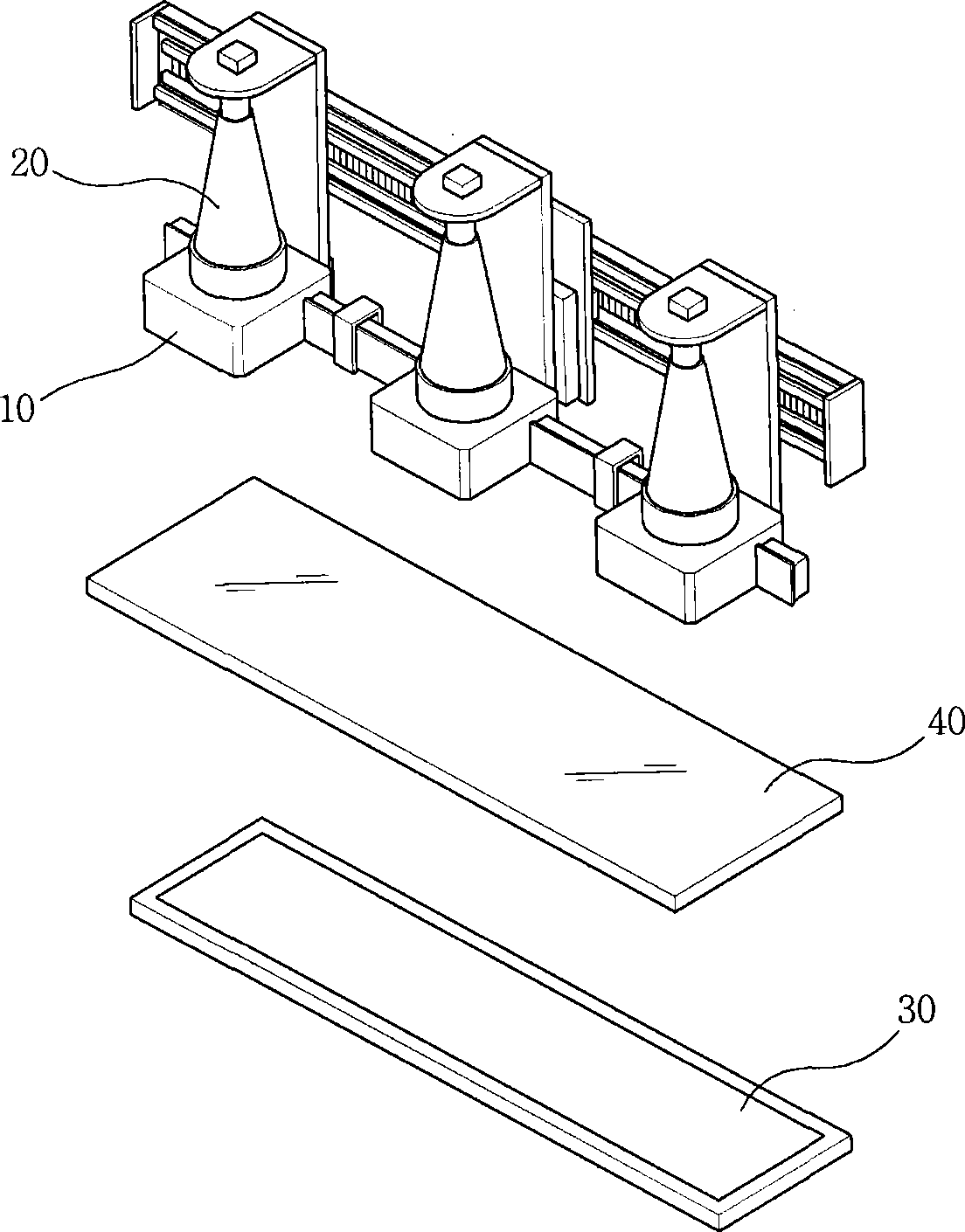

Array detecting device

InactiveCN101419373AImprove defect detection reliabilityStatic indicating devicesElectrical testingOptoelectronicsTest array

The invention discloses an array test apparatus that detects whether electric defect exists in a plurality of electrodes on the substrate of the display panel. The array test apparatus comprises at least one light source and at least one modulator. The light source is installed at one side of the substrate opposite to the position where the modulation is installed. The light source is corresponding to the modulator, which emits light to the corresponding modulator and is moved to a position that is the same as that of the modulator. The size of the light source is as small as that of the modulator, so the luminance difference of the light source is obviously reduced. Therefore, the light source emits uniform light to the substrate to provide uniform light for the modulator so that the amount of light changed according to whether defects exist in the electrode of the panel can be stable. Therefore, a detection unit for testing array measures the amount of the light through the modulator and whether the electrode has defects is accurately ensured so that the reliability of detecting defects by the panel.

Owner:TOP ENG CO LTD

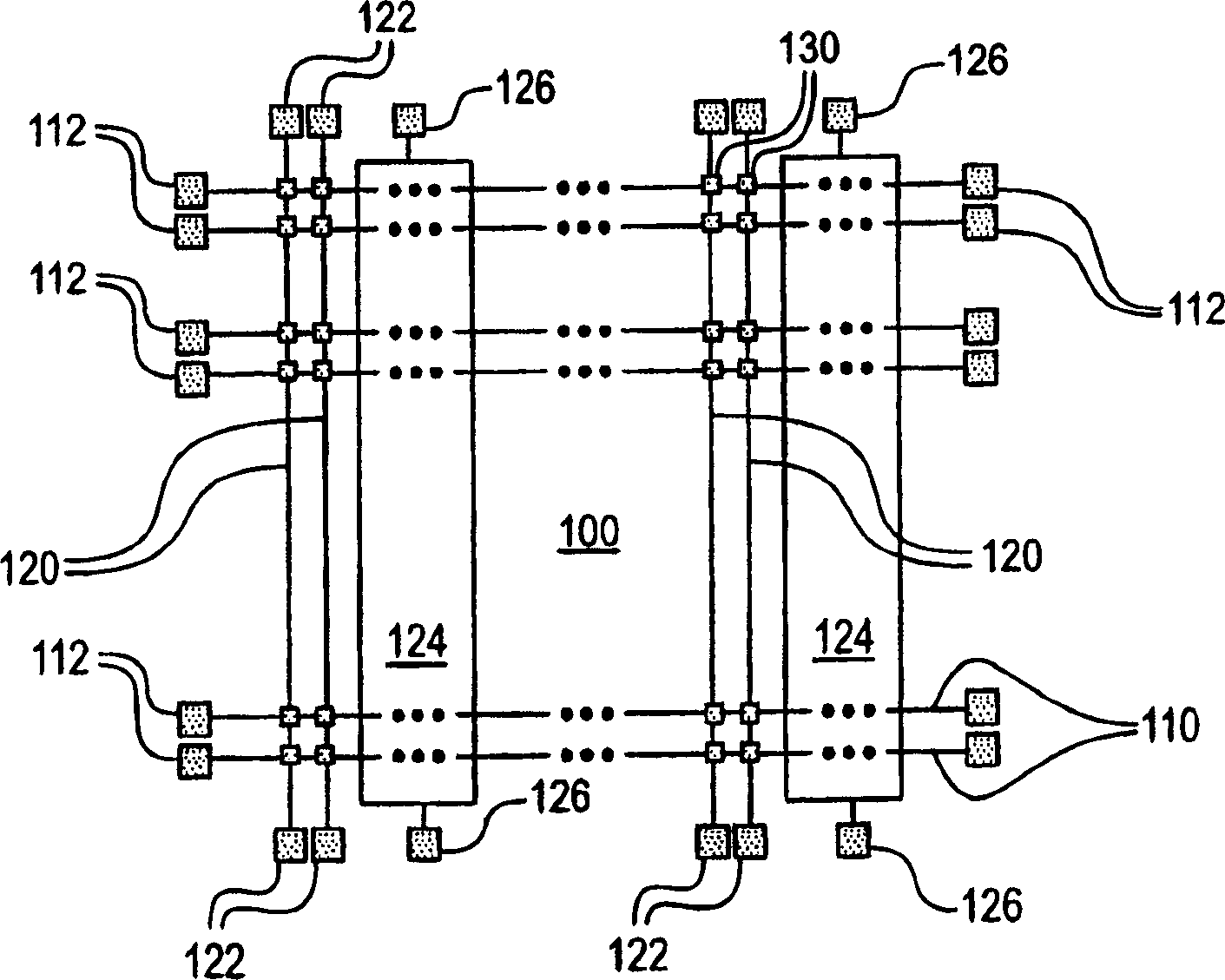

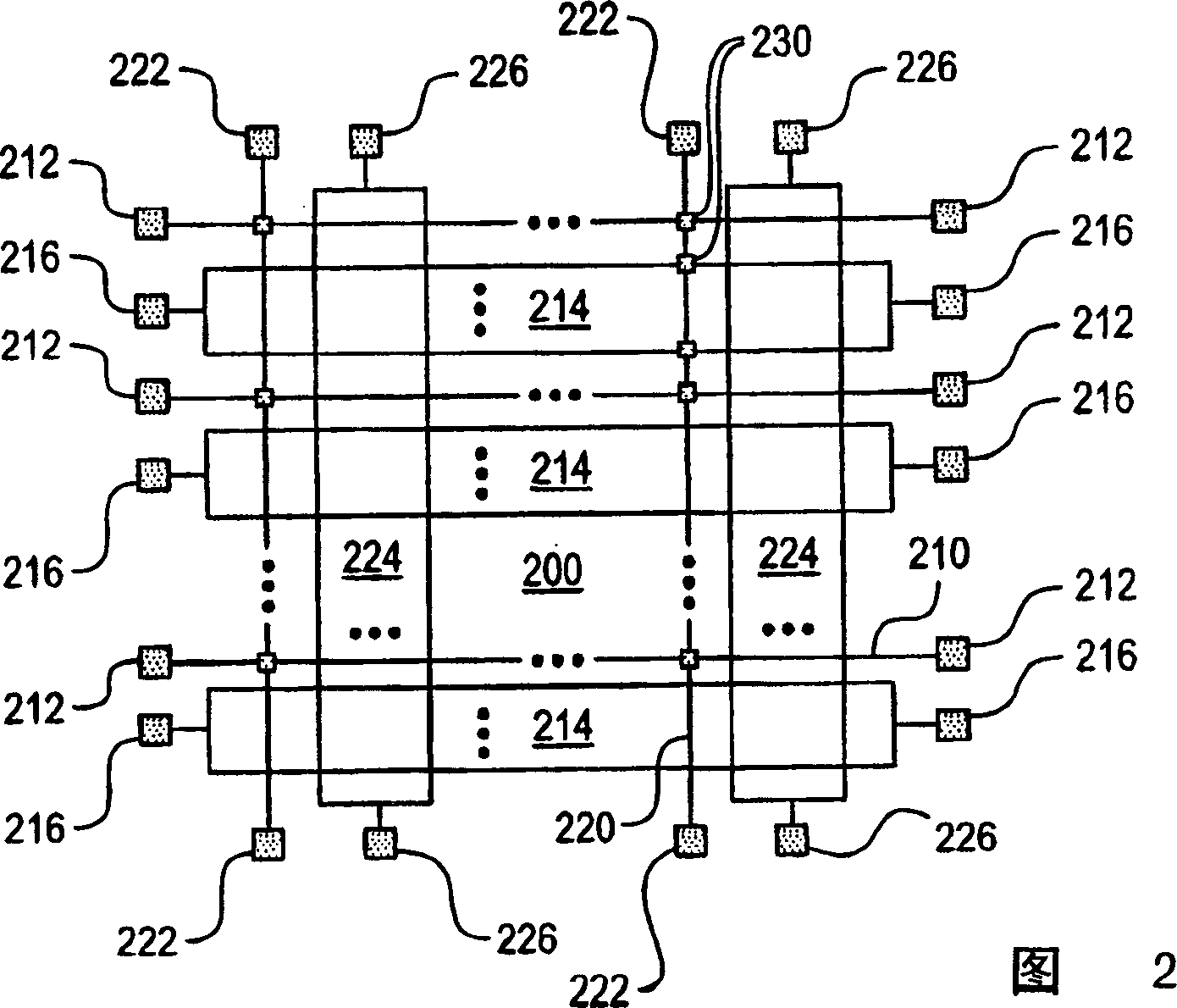

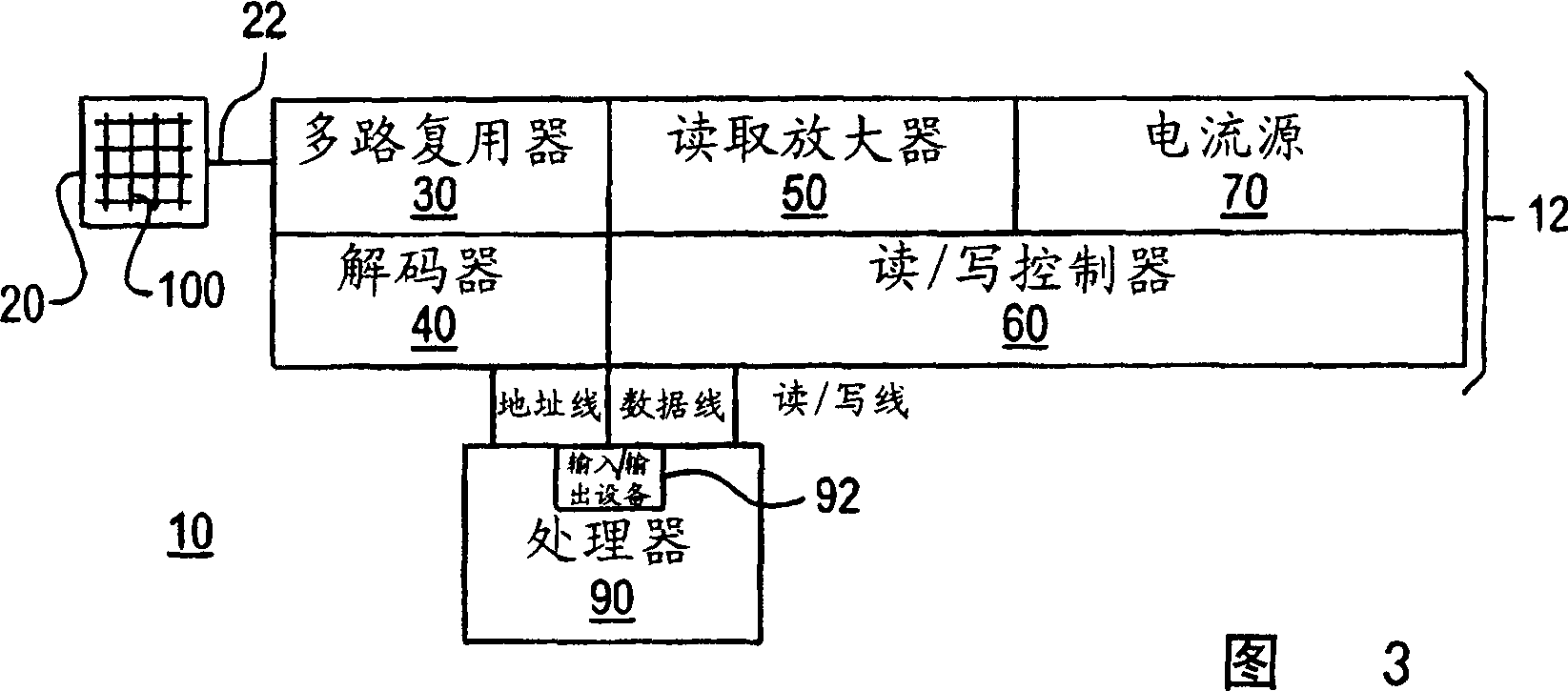

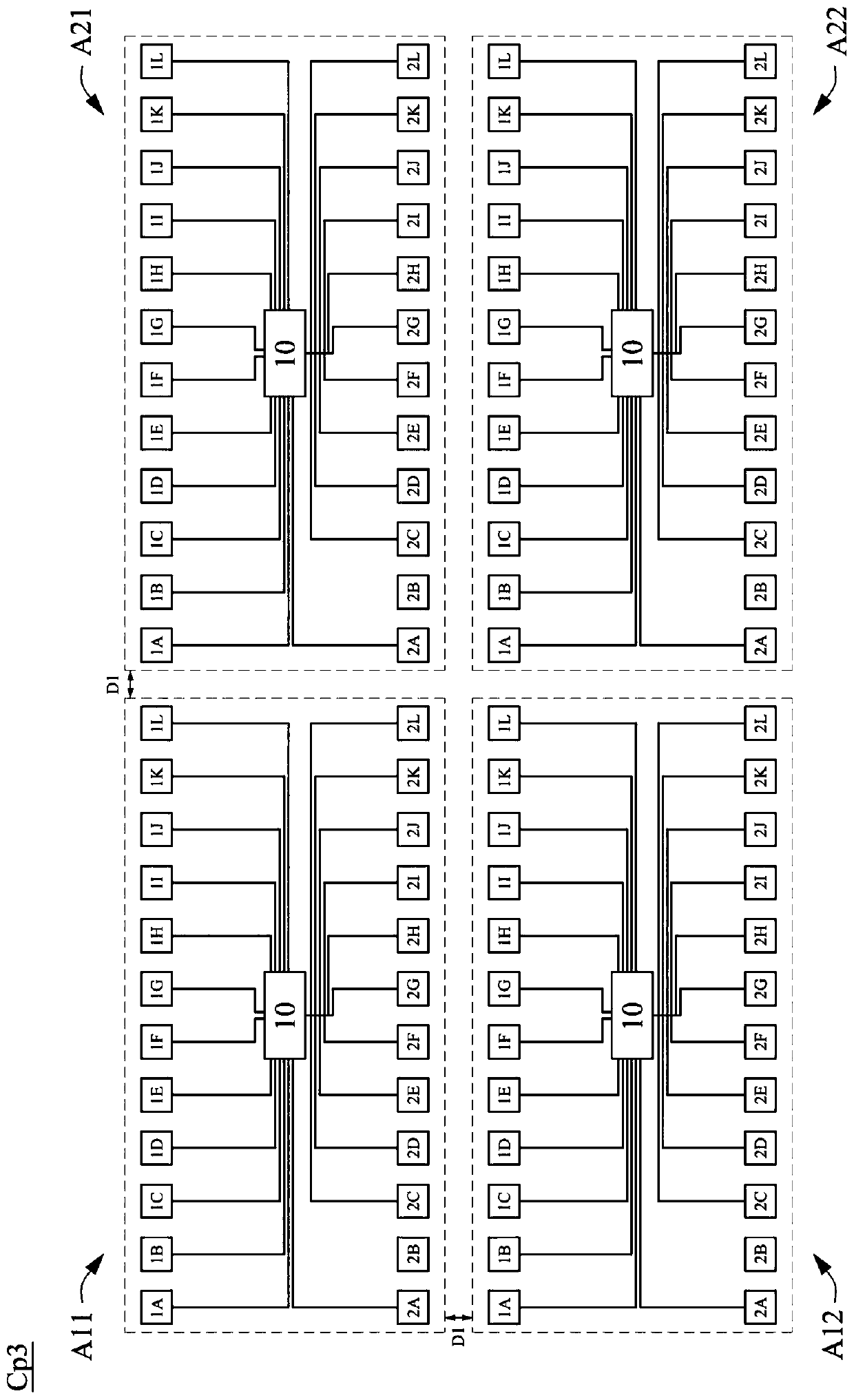

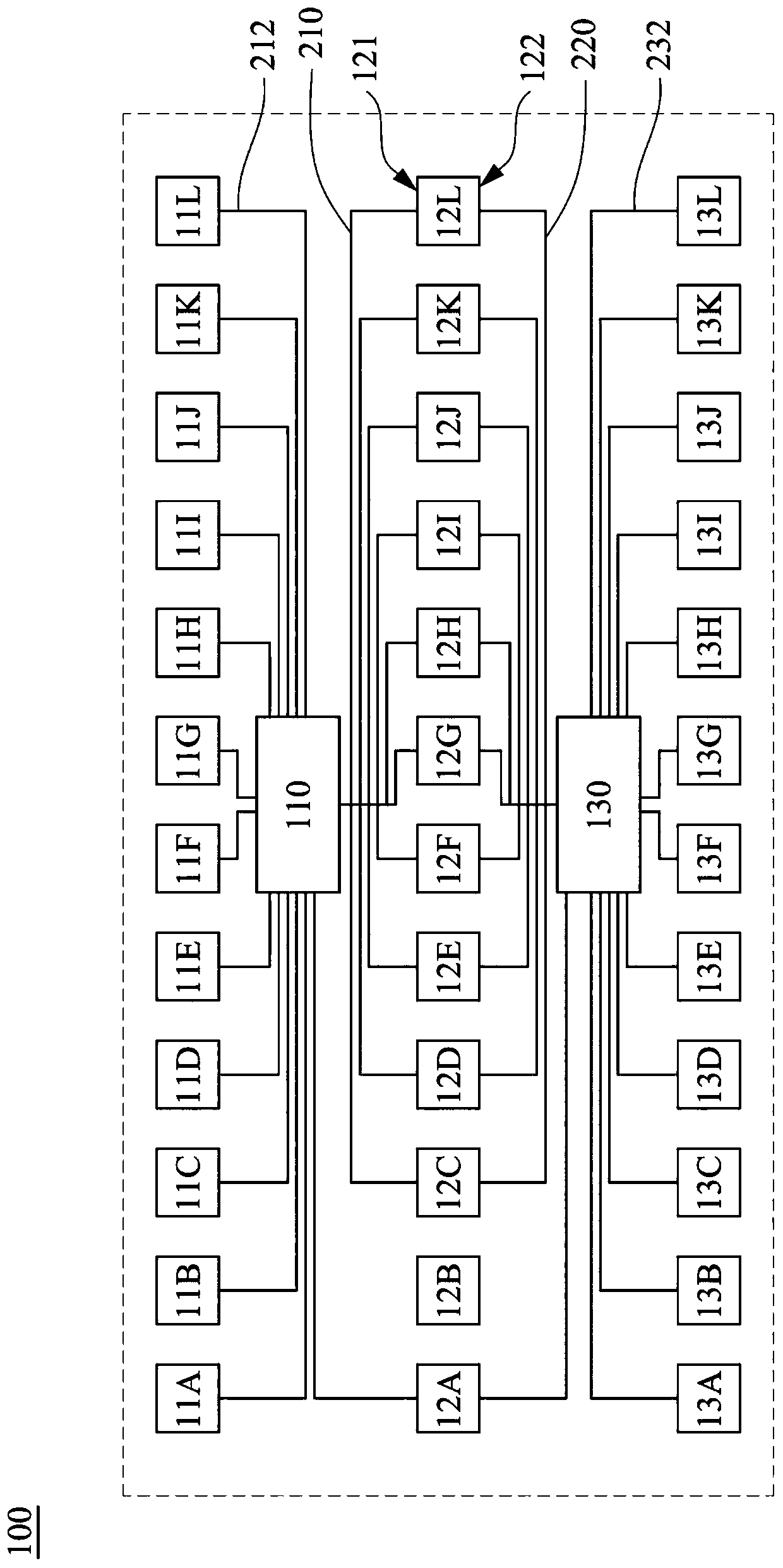

Testing array and method for testing storage array

InactiveCN1414619ASemiconductor/solid-state device testing/measurementElectronic circuit testingElectricityElectrical conductor

A test array (100, 200) includes row conductors (110, 210), column conductors (120, 220), and memory cells (130, 230) located at crossing points of the row and column conductors. The test array (100, 200) can have groups (124, 214, 224) of the row conductors (110, 210) or the column conductors (120, 220) electrically coupled, or ganged together, so that they share common terminals (216, 226). Other selected row and column conductors can have individual terminals (112, 122, 212, 222). In this configuration, memory cells (130, 230) located at the intersection of row and column conductors that have individual terminals (112, 122, 212, 222) can have their characteristics measured using a test apparatus. Ganging together groups of row or column conductors means that the test array has (100, 200) fewer terminals for connection to the test apparatus. Therefore, a test apparatus having a limited number of probes for connection to test array terminals can be used to test arrays (100, 200) of various sizes.

Owner:HEWLETT PACKARD CO

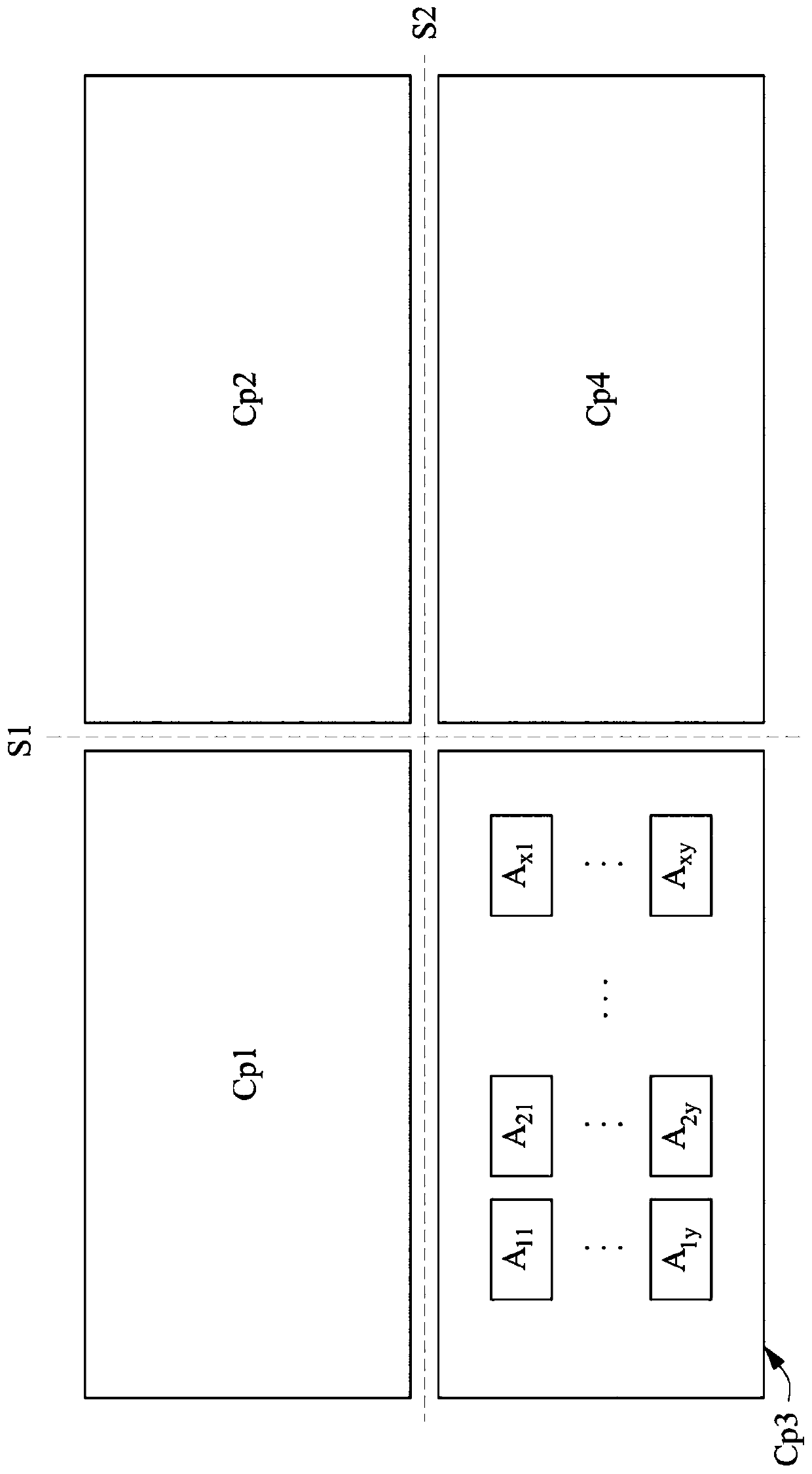

Memory test array and test method thereof

The invention discloses a memory test array and a test method thereof. The memory test array comprises a first memory array, a second memory array and a plurality of first common conductive pads. Thefirst memory array includes a plurality of first bit lines and a plurality of first word lines. The second memory array is adjacent to the first memory array and includes a plurality of second bit lines and a plurality of second word lines. Each first common conductive pad is provided with a first end and a second end, and the first end and the second end are coupled to the first bit line and thesecond bit line respectively or coupled to the first word line and the second word line respectively. The memory test array can effectively save the area of a memory test wafer, and enables the test process to be more efficient.

Owner:BEIJING ADVANCED MEMORY TECH CO LTD

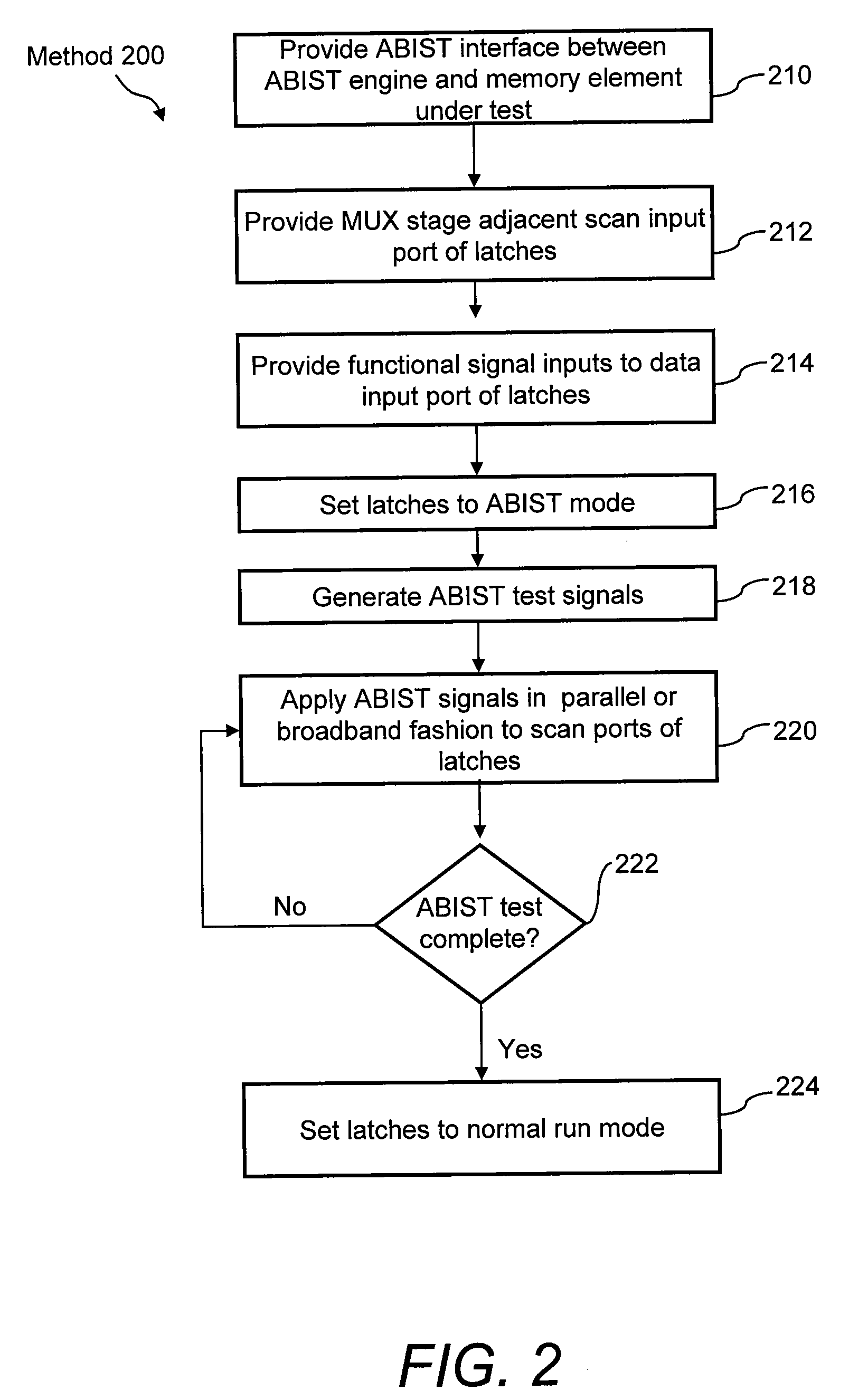

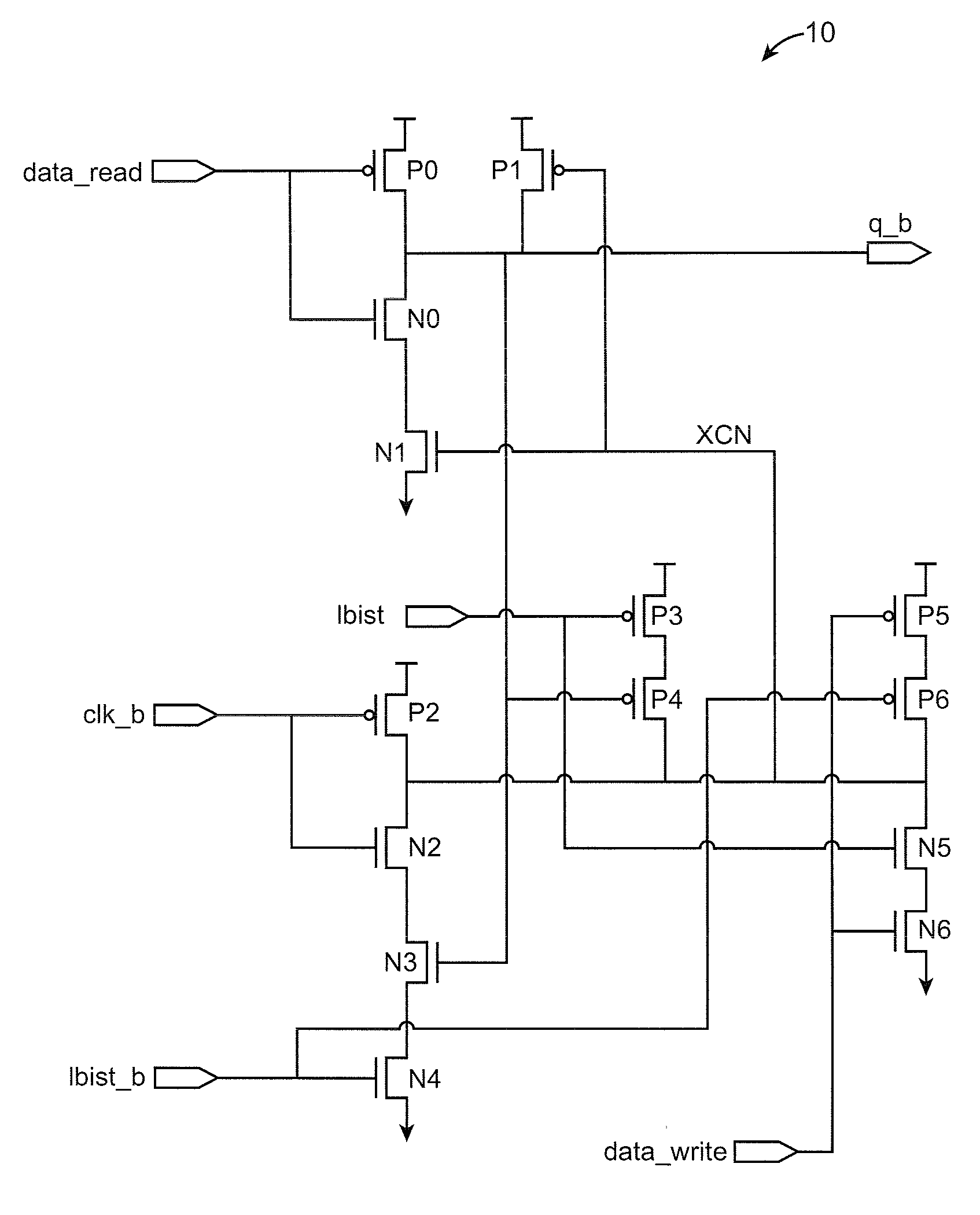

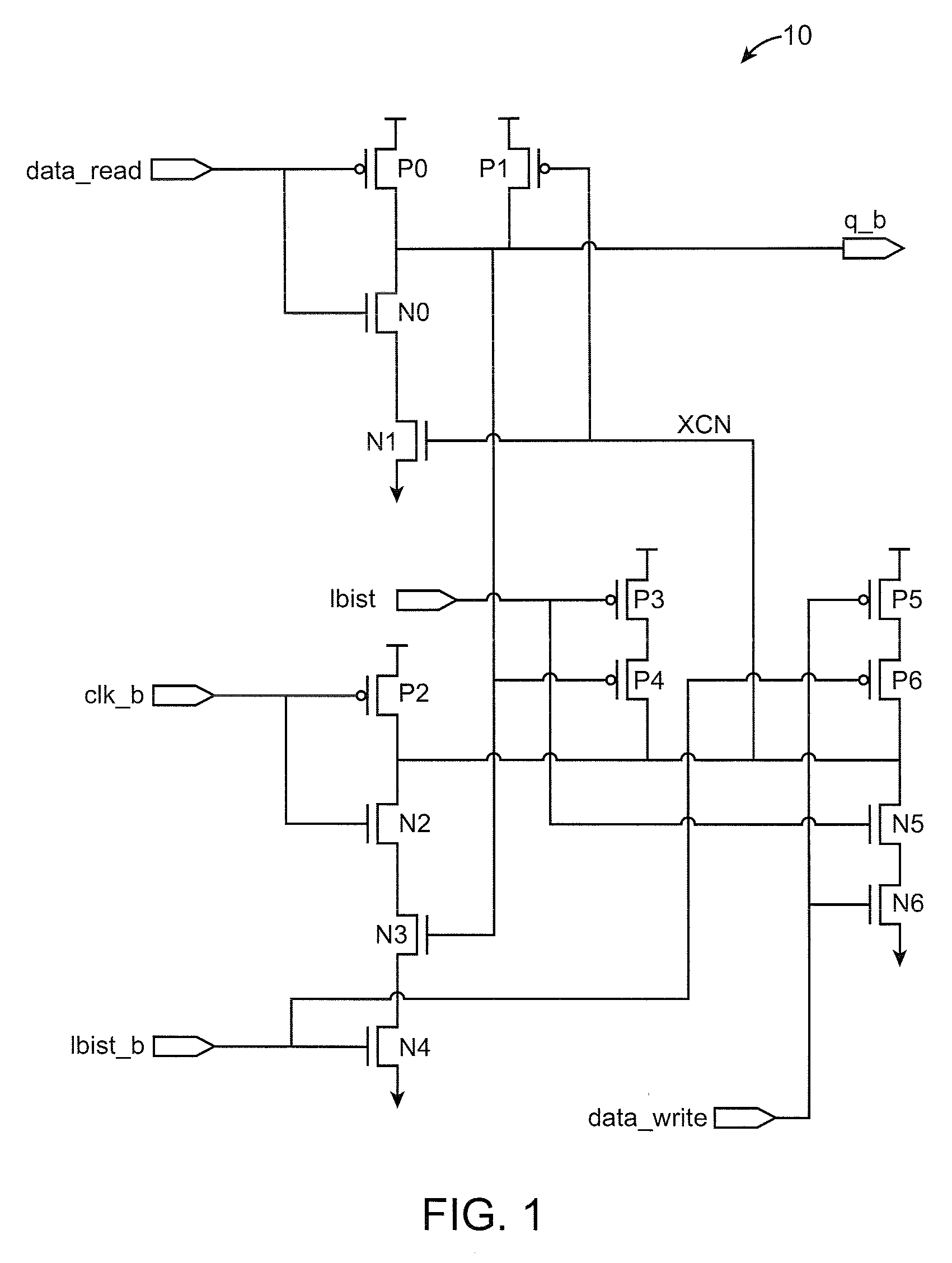

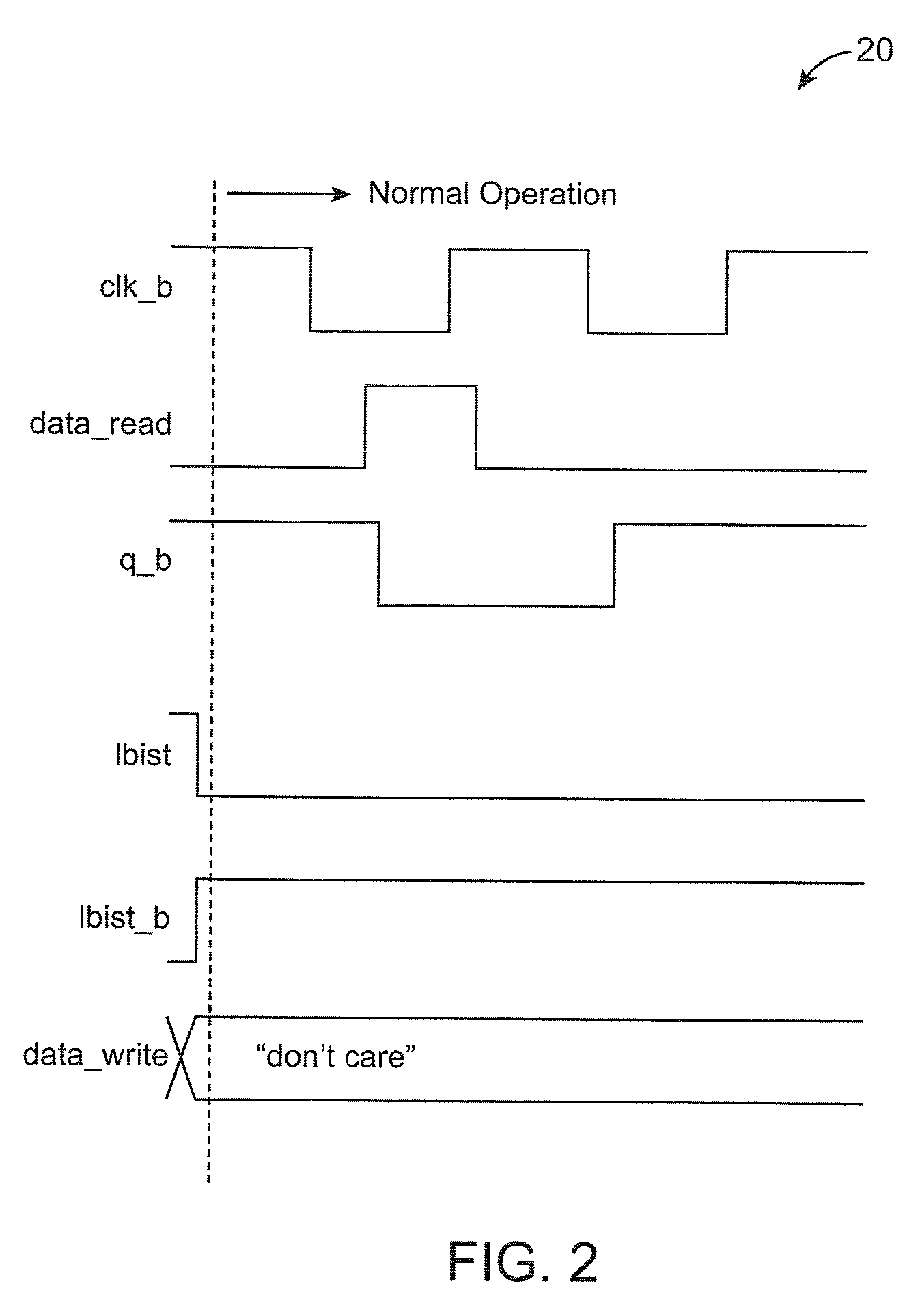

Test interface for memory elements

Owner:INT BUSINESS MASCH CORP

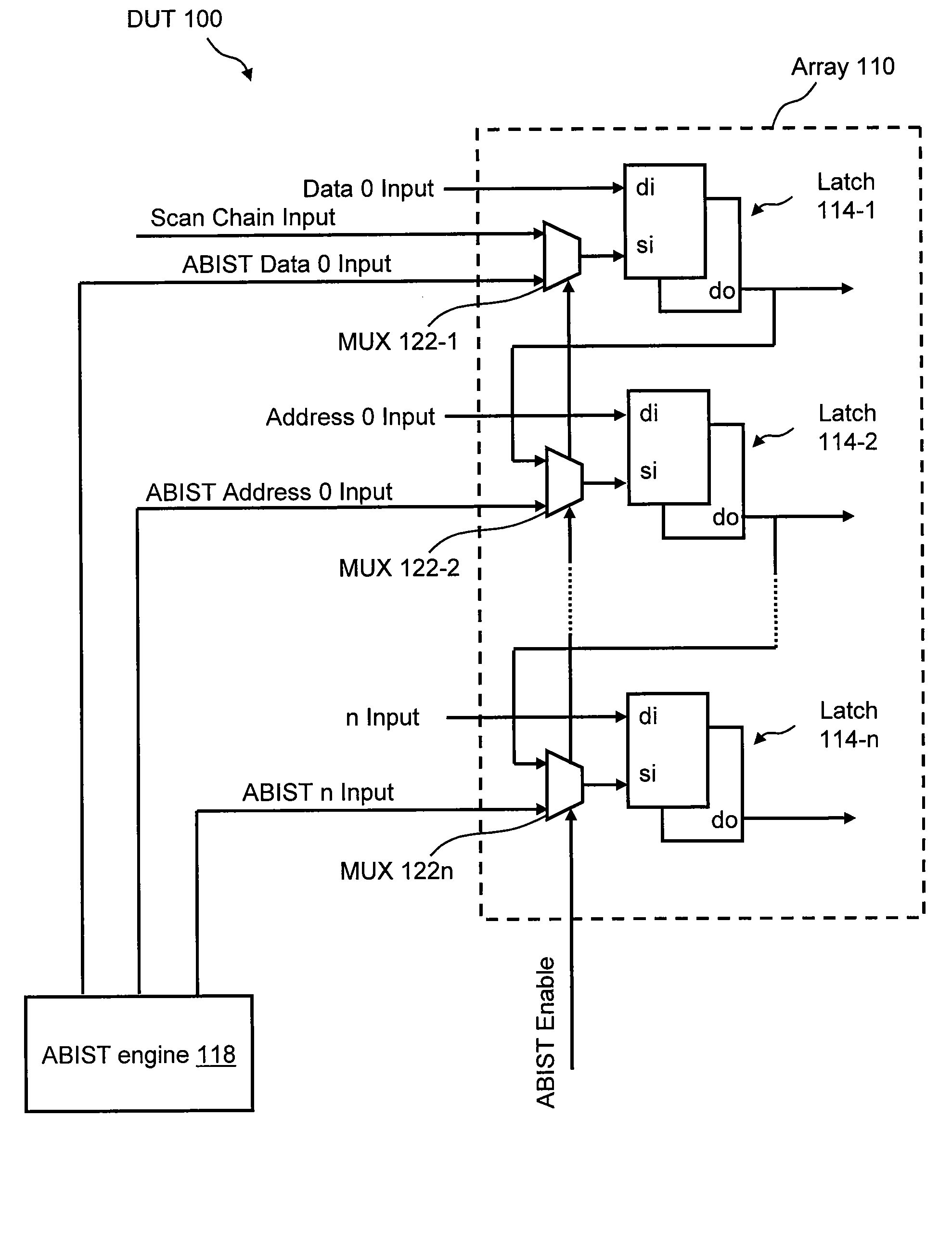

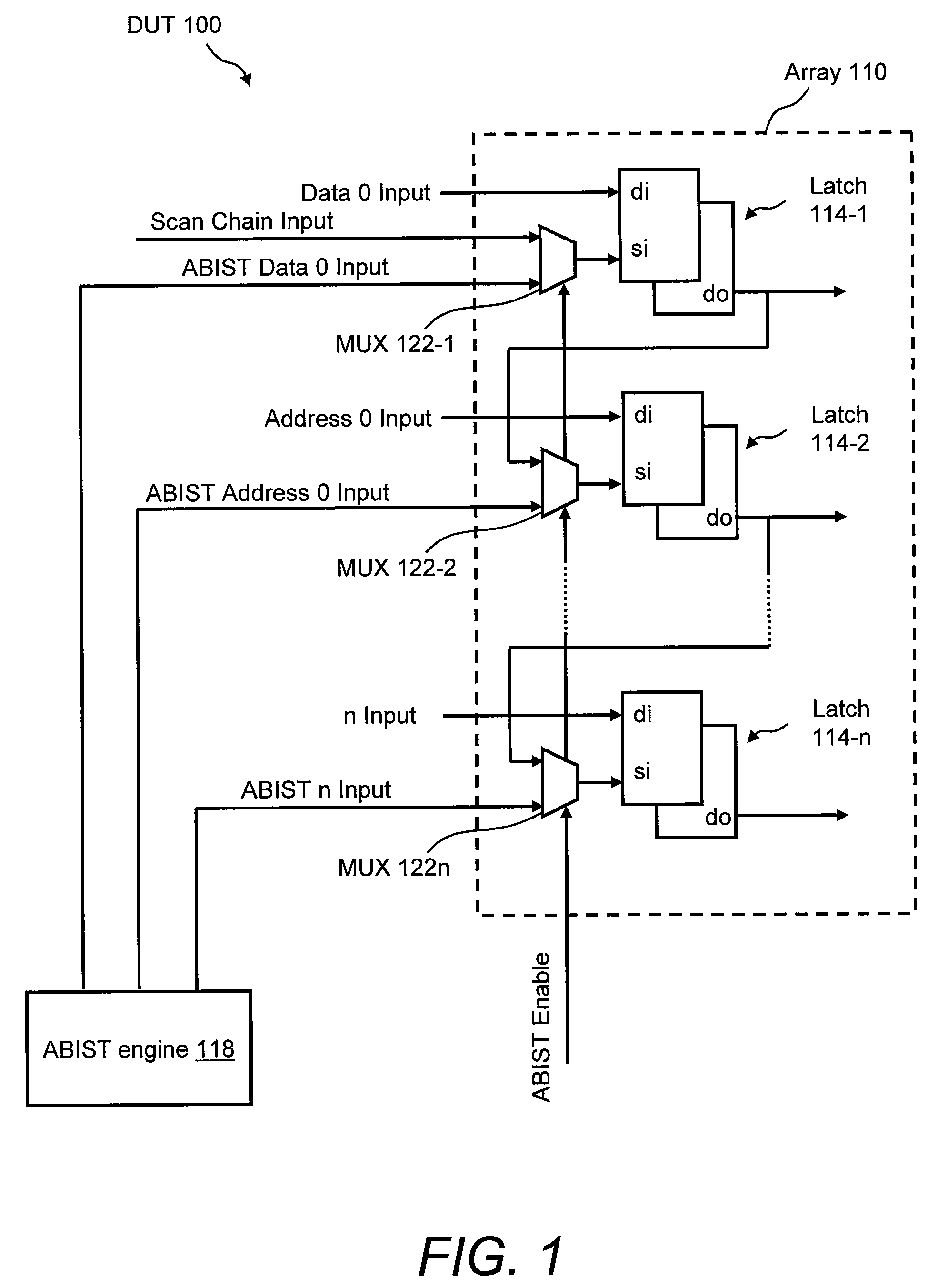

Method and apparatus for testing a random access memory device

InactiveUS20090287971A1Electronic circuit testingFunctional testingStatic random-access memoryRandom access memory

A method and apparatus for testing a random access memory device is provided. One embodiment involves providing an interface between Logic Built in Self Test (LBIST) and Array Built in Self Test (ABIST) paths for memory testing, including providing a cross-coupled NAND device with an LBIST test path; configuring the cross-coupled NAND device for interfacing ABIST and LBIST paths by modeling a worst case scenario for timing from a domino read static random access memory (SRAM) array; and modifying data in the cross-coupled NAND device using an LBIST controlled data path at essentially the latest point in time when a read may propagate from the array to provide full AC test coverage of down stream logic.

Owner:IBM CORP

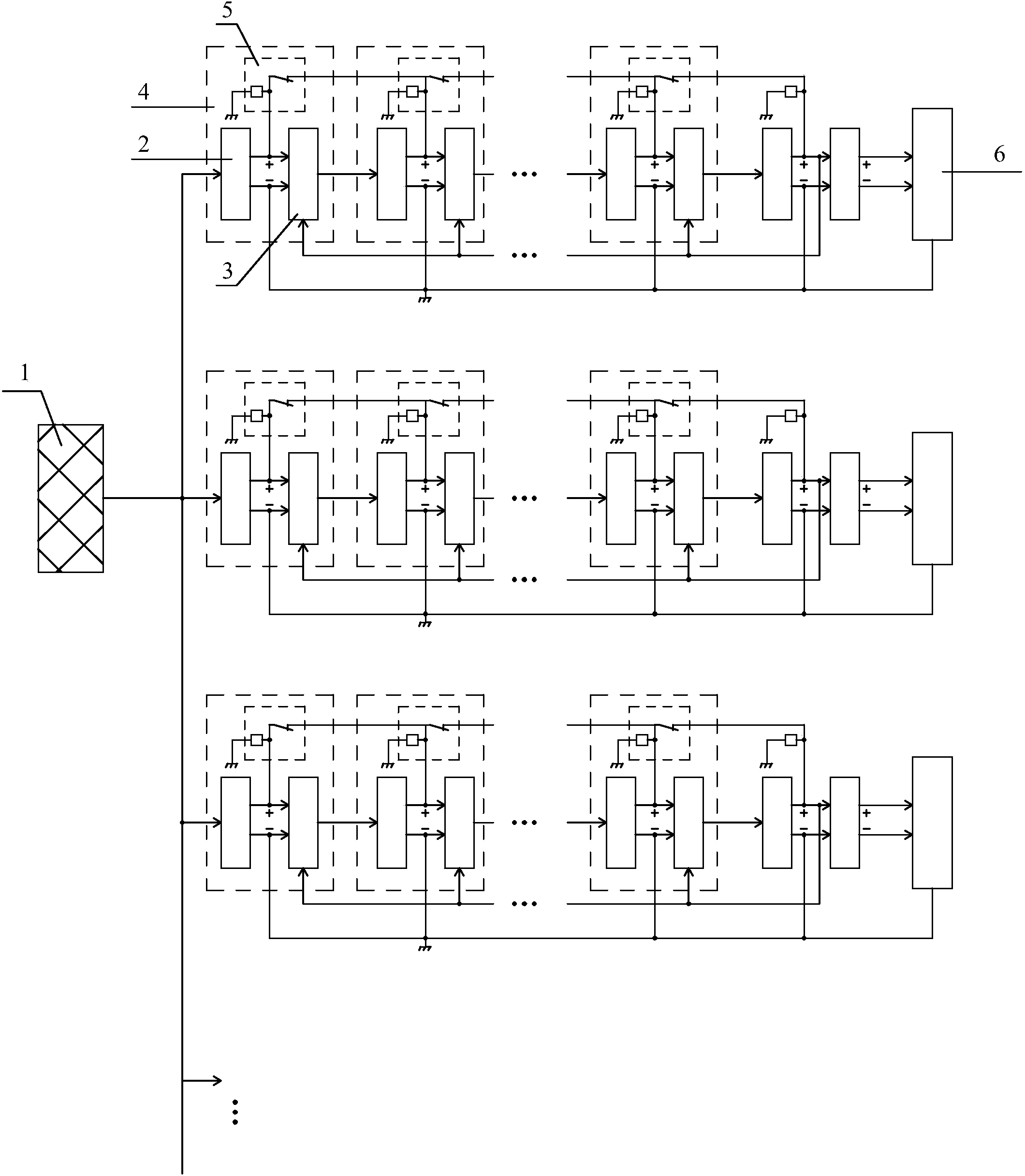

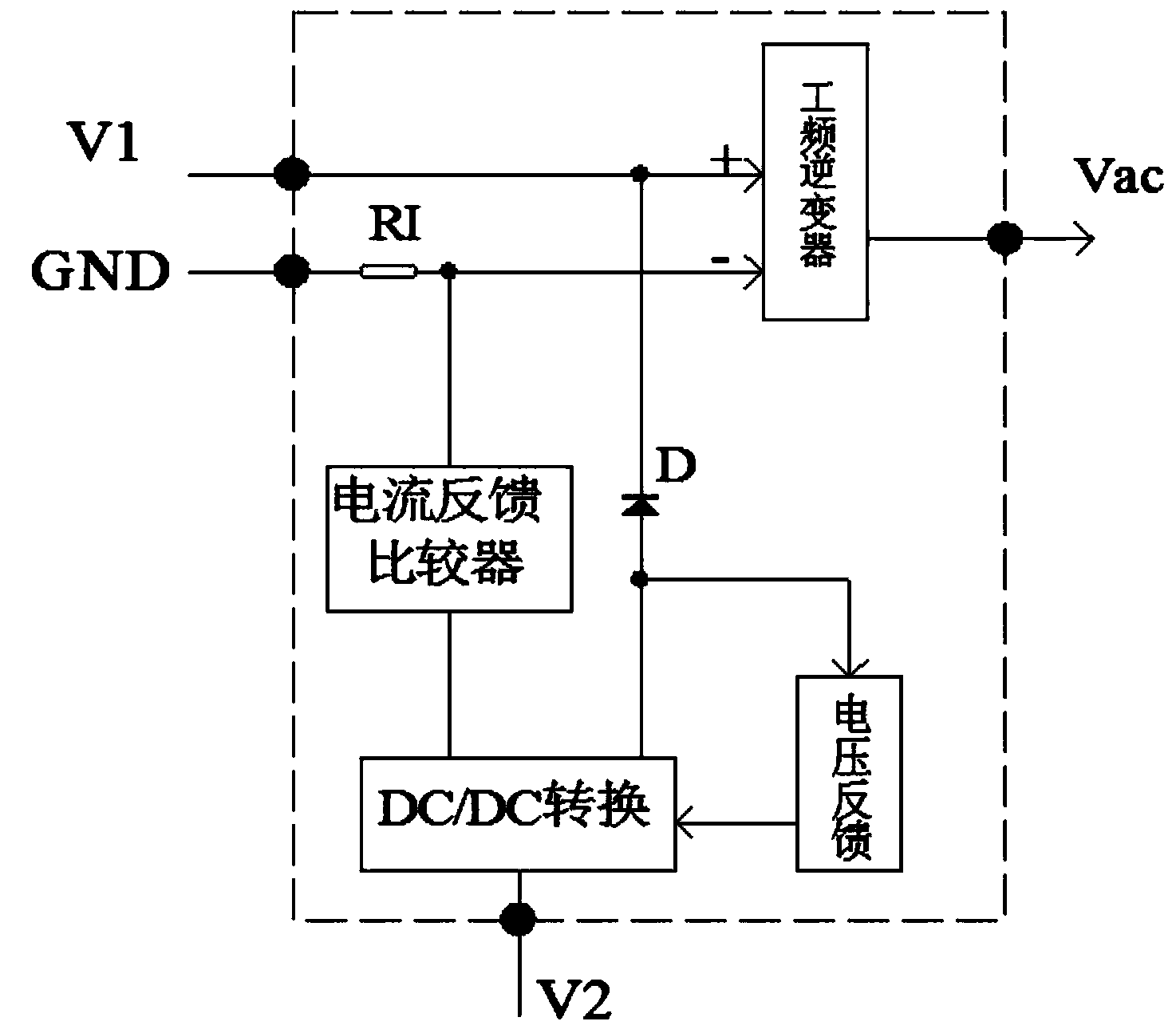

Energy-saving power adapter ageing testing device

The invention discloses an energy-saving power adapter ageing testing device and belongs to the technical field of a power adapter. A group of power adapter ageing testing array of the device is connected to a commercial power grid or at least two groups of power adapter ageing testing arrays are connected to the commercial power grid in parallel; each group of power adapter ageing testing array is formed by serially connecting N power adapter ageing testing units and then serially connecting the N power adapter ageing testing units to an electronic load; each power adapter ageing testing unit comprises a to-be-tested power adapter, a power supply ageing special module and a relay. Compared with the current power adapter ageing testing equipment, the energy-saving power adapter ageing testing device has the advantages that required power supply equipment capacity of the device is reduced to 15 to 20 percent of that of the current power adapter ageing testing equipment, 85 to 90 percent of electric energy can be saved, the electric energy is not consumed on a resistor any more, the energy consumption is reduced, meanwhile, the production cost and the pollution to environment are reduced, and a power adapter which can be applied to test comprises alternating current-direct current electronic equipment for conversion, such as an electric vehicle charger, an LED (light-emitting diode) illuminating power supply and a computer power adapter.

Owner:CHANGSHU RES INST OF DALIAN UNIV OF TECH CO LTD