Timing method and system for a processor array

A processor array and processor technology, applied in the direction of electrical digital data processing, instruments, combination of various digital computers, etc., can solve the problems of waste of chip resources, increase additional costs, etc., and achieve the goal of improving energy consumption ratio and timing accuracy Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] Preferred embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings, wherein the accompanying drawings constitute a part of the application and together with the embodiments of the present invention are used to explain the principle of the present invention and are not intended to limit the scope of the present invention.

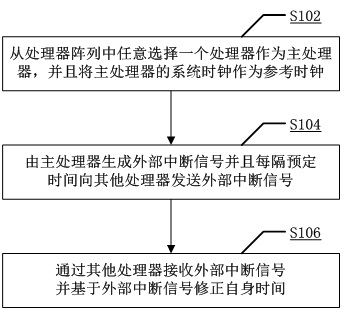

[0030] A specific embodiment of the present invention discloses a timing method of a processor array, such as figure 1 shown. The timing method of the processor array includes: step S102, randomly selecting a processor from the processor array as a main processor, and using the system clock of the main processor as a reference clock; step S104, generating an external interrupt signal by the main processor and Sending an external interrupt signal to other processors every predetermined time; and Step S106, other processors receive the external interrupt signal and correct their own time based ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More