Method, device and chip for cross-chip signal synchronization

A signal synchronization and cross-chip technology, applied in the direction of signal generation/distribution, can solve problems such as chip clock signal delay, and achieve the effect of eliminating delay errors

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

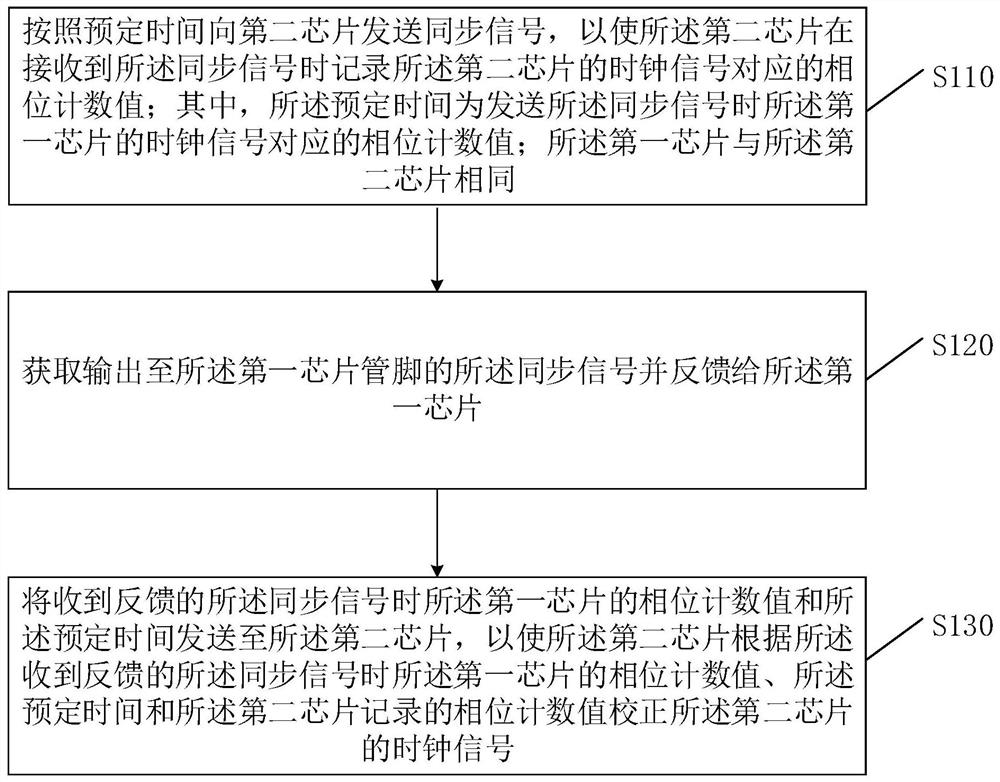

[0041] like figure 1 As shown, it is a schematic flowchart of a method for synchronizing signals across chips provided by Embodiment 1 of the present invention. This embodiment is applicable to the application scenario of synchronously correcting clock signals between two chips, and the method can be executed by a device for synchronizing signals across chips, which can be a chip; in this embodiment of the application, the first chip is used As an executive subject, the method specifically includes the following steps:

[0042] S110. Send a synchronization signal to the second chip according to a predetermined time, so that the second chip records the phase count value corresponding to the clock signal of the second chip when receiving the synchronization signal; The phase count value corresponding to the clock signal of the first chip when the synchronization signal is mentioned; the first chip is the same as the second chip;

[0043] Because in the existing clock correctio...

Embodiment 2

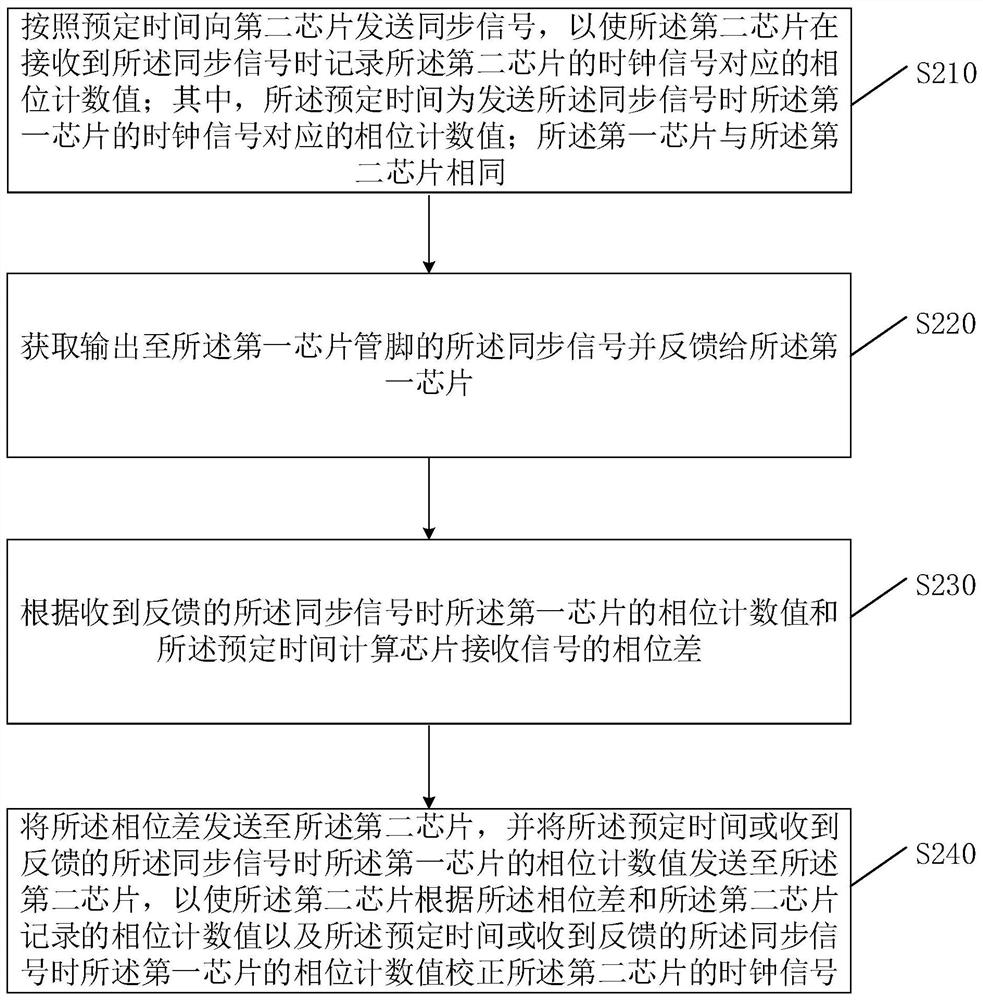

[0055] like figure 2 What is shown is a schematic flowchart of a method for synchronizing signals across chips provided by Embodiment 2 of the present invention. On the basis of the first embodiment, this embodiment also provides another cross-chip signal synchronization method, so as to realize precise synchronization between the first chip and the second chip. The method specifically includes:

[0056] S210. Send a synchronization signal to the second chip according to a predetermined time, so that the second chip records the phase count value corresponding to the clock signal of the second chip when receiving the synchronization signal; wherein, the predetermined time is The phase count value corresponding to the clock signal of the first chip when sending the synchronization signal; the first chip is the same as the second chip;

[0057] When correcting the clock of the second chip, the first chip sends a synchronization signal to the second chip according to the predet...

Embodiment 3

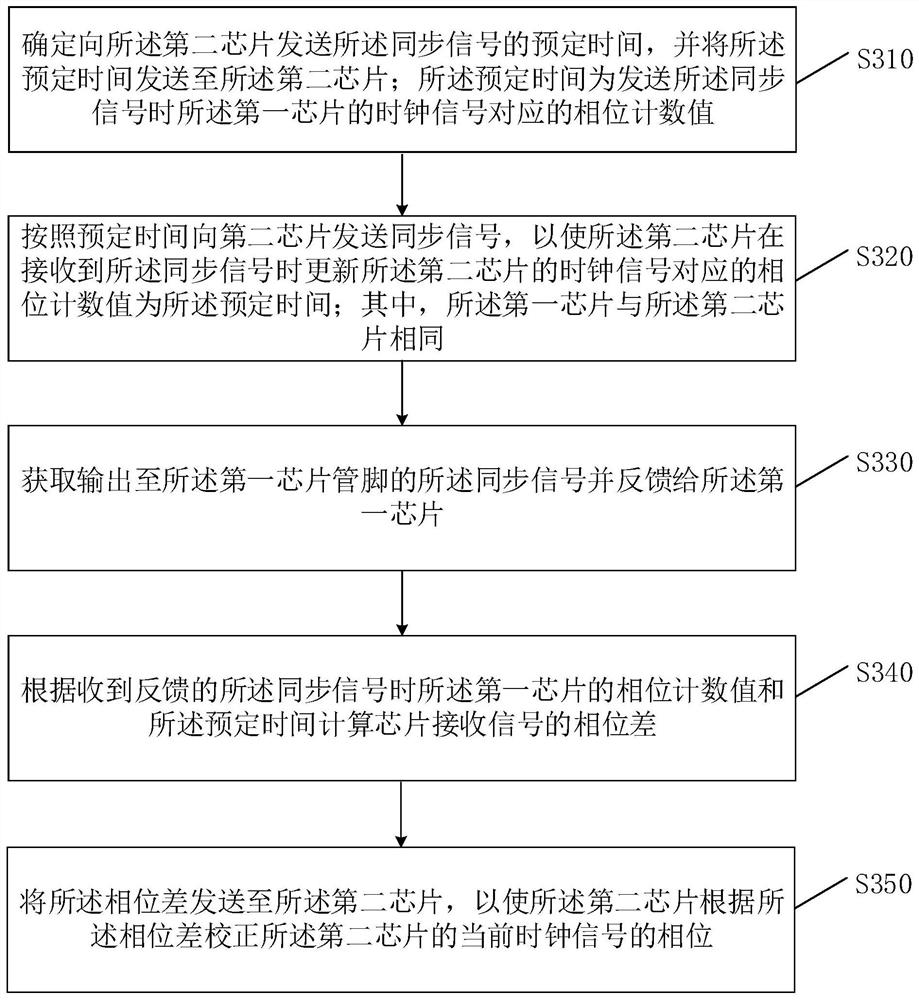

[0070] like image 3 What is shown is a schematic flowchart of a method for synchronizing signals across chips provided by Embodiment 2 of the present invention. On the basis of the second embodiment, this embodiment also provides another cross-chip signal synchronization method, so as to realize precise synchronization between the first chip and the second chip. The method specifically includes:

[0071] S310. Determine a predetermined time for sending the synchronization signal to the second chip, and send the predetermined time to the second chip; the predetermined time is the clock of the first chip when sending the synchronization signal The phase count value corresponding to the signal;

[0072] Specifically, before the first chip sends the synchronization signal to the second chip at the predetermined time, the first chip may predetermine a predetermined time for sending the synchronization signal to the second chip, and send the determined predetermined time to the s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More