Original bit error rate reduction method for three-dimensional flash memory

A technology of original bit error rate and flash memory, which is applied in information storage, static memory, read-only memory, etc., and can solve problems such as high delay

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] In order to make the objectives, technical solutions, and advantages of the present invention clearer, the following further describes the present invention in detail with reference to the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, but not to limit the present invention. In addition, the technical features involved in the various embodiments of the present invention described below can be combined with each other as long as they do not conflict with each other.

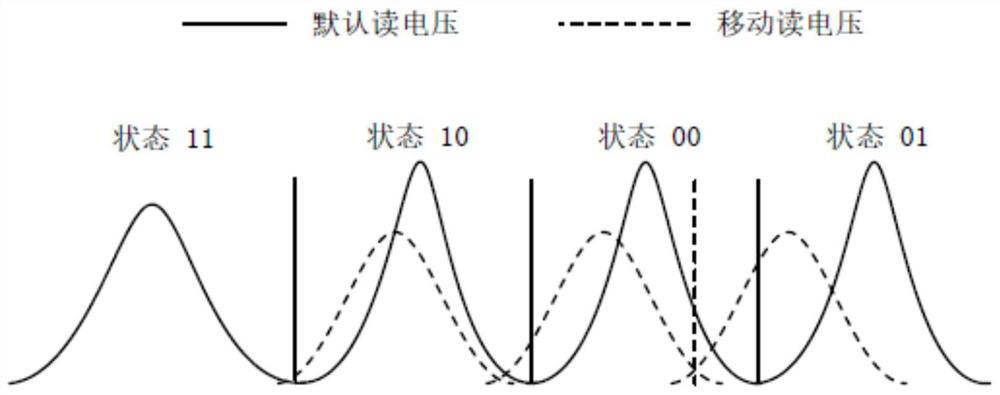

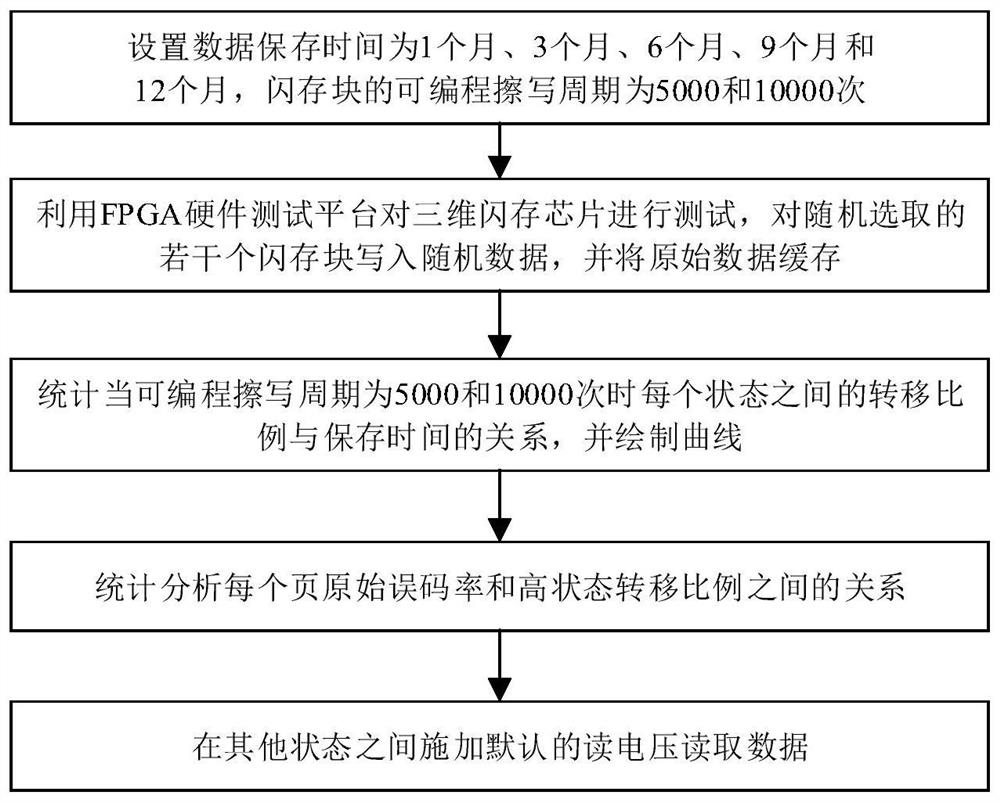

[0031] The design structure diagram of the present invention is as figure 1 As shown, for three-dimensional MLC (Multi-Level Cell) flash memory, each cell stores two bits of information, and has four storage states, namely state 11, state 10, state 00 and state 01, where the left bit is called the highest The most significant bit (Most Significant Bit, MSB), the right bit is called the Least Significant...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More