Novel FPGA chip layout optimization method

A chip layout and optimization method technology, applied in the field of FPGA, can solve the problems of adjustment, poor flexibility, and difficult adjustment of adjustment weights, etc., and achieve the effect of flexible debugging process, strong adaptability and pertinence, and avoiding limitations

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] The specific embodiments of the present invention will be further described below in conjunction with the accompanying drawings.

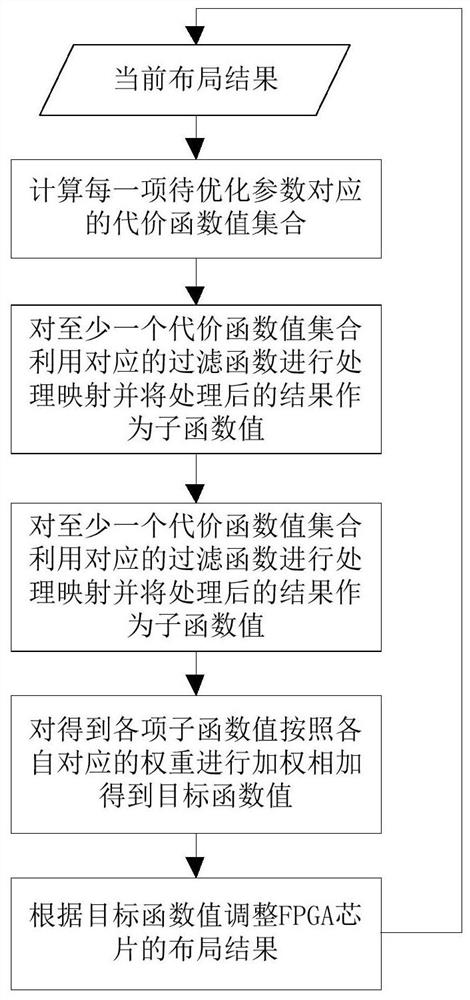

[0032] This application discloses a novel FPGA chip layout optimization method, the method includes the following steps, please refer to figure 1 :

[0033] Step S1, calculating a set of cost function values corresponding to each parameter to be optimized under the current layout of the FPGA chip. Among them, the parameters to be optimized include wire length (NET WIRELENGTH), total wire length (TOTAL WIRELENGTH), path timing margin (SLACK), wire congestion (CONGESTION), power consumption distribution (POWER), clock tree range ( at least one of CLOCKSPAN).

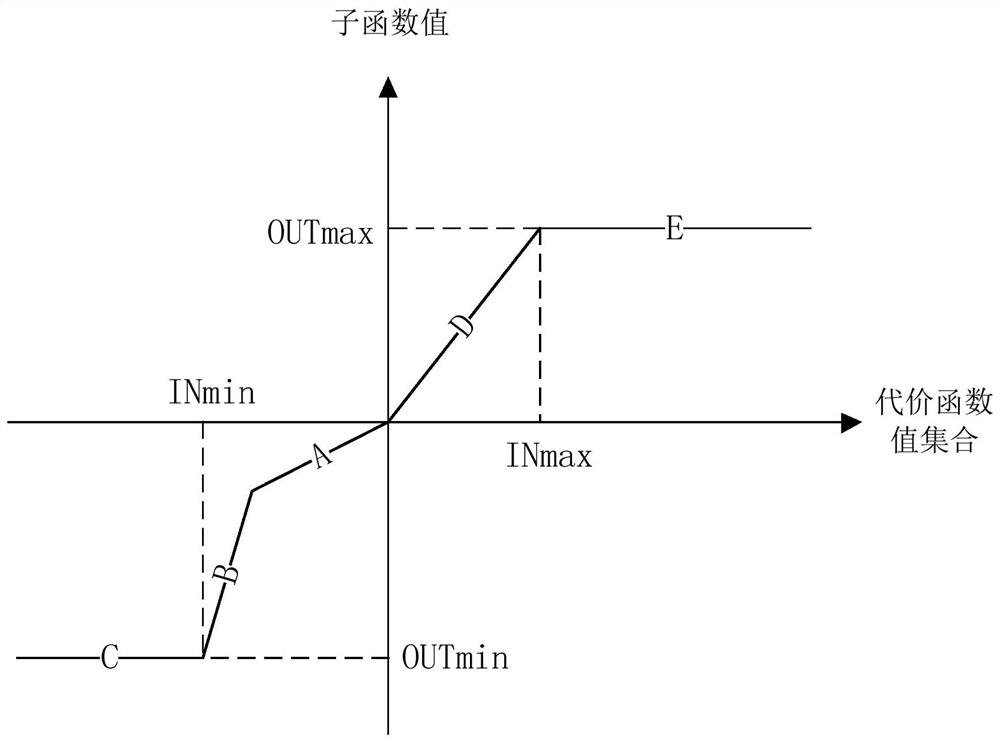

[0034] The cost function value set corresponding to at least one parameter to be optimized includes several sub-costs, and each sub-cost is the value of the parameter to be optimized corresponding to each category obtained by dividing the FPGA chip according to a predetermined classi...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap