Semiconductor device

A semiconductor and device technology, applied in the field of semiconductor devices, can solve the problems of high global bit line load and complex wiring path, etc., and achieve the effect of flexible layout design, simplified wiring path, and reduced overall distance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

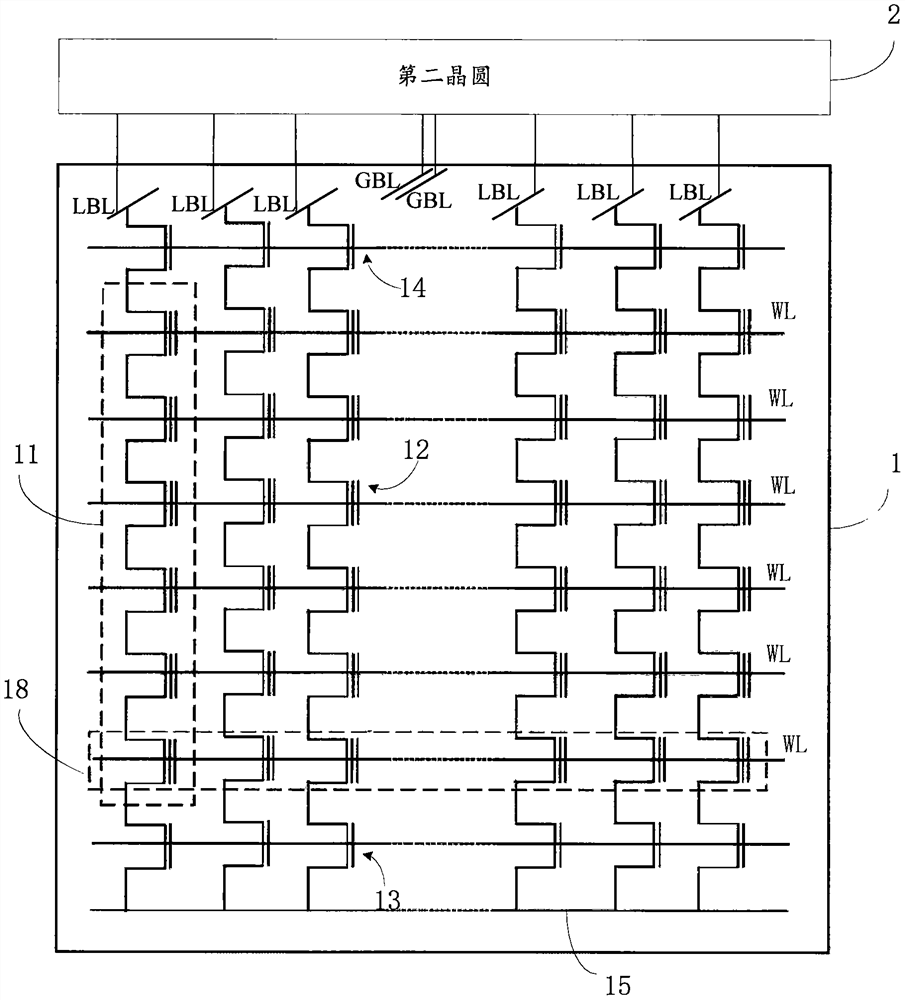

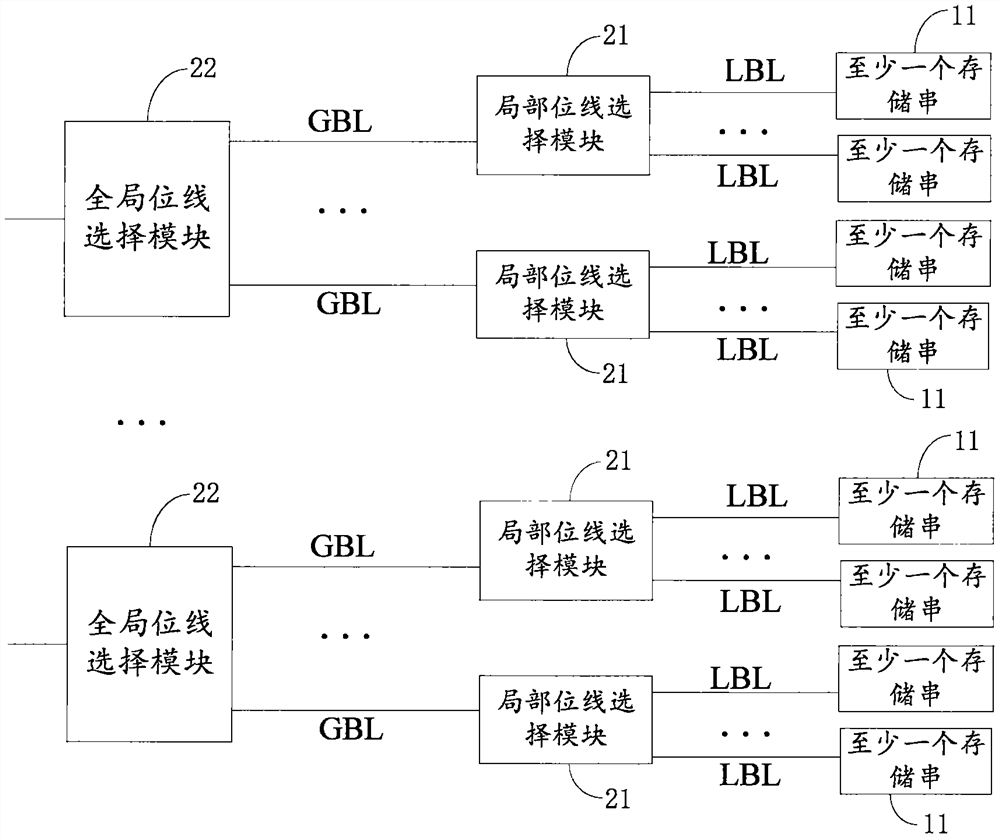

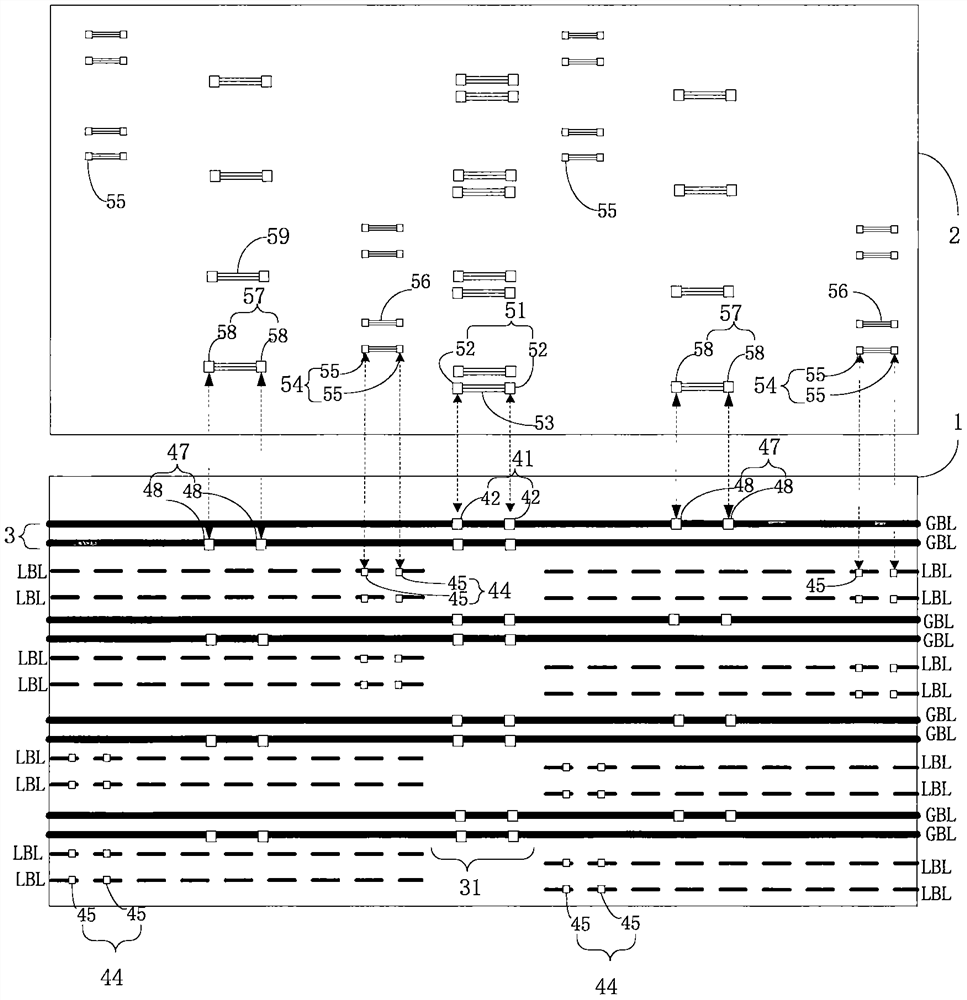

Embodiment Construction

[0035] Specific structural and functional details disclosed herein are representative only and for purposes of describing example embodiments of the present invention. This invention may, however, be embodied in many alternative forms and should not be construed as limited to only the embodiments set forth herein.

[0036] In describing the present invention, it is to be understood that the terms "central", "lateral", "upper", "lower", "left", "right", "vertical", "horizontal", "top", The orientation or positional relationship indicated by "bottom", "inner", "outer", etc. is based on the orientation or positional relationship shown in the drawings, and is only for the convenience of describing the present invention and simplifying the description, rather than indicating or implying the referred device Or elements must have a certain orientation, be constructed and operate in a certain orientation, and thus should not be construed as limiting the invention. In addition, the te...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More