Current biasing circuit for fast wake-up of the chip

A technology of current bias and bias current, which is applied in the direction of adjusting electrical variables, instruments, control/regulation systems, etc., and can solve problems such as long chip wake-up time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] Specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings. It should be understood that the specific embodiments described here are only used to illustrate and explain the present invention, and are not intended to limit the present invention.

[0020] In the embodiments of the present invention, the terms "first", "second", "third", "fourth" and so on are only used for distinguishing descriptions, and should not be understood as indicating or implying relative importance.

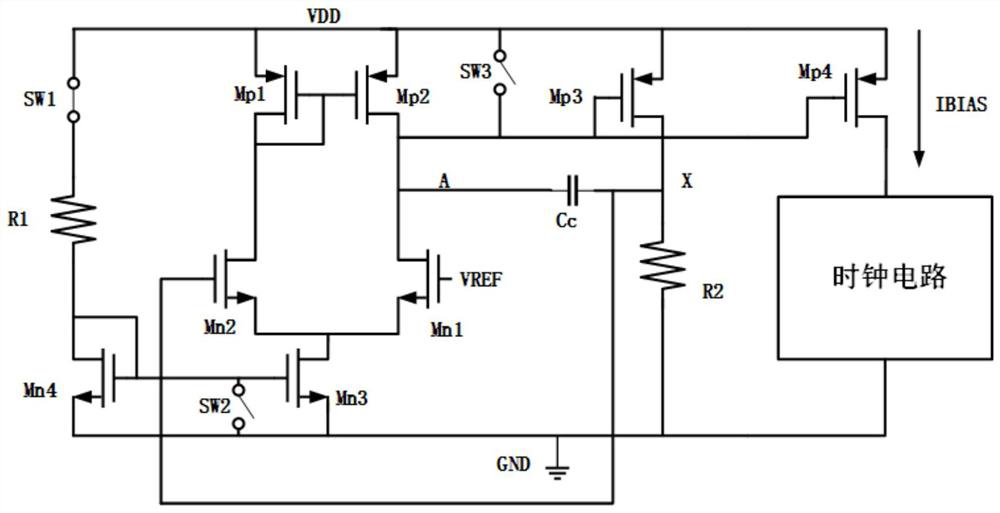

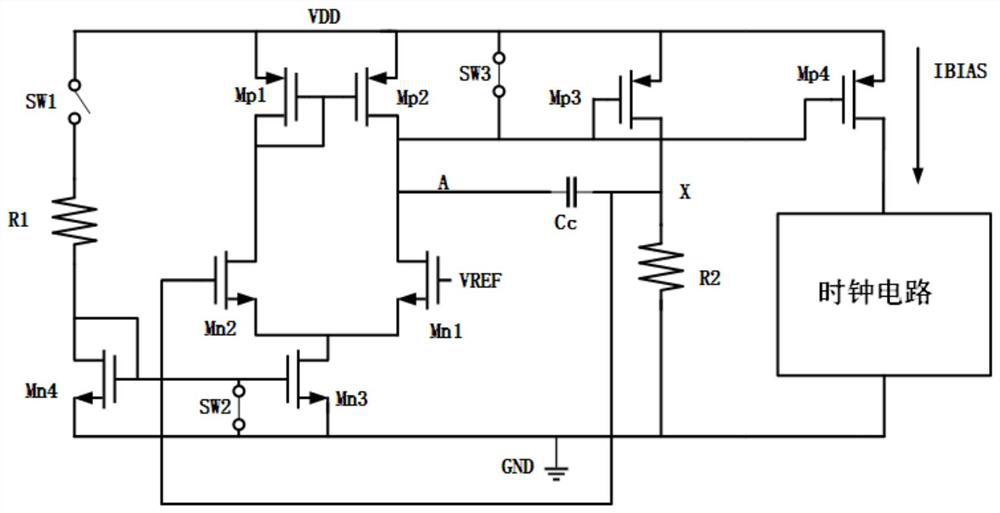

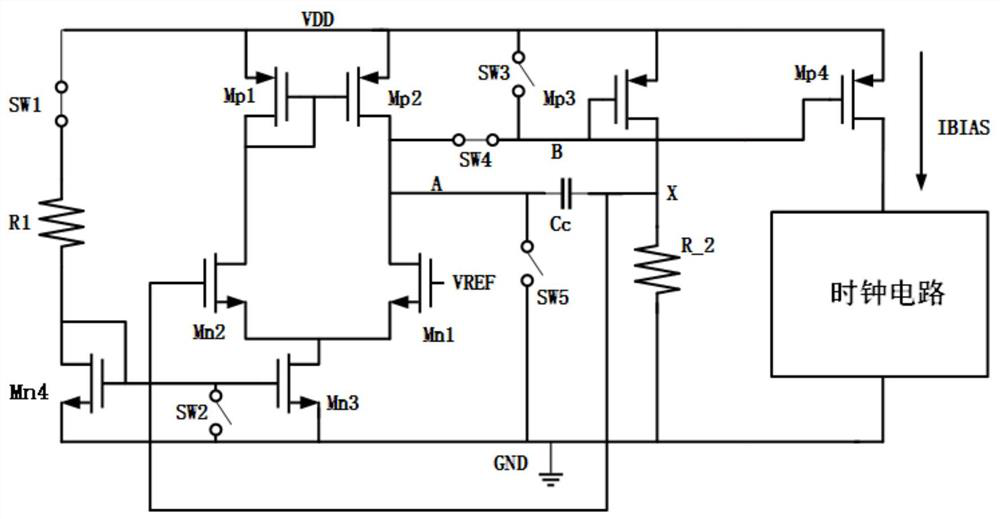

[0021] figure 1 It is a circuit diagram of an existing current bias circuit in a normal working state. Such as figure 1 As shown, the existing current bias circuit includes a bias current generating circuit, a low-precision bias current generating circuit and a current output branch. The bias current generation circuit includes: a first PMOS transistor Mp1, a second PMOS transistor Mp2, a first NMOS transistor Mn1, a second NMOS ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More