Method for reducing input power frequency ripples

A ripple and input power technology, applied in the field of reducing input power frequency ripple, can solve problems such as inability to guarantee aging and affect product production, and achieve the effect of guaranteeing normal aging and reducing input power frequency ripple

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

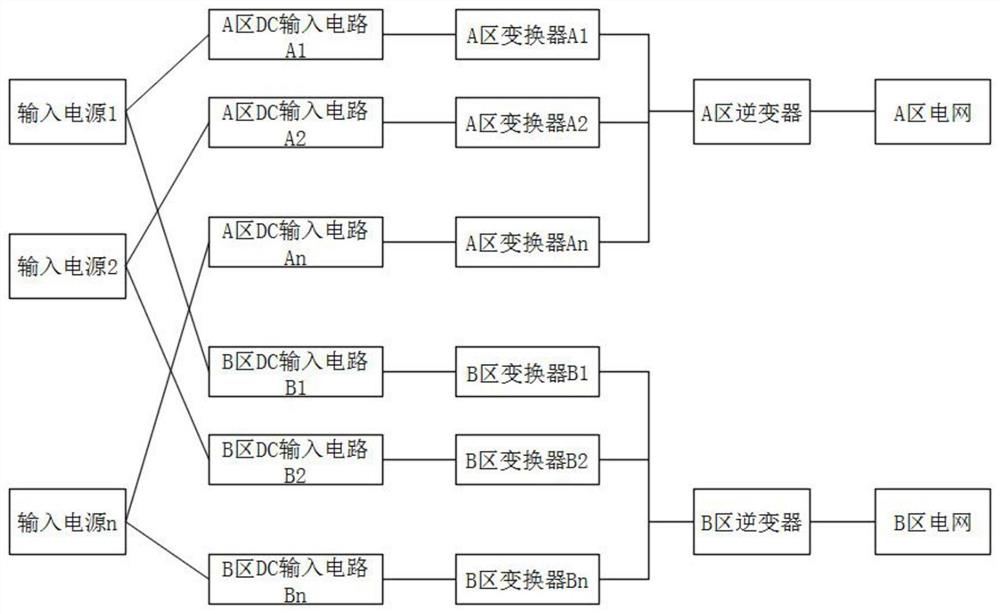

[0036] When the two DC inputs are connected in parallel, in the present invention, one DC-DC conversion circuit connected to the power grid in area A and one DC-DC conversion circuit connected to the power grid in area B are selected instead of the traditional two-way DC-DC conversion circuit connected to the same phase of the power grid. DC-DC conversion circuit. Because there is a fixed phase difference between the power grid in area A and the power grid in area B, the input power frequency ripple of the two DC-DC conversion circuits also has a fixed phase difference, and the input power frequency ripple after the two are connected in parallel will be significantly reduced. Assume that the input power frequency ripple of each DC-DC conversion circuit is K sinωt, that is, the peak-to-peak value of each input power frequency ripple is 2K, if connected to the same phase of the power grid, the input power frequency ripple after parallel connection is K sinωt, that is, the peak-t...

Embodiment 2

[0038] When there are three or more DC-DC conversion circuit inputs connected in parallel, if the number of parallel circuits is an integer multiple of three R, the input power frequency ripple after parallel connection is R·(K·sinwt+K·sin(120+ ωt)+K·(ωt+240))=R×0=0, that is, the peak-to-peak value of the input ripple after parallel connection is 0; After parallel connection, the input ripple is 0, and the input ripple of the remaining channel is not canceled, then the ripple expression after parallel connection is K sinωt, that is, the peak-to-peak value of the input power frequency ripple after parallel connection is 2K; if When the number of parallel circuits is not an integer multiple of three, and the remainder is 2, since the input ripple is 0 after the integer multiple of 3 is connected in parallel, the input ripple of the remaining 2 channels is not canceled out, and the ripple expression after parallel connection is The formula K·sinωt+K·sin(120°+ωt)=K·sin(ωt-120°), t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More