JTAG data capture and analysis system

An analysis system and data capture technology, applied in the direction of electrical digital data processing, instruments, and faulty computer hardware detection, can solve problems such as logic design errors, affecting the efficiency of software and hardware debugging, and JTAG unable to communicate normally.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] In order to make the purpose, technical solutions and advantages of the embodiments of the present invention more clear, the implementation manners of the present invention will be described in detail below in conjunction with the drawings and embodiments.

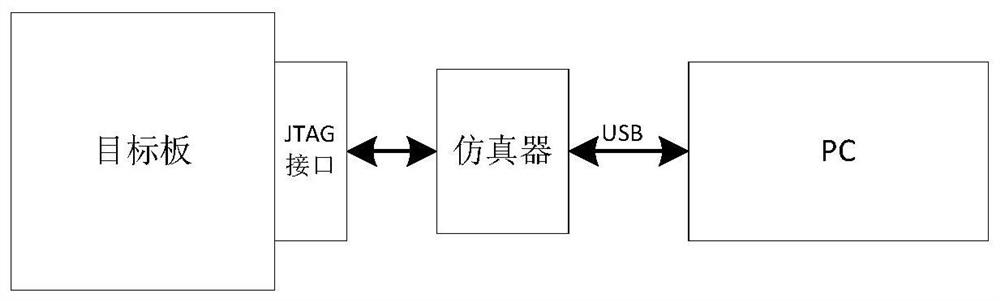

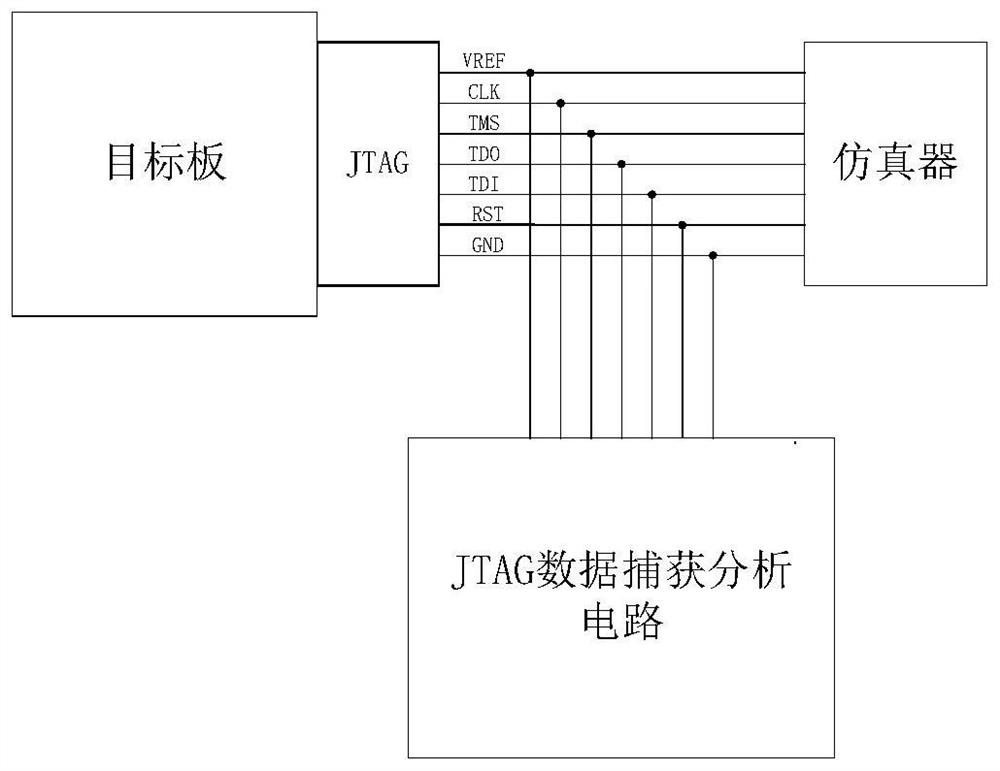

[0025] The invention is a JTAG data capturing and analyzing system, which is mainly used for diagnosing the communication failure of the JTAG debugging interface. refer to figure 2 , during the debugging process for the target processor, it is installed between the target processor and the emulator, connected to each communication signal line of the JTAG debugging interface, independent of the target processor and the emulator, and connected externally between the two Collect the JTAG communication signals, and analyze and detect communication faults based on the collected signals.

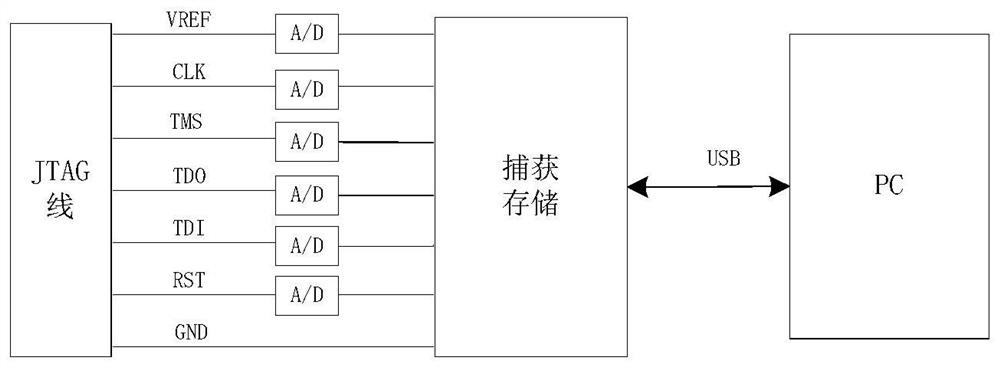

[0026] Specifically, the system of the present invention includes three main modules, as follows:

[0027] The JTAG communication s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More