Architecture capable of interconnecting HART communication protocol chips and use method thereof

A communication protocol and chip technology, which is applied in the architecture field of interconnectable HART communication protocol chips, can solve the problems of lack of interoperability of smart instruments, large amount of wiring, backward equipment interfaces, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0049] In order to better understand the technical solutions of the present invention, the specific implementation manners of the present invention will be further described in detail below in conjunction with the accompanying drawings and examples. The same reference numbers in the figures indicate functionally identical or similar elements. While various aspects of the embodiments are shown in drawings, the drawings are not necessarily drawn to scale unless specifically indicated.

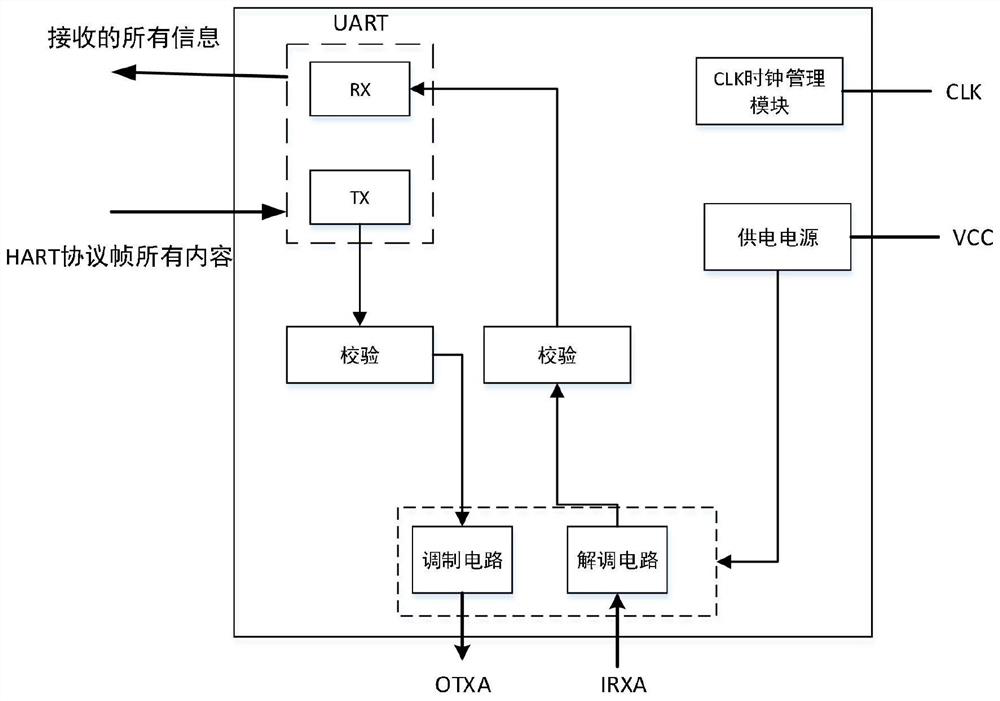

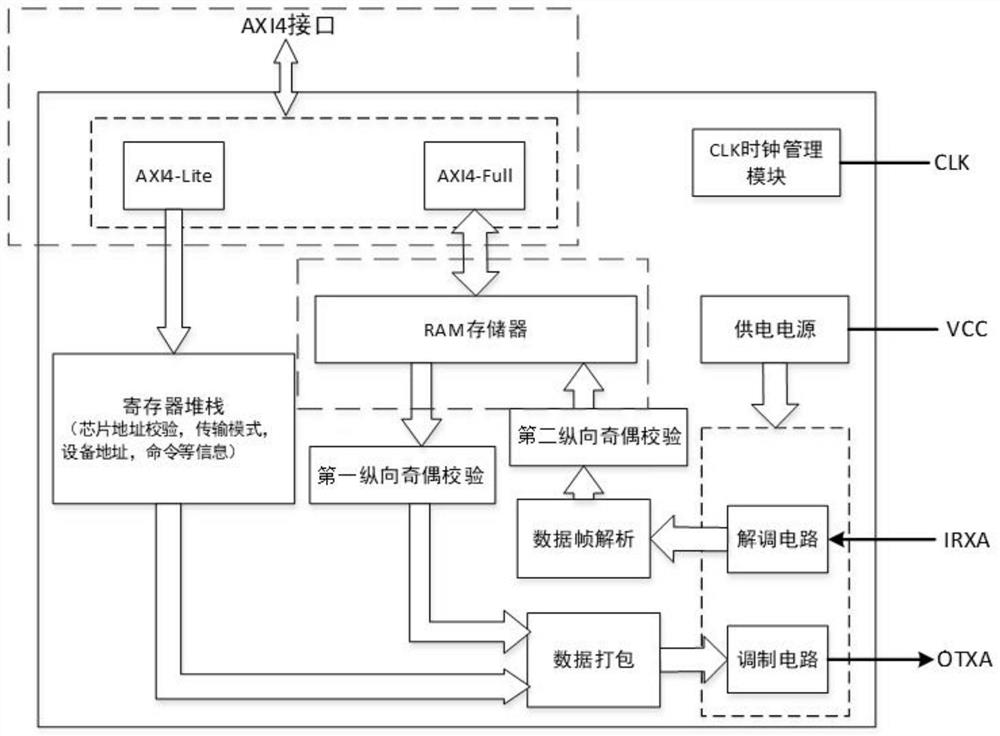

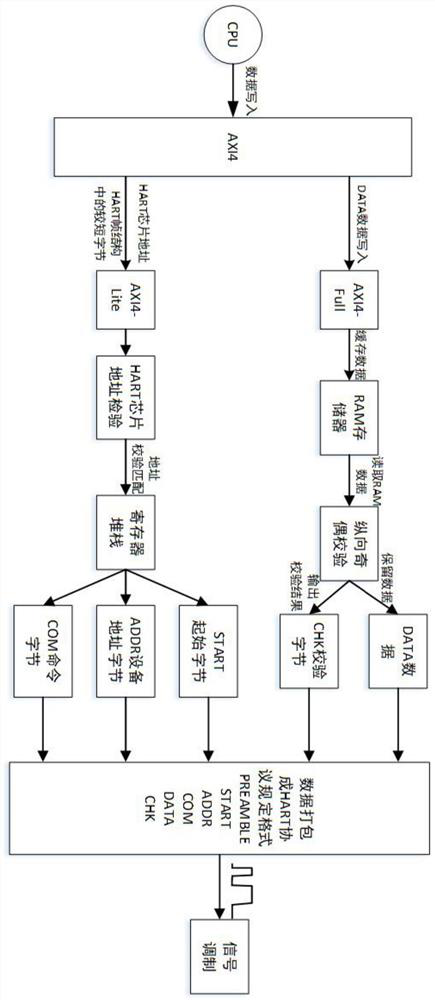

[0050] The improved design diagram of the HART chip architecture designed by the present invention is as follows figure 2 shown, with traditional architecture figure 1 Compared, the present invention has added two parts of AXI4 bus and RAM memory on the basis of traditional HART chip, the architecture of interconnectable HART communication protocol chip that the present invention proposes comprises following module: AXI4 bus module, register stack module, RAM memory module, Longitudinal parity...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More