Neural network in-memory computing device based on communication lower bound and acceleration method

A neural network and computing device technology, applied in biological neural network models, energy-saving computing, neural architecture, etc., can solve problems such as inability to guarantee the optimality of data flow schemes, lack of theoretical analysis support, etc., and achieve the effect of reducing the amount of data access

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

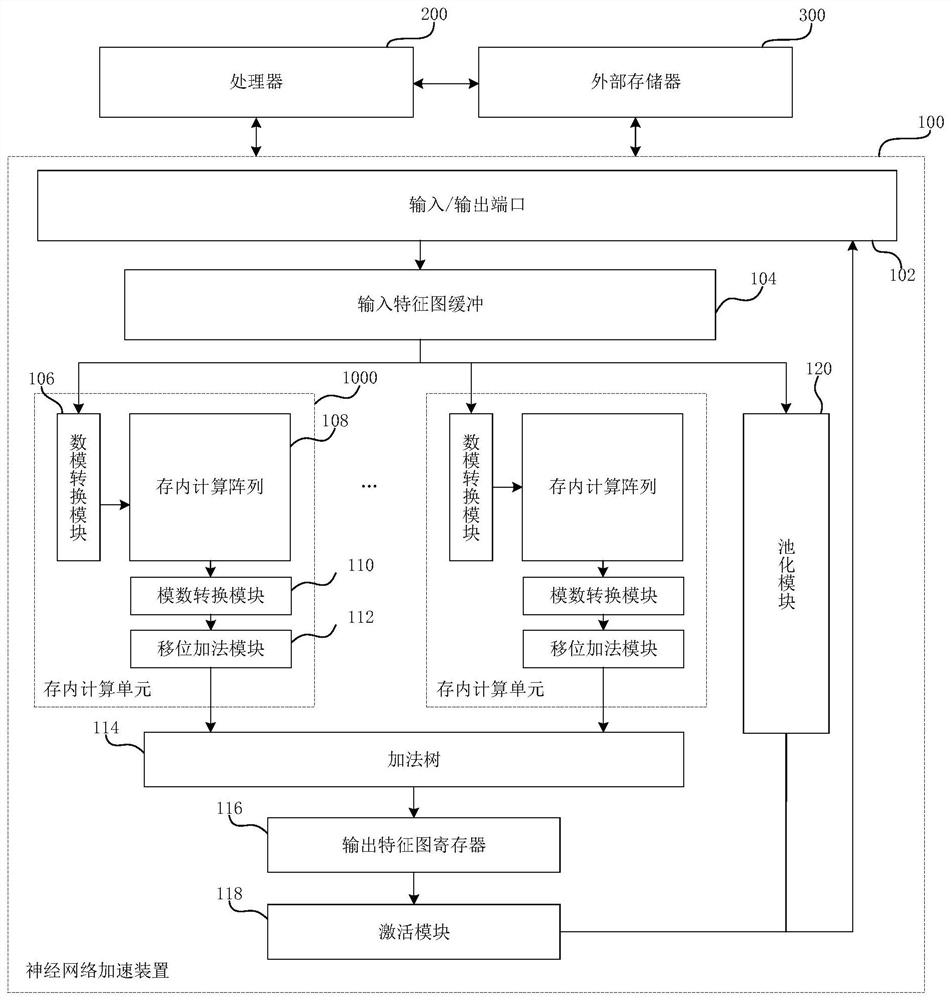

[0045] Embodiment 1. Neural network in-memory computing device based on communication lower bound, such as Figure 1-5 As shown, it includes a neural network acceleration device 100, a processor 200 and an external memory 300, and the neural network acceleration device 100 is connected to the processor 200 and the external memory 300 respectively; the processor 200 is used to control the process of the neural network acceleration device 100 and Carry out the calculation of some special layers (such as Softmax layer, etc.); the external memory 300 stores the weight data required in the neural network calculation process, the input feature map data, and the output feature map data of each layer in the layer-by-layer calculation process.

[0046] The processor 200 and the external memory 300 are signal-connected to each other, and the processor 200 and the external memory 300 belong to the prior art, so a detailed description thereof will not be given.

[0047] The neural network...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More