Method for preventing layer staggering in lamination of multi-layer circuit board

A multi-layer circuit, error-proofing technology, applied in the direction of multi-layer circuit manufacturing, printed circuit, printed circuit manufacturing, etc., can solve the problems of high labor intensity and high scrap rate, reduce labor intensity, reduce scrap rate and high accuracy Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

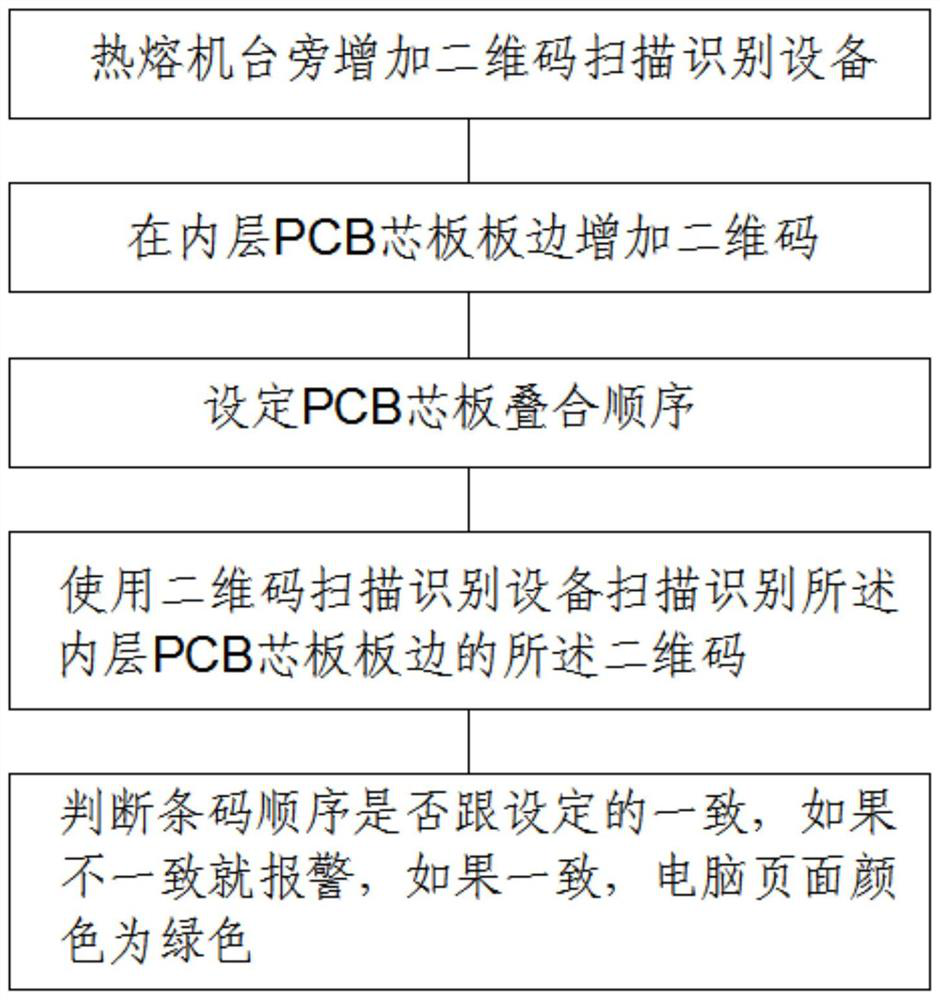

[0028] Please refer to figure 1 , in the first embodiment of the present invention, the method for laminating the error prevention layer of a multilayer circuit board includes the following steps:

[0029] S1: Add a QR code scanning recognition device next to the hot-melt machine;

[0030] S2: Add a QR code on the edge of the inner PCB core board;

[0031] S3: Set the stacking sequence of PCB core boards;

[0032] S4: Use a two-dimensional code scanning recognition device to scan and identify the two-dimensional code on the edge of the inner PCB core board;

[0033] S5: Judging whether the barcode sequence is consistent with the setting, if not, it will alarm, if it is consistent, the color of the computer page is green.

[0034] The two-dimensional code scanning recognition device is connected to a computer, and the two-dimensional code scanning recognition device is adapted to the software in the computer.

[0035] The two-dimensional code information includes the materi...

no. 2 example

[0043] Based on the method for laminating an anti-error layer on a multilayer circuit board provided in the first embodiment of the present application, the second embodiment of the present application proposes another method for laminating an anti-error layer on a multilayer circuit board. The second embodiment is only a preferred mode of the first embodiment, and the implementation of the second embodiment will not affect the independent implementation of the first embodiment.

[0044] The second embodiment of the present invention will be further described below in conjunction with the drawings and implementation methods.

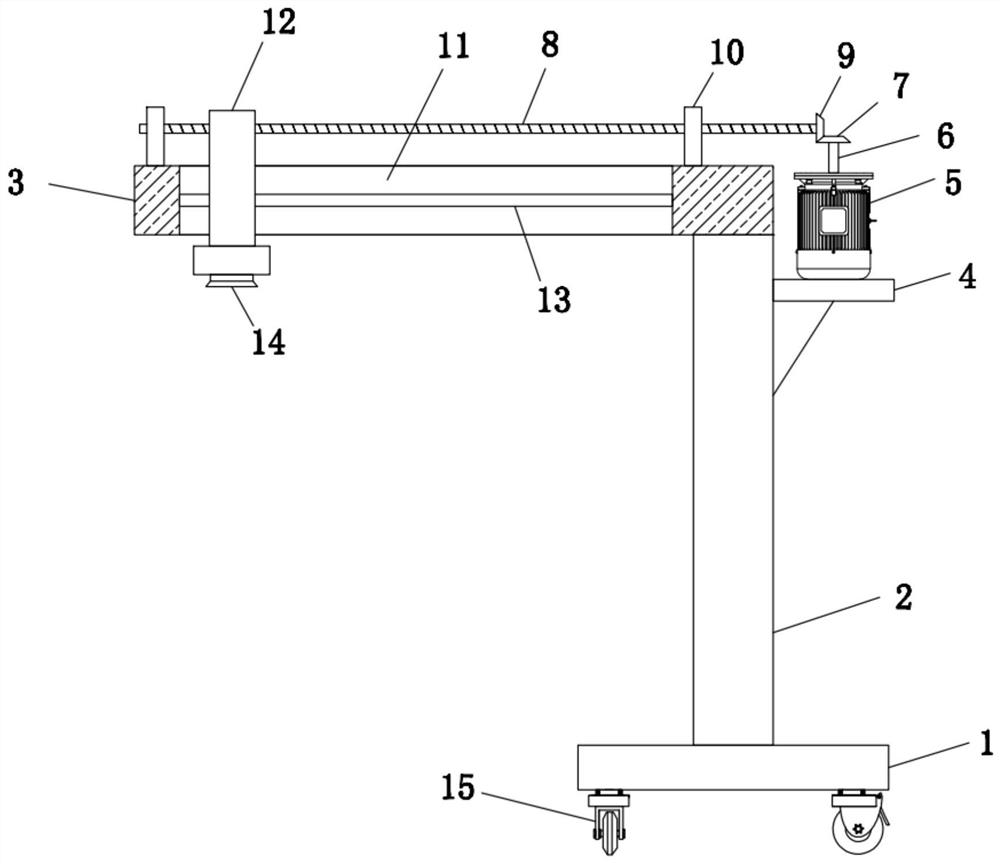

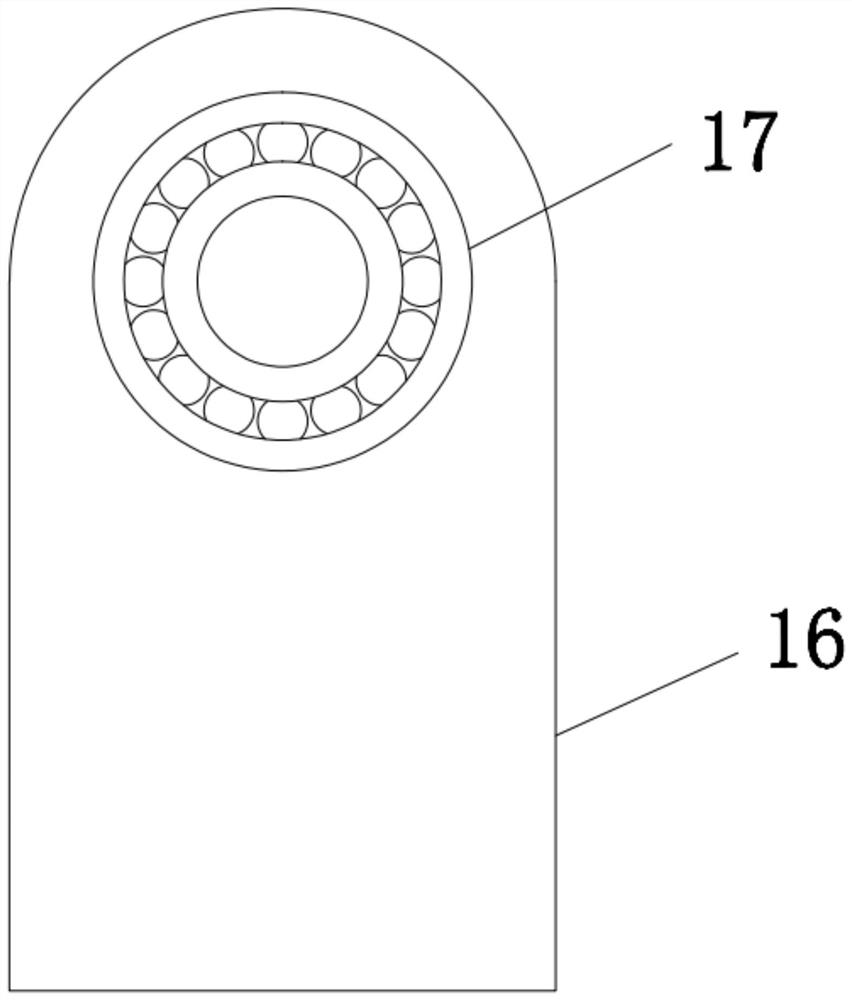

[0045] Please refer to Figure 2-Figure 3 The difference between this embodiment and the first embodiment is that the two-dimensional code scanning recognition device includes a base 1, a column 2 is fixedly installed on the top side of the base 1, and a top plate 3 is fixedly installed on the top side of the column 2 , a lateral moving device is instal...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More