ESD protection transistor and ESD protection method of CMOS device

A technology of transistors and devices, applied in the field of electrostatic protection, can solve problems such as degradation, CMOS device damage, and failure performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

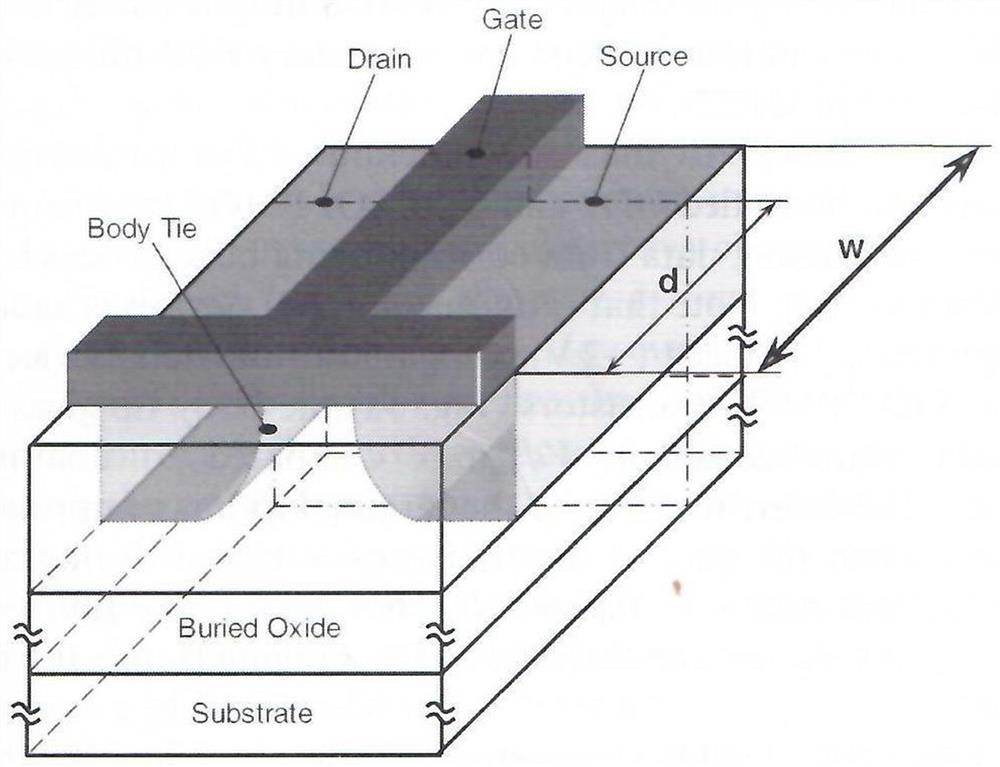

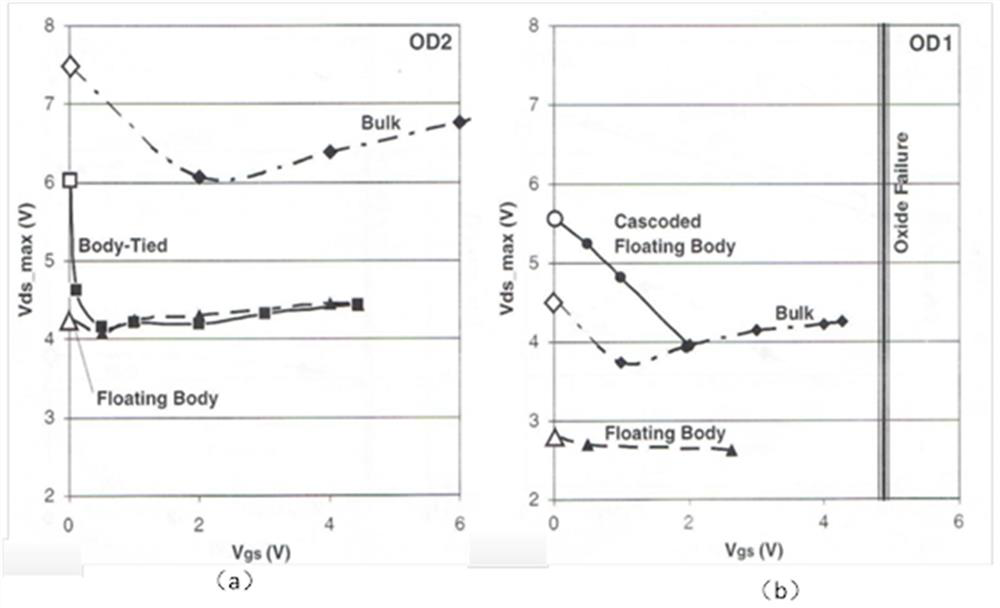

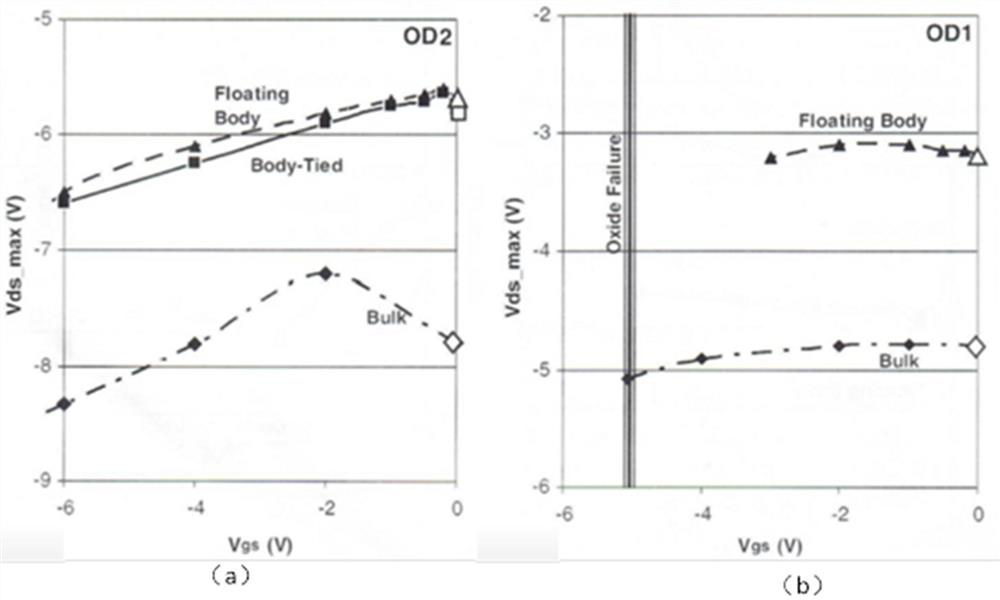

[0021] The ESD protection method for the ESD protection transistor and the CMOS device proposed by the present invention will be further described in detail below with reference to the drawings and specific embodiments. Advantages and features of the present invention will be apparent from the following description and claims. It should be noted that all the drawings are in a very simplified form and use imprecise scales, and are only used to facilitate and clearly assist the purpose of illustrating the embodiments of the present invention.

[0022] In addition, each embodiment of the content described below has one or more technical features respectively, but this does not mean that the inventor must implement all the technical features in any embodiment at the same time, or can only implement different embodiments separately. Some or all of the technical features. In other words, on the premise that the implementation is possible, those skilled in the art can selectively im...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More