Turbo decoder fault tolerance method based on DWC

A decoder and decoding technology, which is applied in the fault tolerance field of DWC-based turbo decoders, can solve the problem that the overall protection of the decoder cannot be realized, and achieve the effect of reducing resource overhead and excessive protection.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

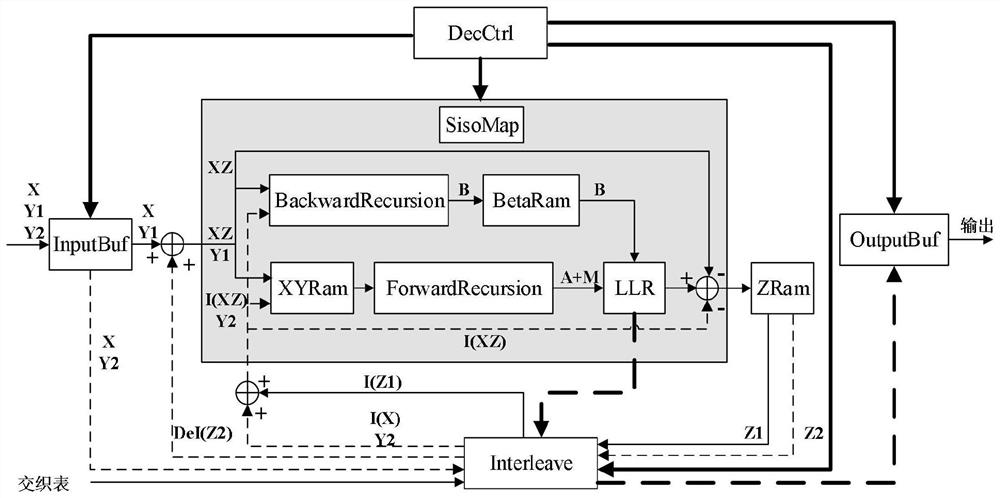

[0028] The Turbo decoder that adopts the Log-MAP decoding algorithm is used for the implementation example of the present invention, and the structure of the decoder is as follows figure 1 shown. The generation matrix of the Turbo code is G=[1 1 0 1; 1 0 1 1], the code rate is 1 / 3, and the information sequence length is 256. In order to ensure that the final state of the encoder returns to zero during the encoder, each component encoder generates 3 additional information bits and 3 check bits, so the length of the encoded sequence is 256*3+(3+3)*2= 780, which is the input sequence length of the decoder. The Turbo decoder iterates 8 times in total, and if one component decoding is counted as one time, it is 16 times.

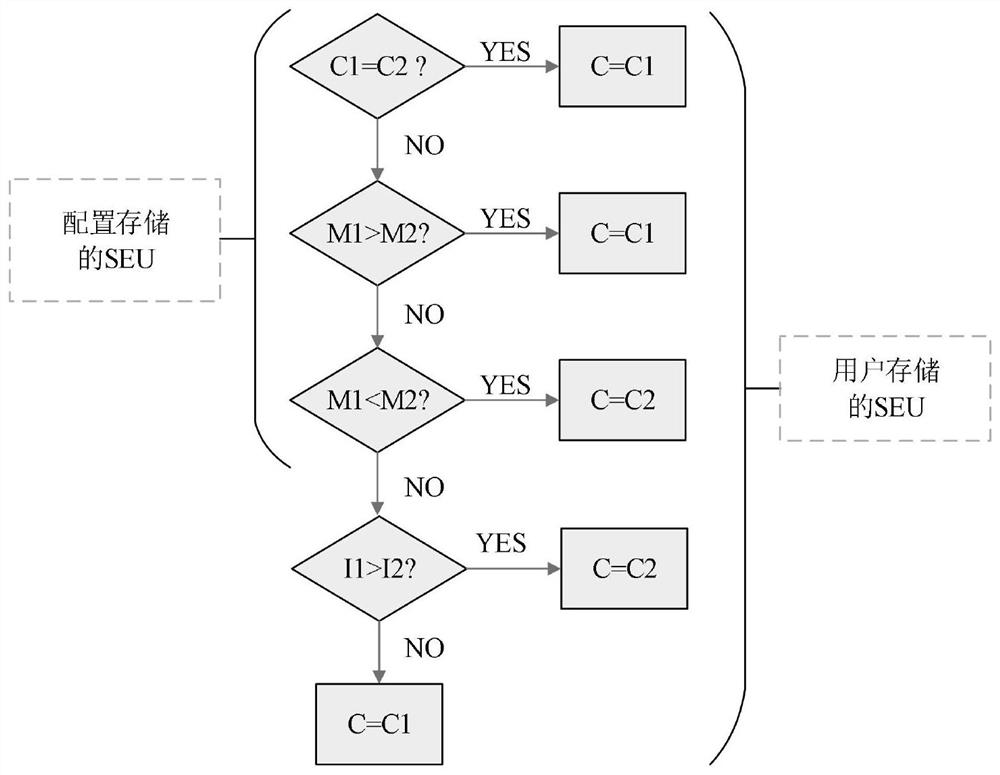

[0029] 1) The proposal of the DWC fault-tolerant scheme in the present invention is based on the analysis of the influence of the SEU on the internal variables of the Turbo decoder. Through the fault injection experiment of FPGA, it is found that the absolute ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More