Cascading method of PCIe signal processing card

A signal processing and processing card technology, applied in the cascade field of PCIe signal processing cards, can solve the problems of limited FPGA resources, limitation of the acceleration capability of a single PCIe card, etc., and achieve the effect of breaking through the bottleneck of limited acceleration capability.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

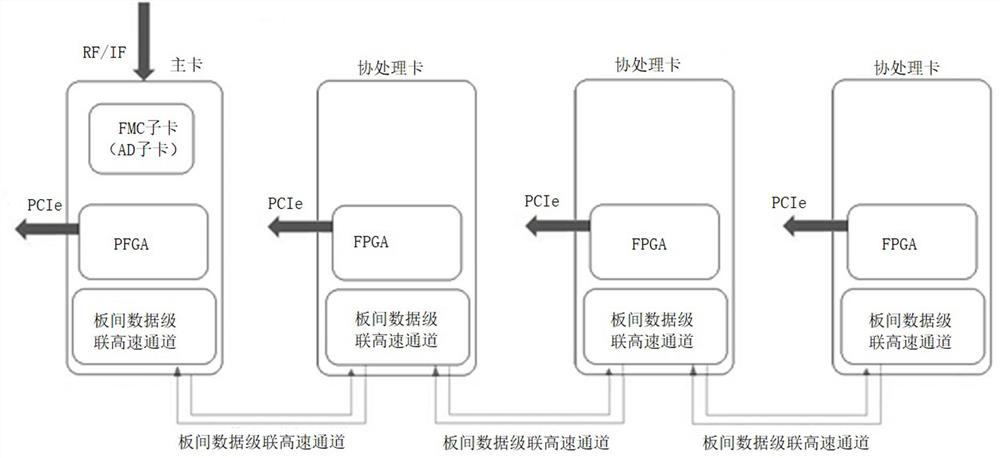

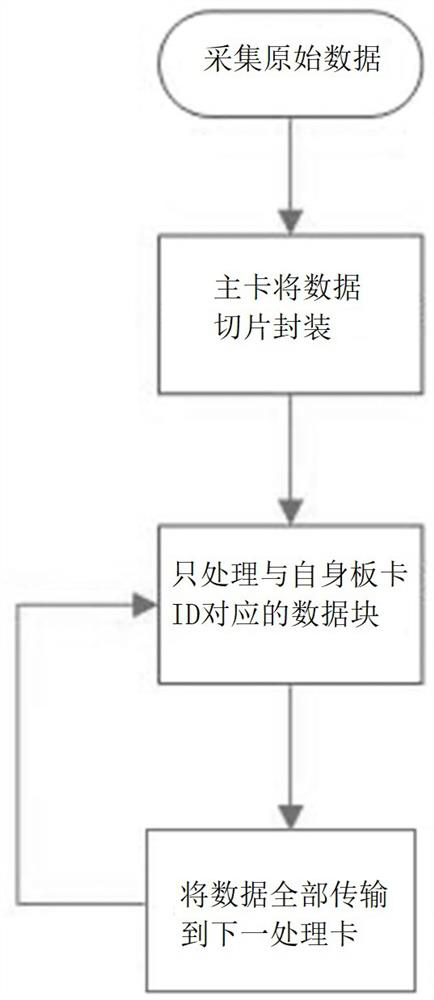

[0038] combined with figure 1 and image 3 As shown, a method for cascading PCIe signal processing cards, including:

[0039] Step S110, cascading multiple identical PCIe signal processing cards through inter-board data high-speed cascading channels, one of the PCIe signal processing cards is connected to the FMC sub-card as the main card, and the remaining PCIe signal processing cards are used as co-processing cards. A PCIe signal processing card communicates with the host computer through the PCIe slot;

[0040] Step S120, the FMC sub-card sends the collected raw data to the main card, and the main card slices and encapsulates the original data to obtain packaged data, and the package header of the packaged data contains information such as the card ID and serial number of the corresponding PCIe signal processing card , the data format of the encapsulation header is shown in the following table:

[0041]

[0042] Step S130, the main card transmits all the data to the c...

Embodiment 2

[0045] A method for cascading PCIe signal processing cards, comprising:

[0046] In step S210, multiple identical PCIe signal processing cards are cascaded through inter-board data high-speed cascading channels, one of the PCIe signal processing cards is connected to the FMC sub-card as the main card, and the remaining PCIe signal processing cards are used as co-processing cards. A PCIe signal processing card communicates with the host computer through the PCIe slot;

[0047] Step S220, the FMC sub-card sends the collected raw data to the main card, and the main card slices and encapsulates the original data to obtain packaged data, and the package header of the packaged data contains the board ID and data block serial number of the corresponding PCIe signal processing card and other information;

[0048] Step S230: The main card takes out the data corresponding to its own card ID from the packaged data, and then sends the remaining data to the next-level co-processing card t...

Embodiment 3

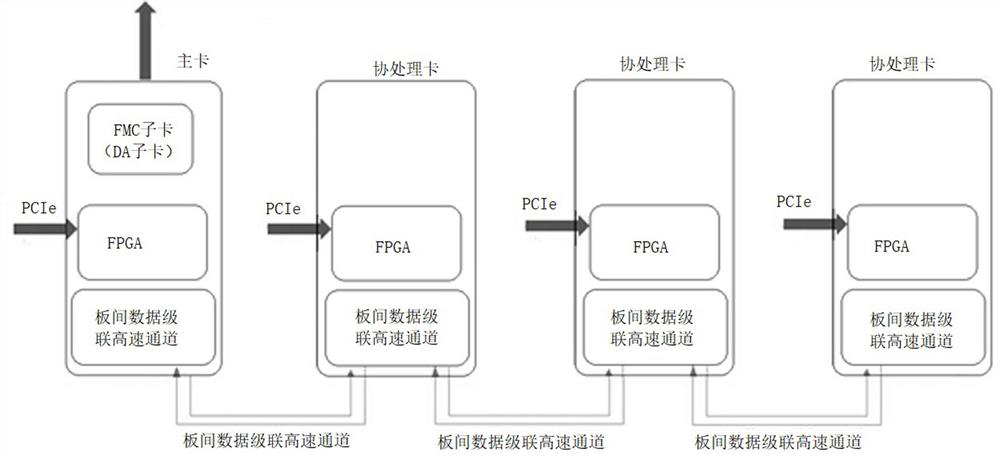

[0053] combined with figure 2 As shown, a method for cascading PCIe signal processing cards, including:

[0054] In step S310, multiple identical PCIe signal processing cards are cascaded through the inter-board data high-speed cascading channel, one of the PCIe signal processing cards is connected to the FMC sub-card as the main card, and the remaining PCIe signal processing cards are used as co-processing cards. A PCIe signal processing card communicates with the host computer through the PCIe slot;

[0055] Step S320: the host computer slices and encapsulates the modulated data to obtain the encapsulated data, and the encapsulation header of the encapsulated data contains information such as the card ID and the data block serial number of the corresponding PCIe signal processing card;

[0056] Step S330: The host computer sends all packaged data to each PCIe signal processing card through the PCIe slot, and the FPGA on each PCIe signal processing card processes the data a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More