Integrated circuit device

A technology of integrated circuits and circuit patterns, which is applied in the direction of circuits, electrical components, and electrical solid devices, and can solve problems such as difficulties in the planarization process of the upper surface of the insulating interlayer

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0017] Hereinafter, a direction substantially perpendicular to the upper surface of the substrate is defined as a vertical direction, and two directions crossing each other in a horizontal direction substantially parallel to the upper surface of the substrate are defined as a first direction and a second direction, respectively. In example embodiments, the first direction and the second direction may be perpendicular to each other.

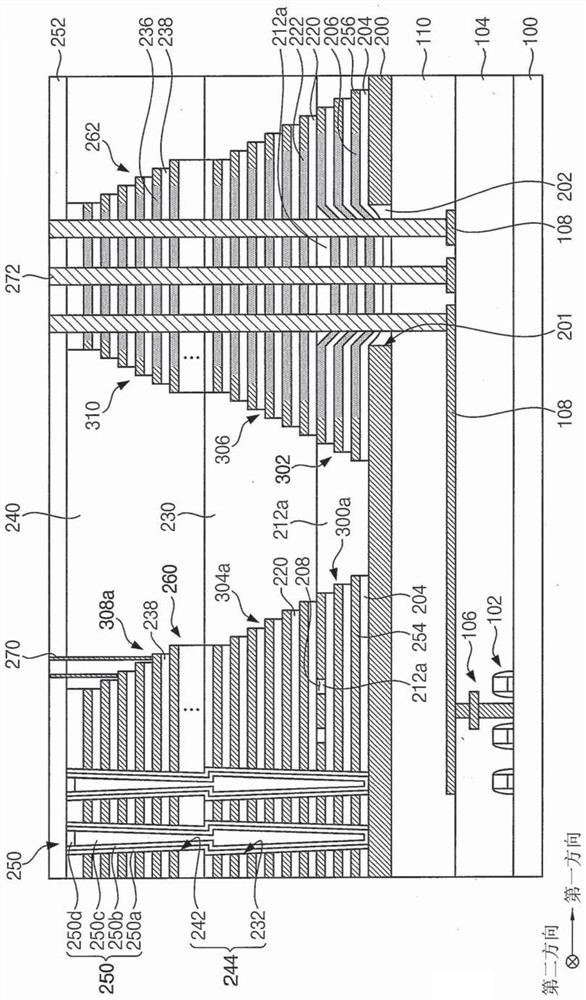

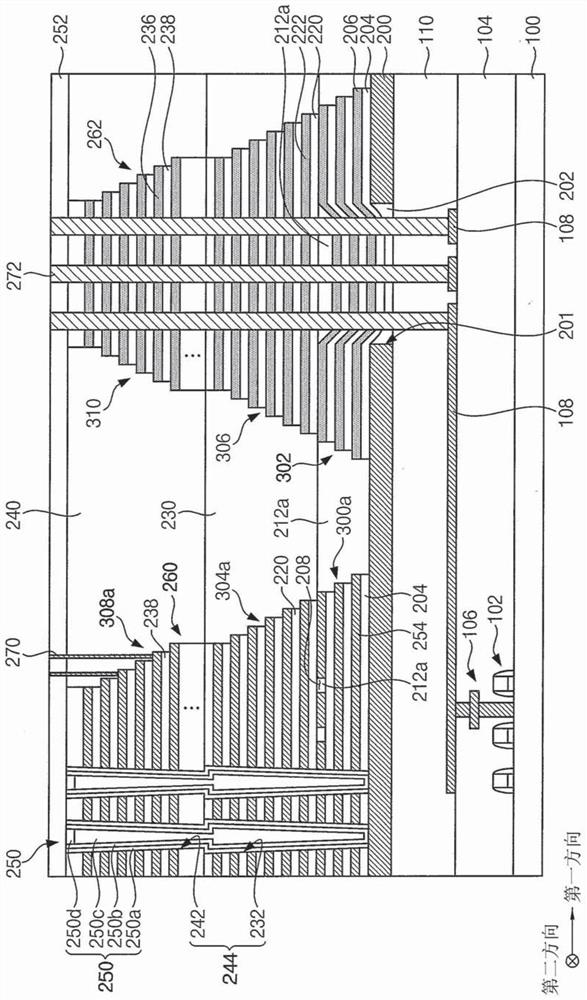

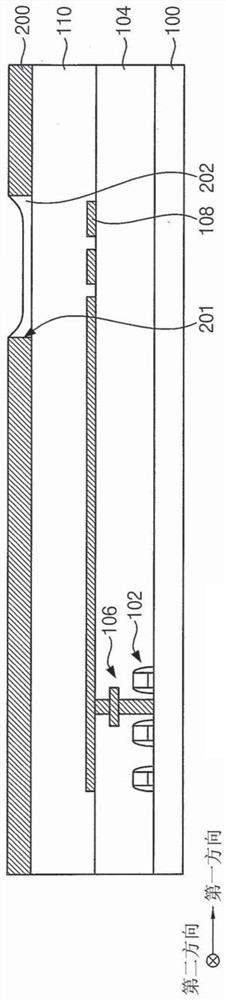

[0018] figure 1 is a cross-sectional view illustrating a vertical semiconductor device according to example embodiments. figure 2 is a cross-sectional view illustrating a vertical semiconductor device according to some example embodiments. refer to figure 1 , the vertical semiconductor device may include circuit patterns constituting peripheral circuits on the substrate 100 . In example embodiments, the circuit pattern may include a lower transistor 102 and a lower wiring 106 . The lower wiring 106 may include lower contact plugs and lower ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More