3d NAND memory and its formation method

A 3DNAND, memory technology, applied in the direction of semiconductor devices, electric solid state devices, electrical components, etc., can solve the problems of stack dislocation, wafer warping and sliding, high production cost, prevent dent defects, small thermal stress, high temperature deformation Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0048] As mentioned in the background art, conventionally, when forming a polysilicon layer and a metal layer on the polysilicon layer to form an array common source, residues of the metal layer are likely to occur.

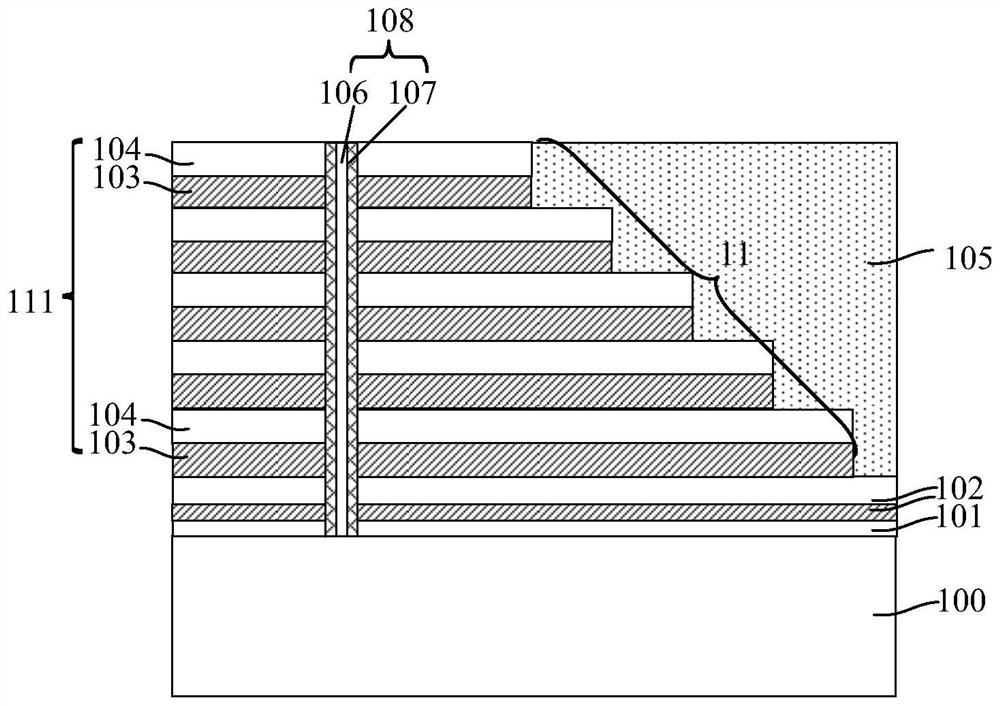

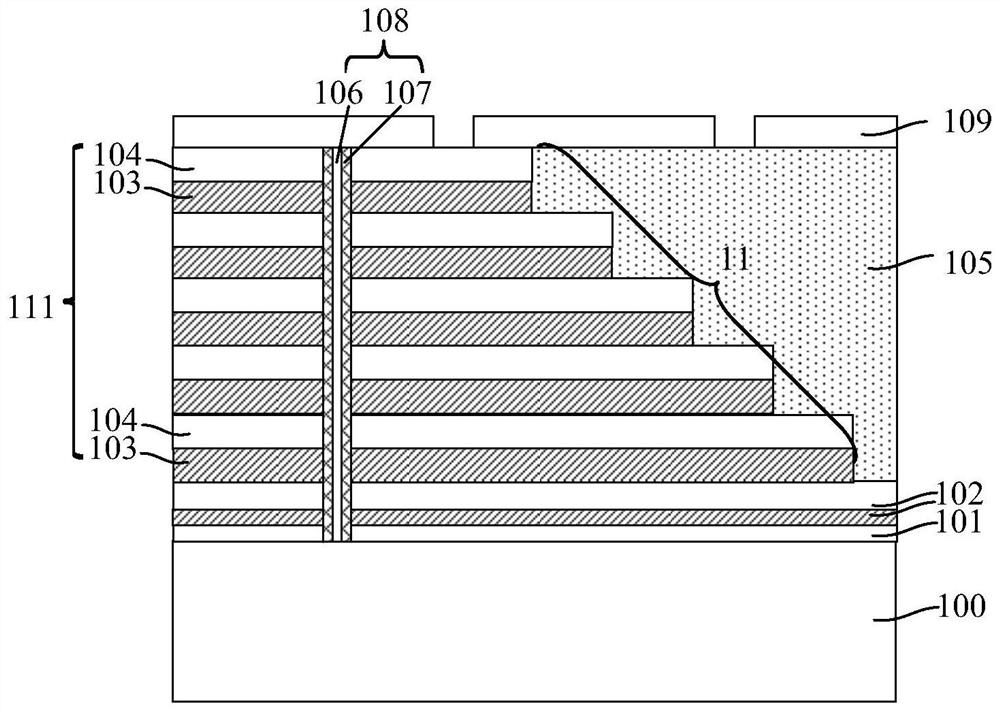

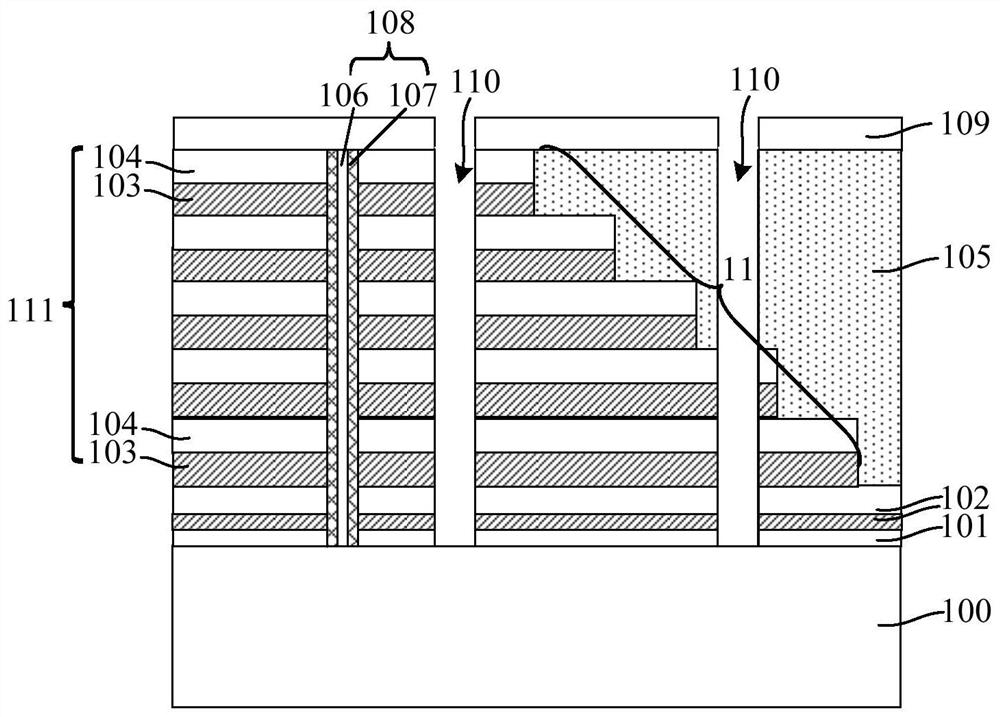

[0049] Research has found that the formation process of 3D NAND memory is as follows: firstly, a stack structure with alternately stacked sacrificial layers and isolation layers is formed on the semiconductor substrate, and the end of the stack structure has a stepped structure; a dielectric layer covering the stepped structure is formed; A plurality of gate spacers are formed in the stacked structure on one side of the stepped structure; a polysilicon material layer is formed on the stacked structure and the dielectric layer and in the gate spacers; a chemical mechanical polishing process removes the polysilicon on the stacked structure and the dielectric layer material layer, and then etch back to remove part of the thickness of the polysilicon material layer, f...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More