Display panel and pixel circuit thereof

A pixel circuit and display panel technology, applied to static indicators, instruments, etc., can solve the problems of signal voltage conversion and loading, affecting optical effects, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

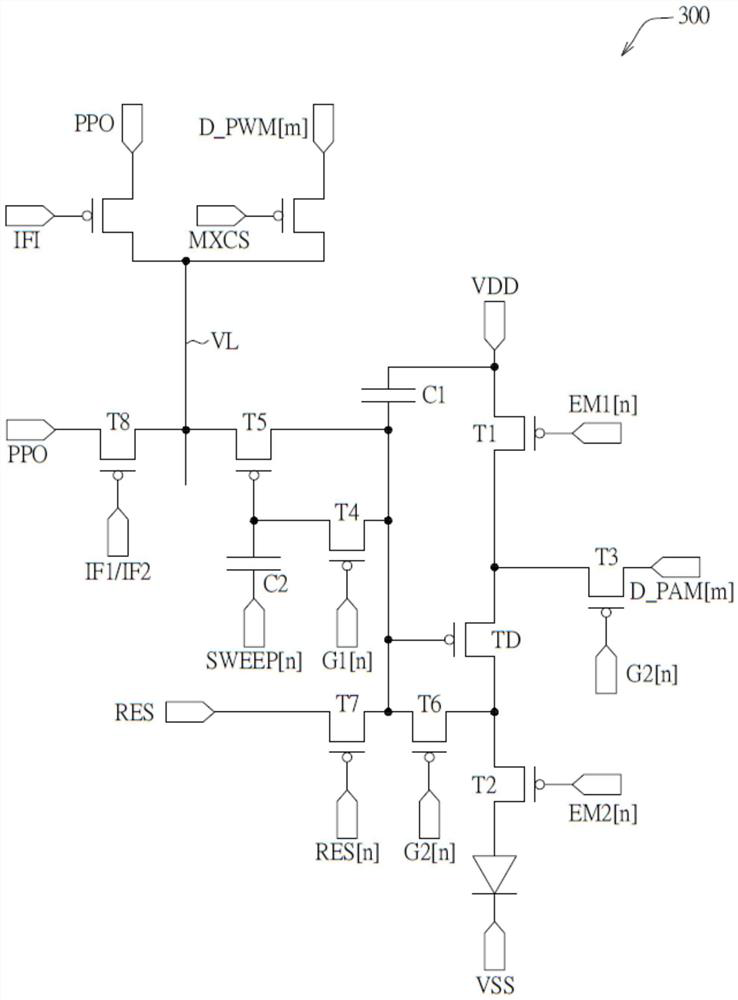

[0028] Below in conjunction with accompanying drawing, structural principle and working principle of the present invention are specifically described:

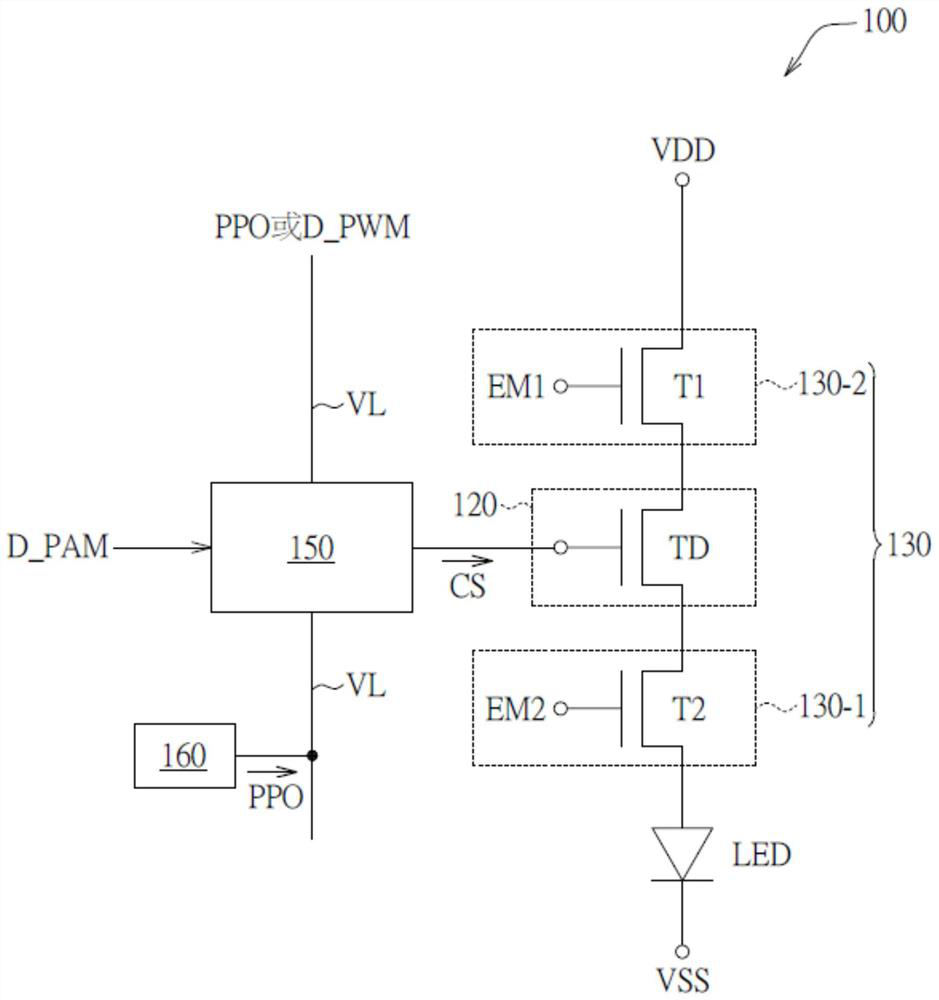

[0029] Please refer to figure 1 , figure 1 It is a block diagram of a pixel circuit according to an embodiment of the present invention. The pixel circuit 100 includes a driving unit 120 , a light emitting controller 130 , a light emitting element LED, a first driving block 150 and a second driving block 160 .

[0030] The driving unit 120 includes a driving transistor TD. The driving transistor TD has a control terminal for receiving a control signal CS, wherein the control signal CS may include a pulse width control signal and an amplitude control signal. The driving transistor TD generates a driving signal according to the control signal CS to drive the light emitting element LED to emit light. In this embodiment, the light emitting element LED may be any form of light emitting diode.

[0031] The circuits 130-1, 130-2...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More