Mixed bit width accelerator based on DSP and fusion calculation method

A technology of accelerators and adders, applied in computing, instruments, biological neural network models, etc., can solve problems such as no higher parallelism implementation plan, poor versatility, and limitations, and achieve wide application and versatility Good, the effect of maximizing computing performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0047] In order to further understand the present invention, the present invention will be described below in conjunction with the examples. These descriptions are only to further explain the features and advantages of the present invention, and are not intended to limit the claims of the present invention.

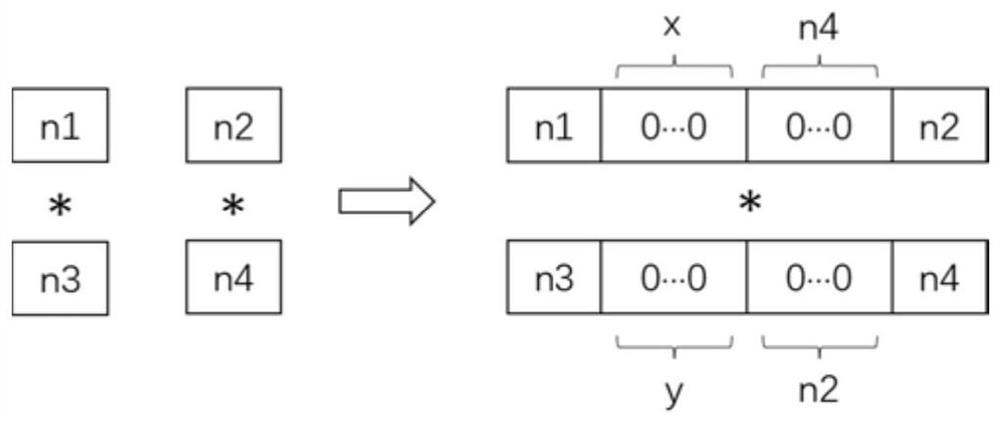

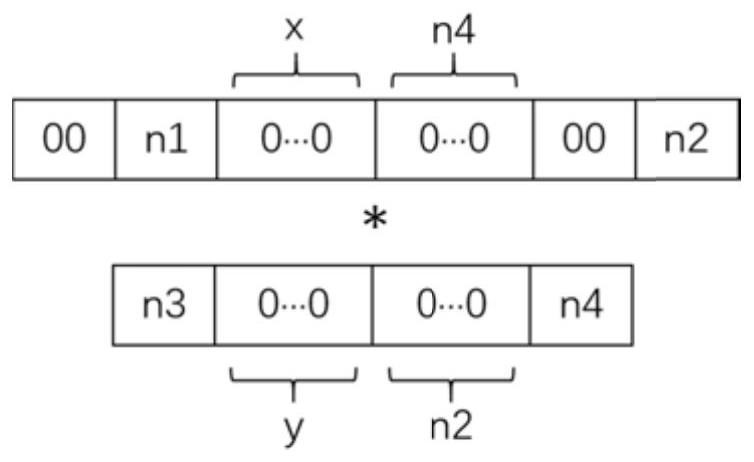

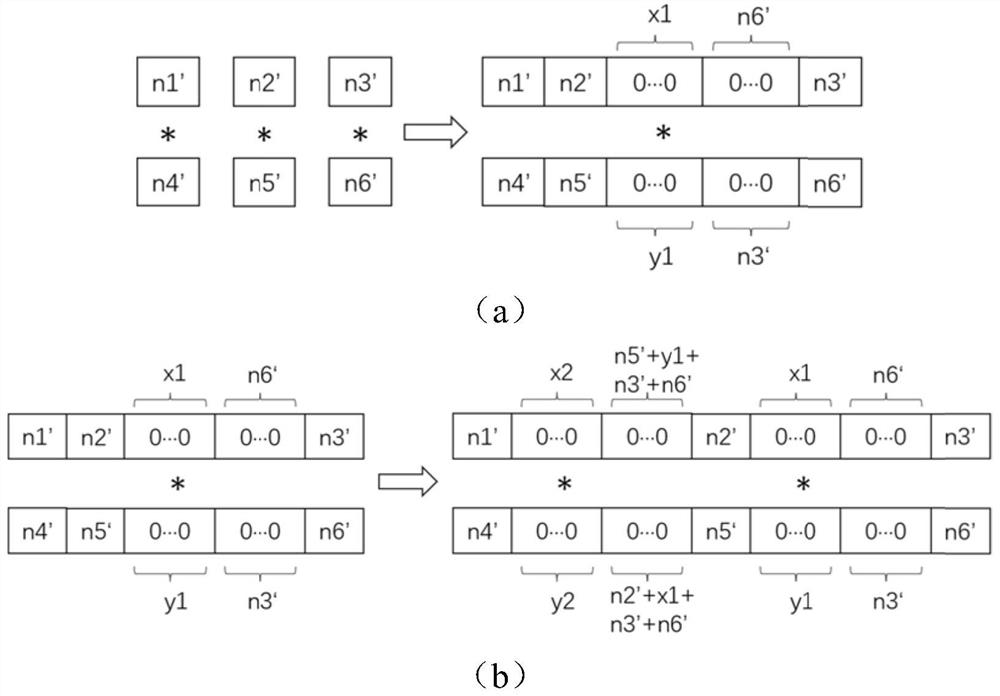

[0048] Firstly, the high-bit-width DSP realizes two low-bit-width multiplication and accumulation schemes at the same time, such as figure 1 shown. For two sets of low-bit-width multiplications to be performed, the bit-widths of the multiplicand and the multiplier are n1 and n3, n2 and n4, respectively. The two multiplicands and the multiplier form the multiplication of two high-bit-width numbers by shifting and splicing, and the shift numbers during splicing are x+n4 and y+n2 respectively. Among them, x, y, n1, n2, n3, and n4 need to satisfy the following constraints:

[0049] x+y+2(n2+n4)≥max(n1+x+n4+n2+n4,n3+y+n2+n4+n2)+1 (1)

[0050] Under this constraint, by calcu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More