Equal-delay distributed cache Ethernet MAC architecture

A distributed cache, Ethernet technology, applied in the field of communication, can solve the problem that the packet scheduling delay is difficult to keep consistent, and achieve the effect of achieving certainty and consistency, low jitter, and saving cache resources.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

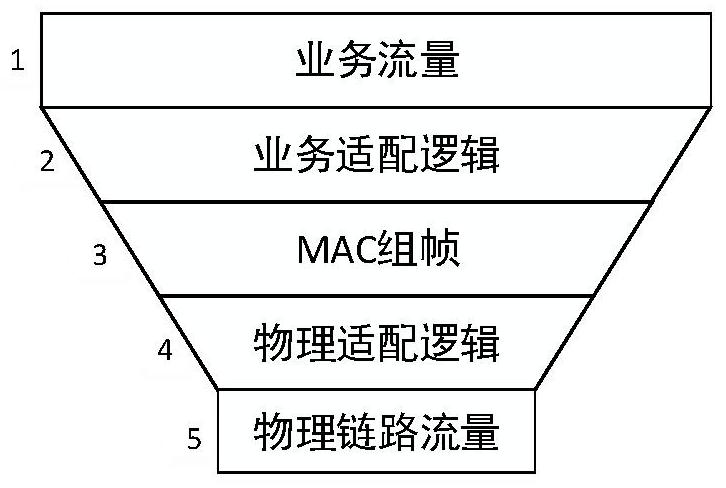

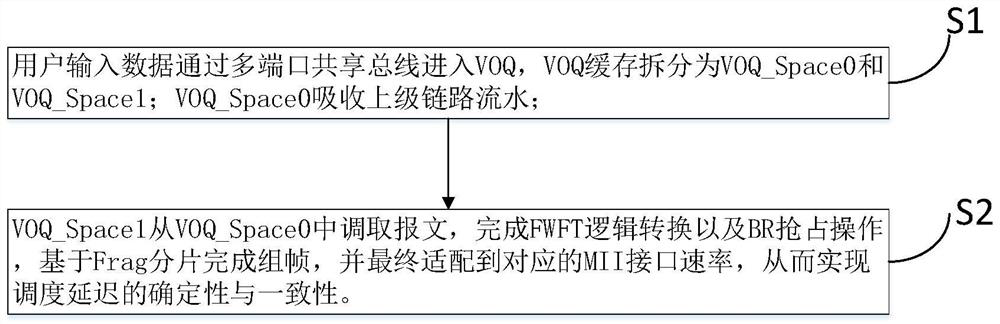

[0055] A schematic diagram of an equal-delay distributed cache Ethernet MAC architecture is shown in Image 6 shown. The specific implementation steps are as follows:

[0056] Step 1: If Image 6 As shown, user input data enters VOQ (Virtual OutputQueue, virtual output queue) through the multi-port shared bus;

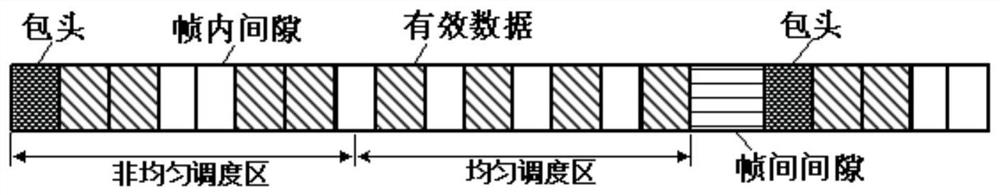

[0057] The VOQ cache here only needs to absorb the flow of the upper link (marked as VOQ_Space0), and does not need to centrally set the cache part (marked as VOQ_Space1) that is exclusive to the sub-queue in the conventional VOQ to ensure continuous data flow. The VOQ outlet demultiplexes data based on the port. Each port supports two priority queues, e and p. The e queue has a high priority and can interrupt the transmission of the p queue to ensure that this queue is sent first. The final realization of the Layer 2 service adaptation logic scheduling effect is as follows: Figure 4 As shown, it is characterized by uniform intra-packet scheduling and controllable...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More