Analog frequency divider

A frequency divider and analog signal technology, applied in the direction of pulse counters, counting chain pulse counters, pulse counters using semiconductor devices, etc., can solve the problem of inability to complete normal frequency division functions, frequency division function errors, and digital frequency divider frequency upper limit And other issues

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

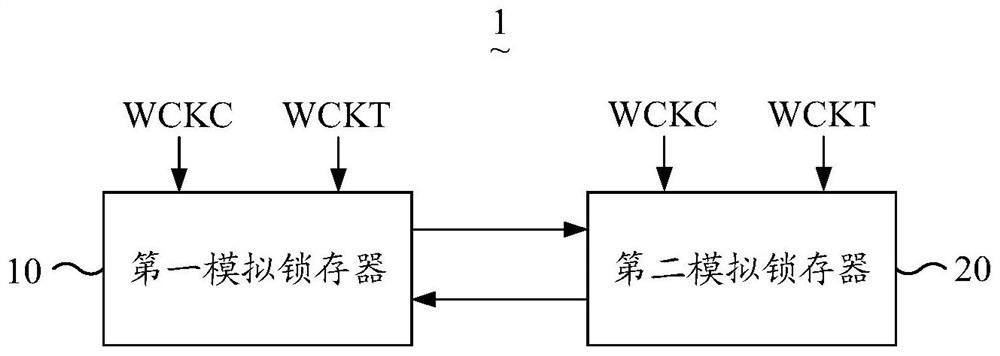

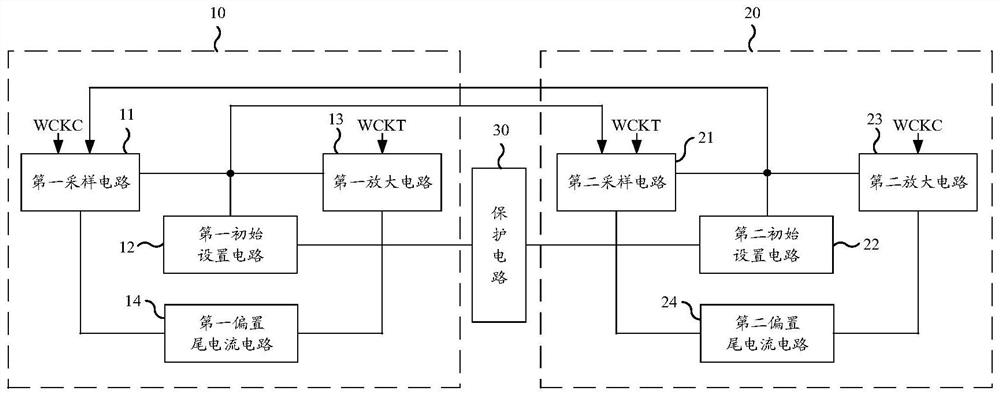

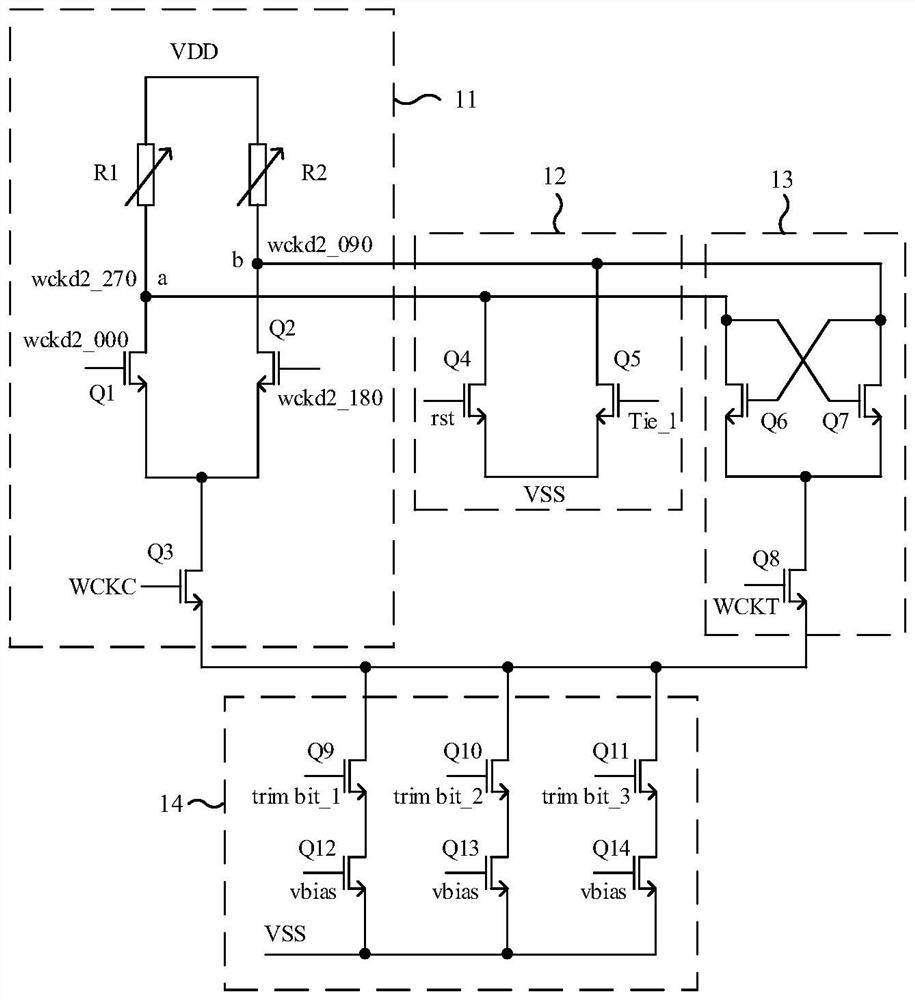

[0014] In order to make those skilled in the art better understand the technical solutions of the present application, the analog frequency divider provided by the present application will be described in further detail below with reference to the accompanying drawings and specific embodiments. It should be understood that the described embodiments are only a part of the embodiments of the present application, but not all of the embodiments. Based on the embodiments in the present application, all other embodiments obtained by those of ordinary skill in the art without creative efforts shall fall within the protection scope of the present application.

[0015] The terms "first", "second", etc. in this application are used to distinguish different objects, rather than to describe a specific order. Furthermore, the terms "comprising" and "having" and any variations thereof are intended to cover non-exclusive inclusion. For example, a process, method, system, product or device c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More