Patents

Literature

609results about How to "Improve working bandwidth" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Optical grating coupler and optical signal coupling method

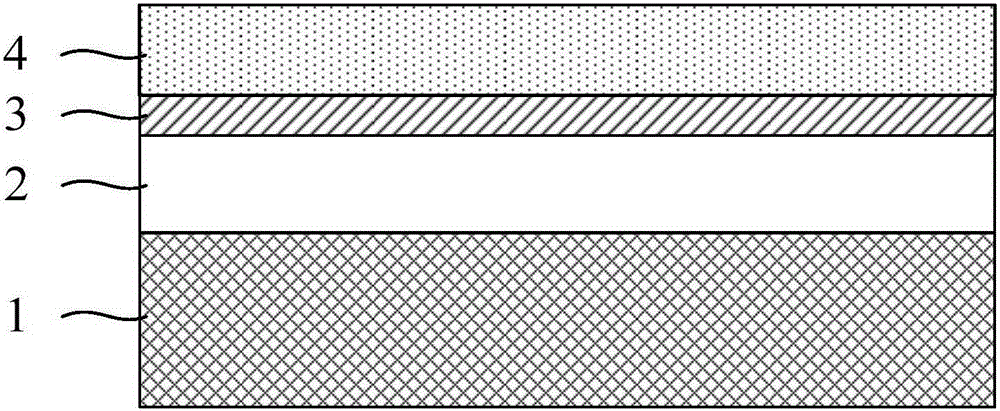

InactiveCN103777282AImprove working bandwidthSimple structureCoupling light guidesTime domainGrating

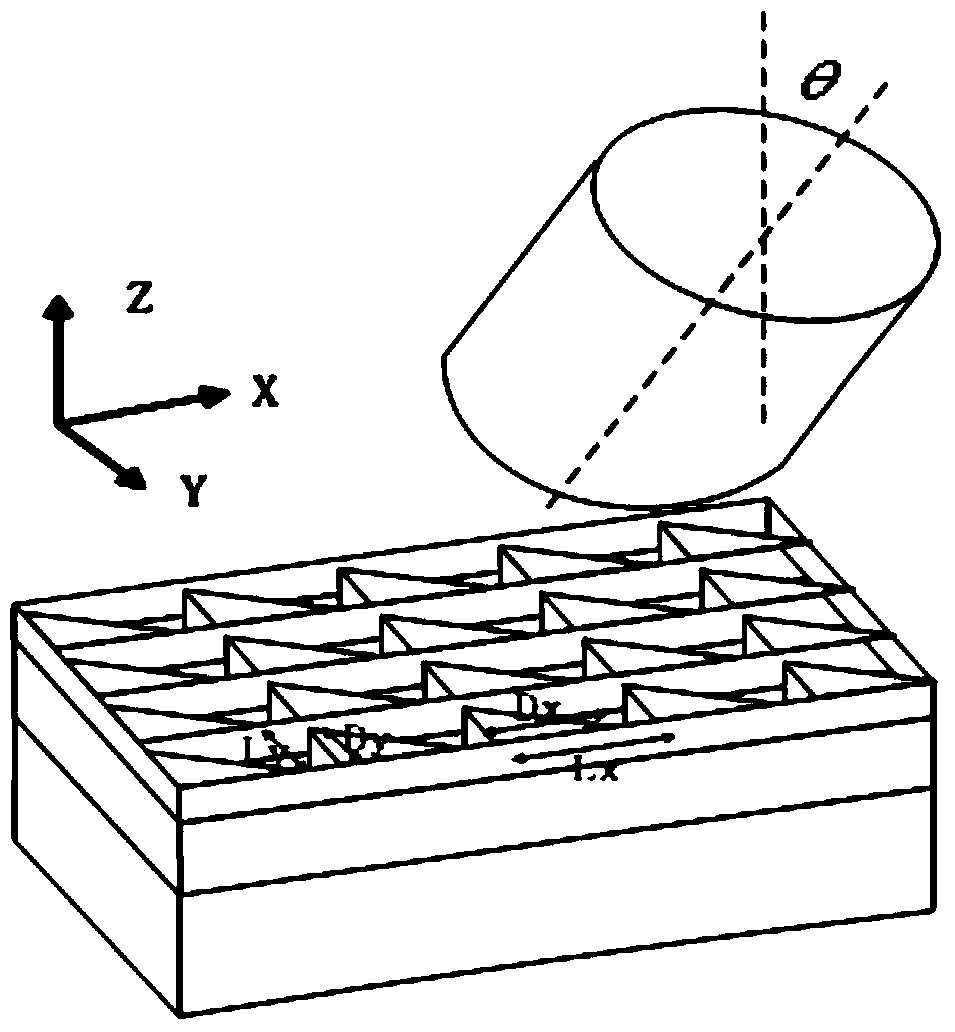

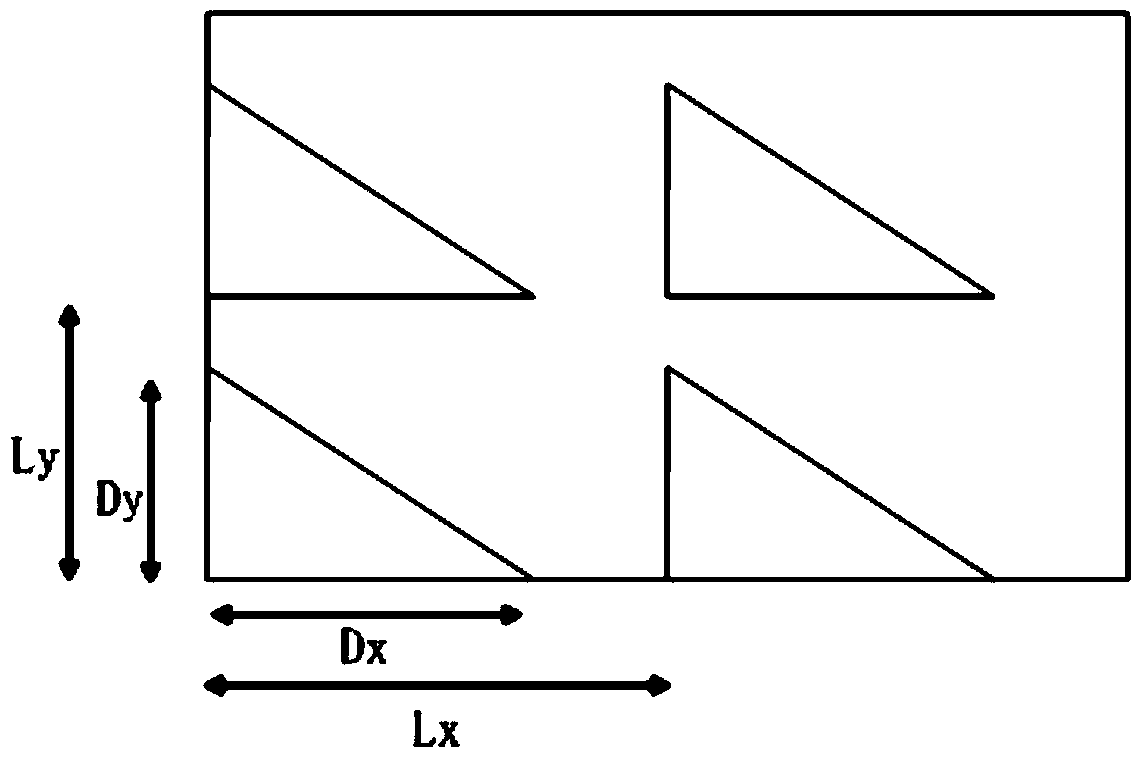

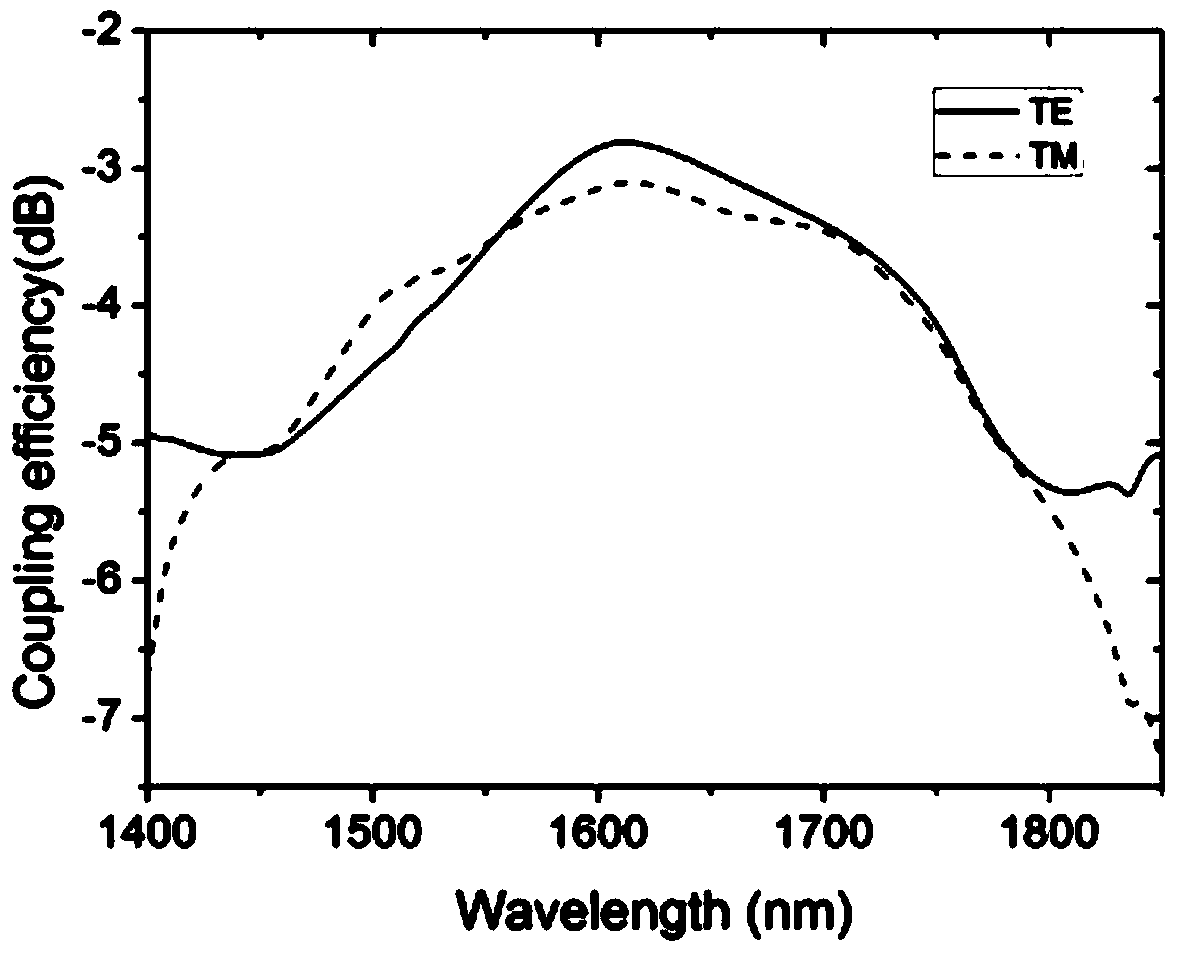

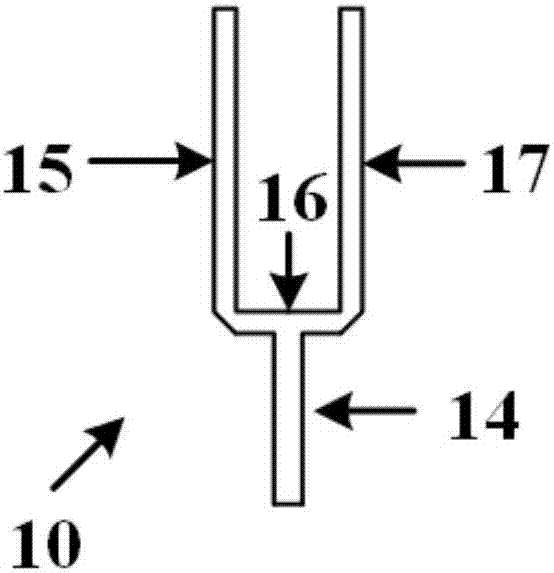

The invention relates to the technical field of optical communication and discloses an optical grating coupler and an optical signal coupling method. The optical grating coupler comprises a top silicon layer, a base silicon layer and a silicon dioxide layer, wherein the silicon dioxide layer is arranged on the upper surface of the base silicon layer, the top silicon layer is disposed on the upper surface of the silicon dioxide layer, the top silicon layer is of a structure formed by ranking at least two right triangles in the direction perpendicular to the light transmission direction, and received optical fibers face toward the rank structure of the right triangles. According to the optical grating coupler and the optical signal coupling method, through application of triangular optical gratings, work bandwidth of the optical grating coupler is increased, and applicability of the optical grating coupler is improved; besides, simulating calculation is performed through a three-dimensional time domain finite difference method so that TE and TM light coupling efficiencies are the same, optical grating structural parameters are determined, polarization insensitivity is achieved; the optical grating coupler has the advantages of being simple in structure, wide in work bandwidth, low in polarization loss and high in coupling efficiency.

Owner:HUAZHONG UNIV OF SCI & TECH

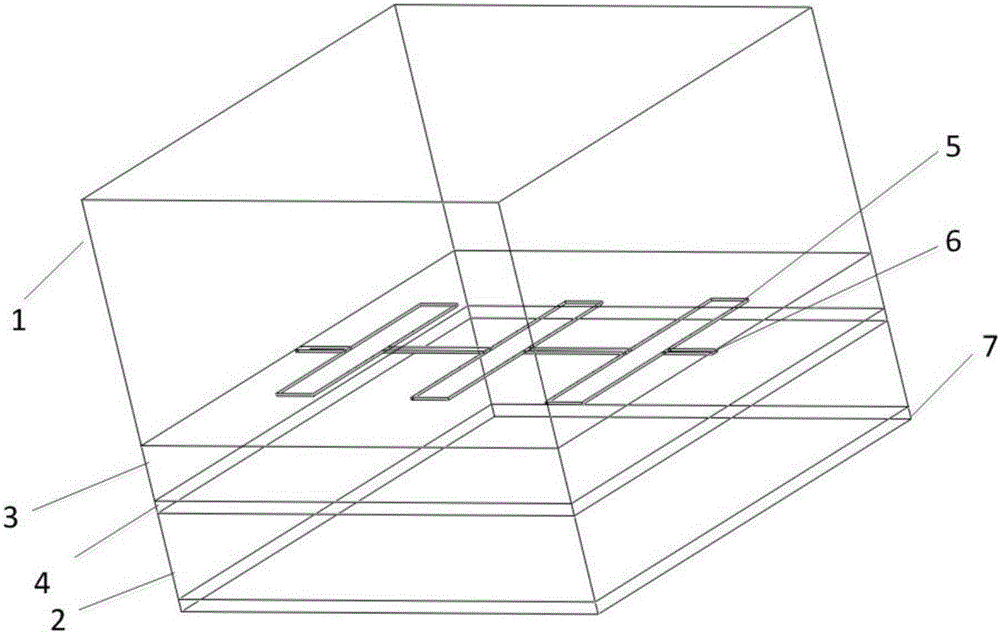

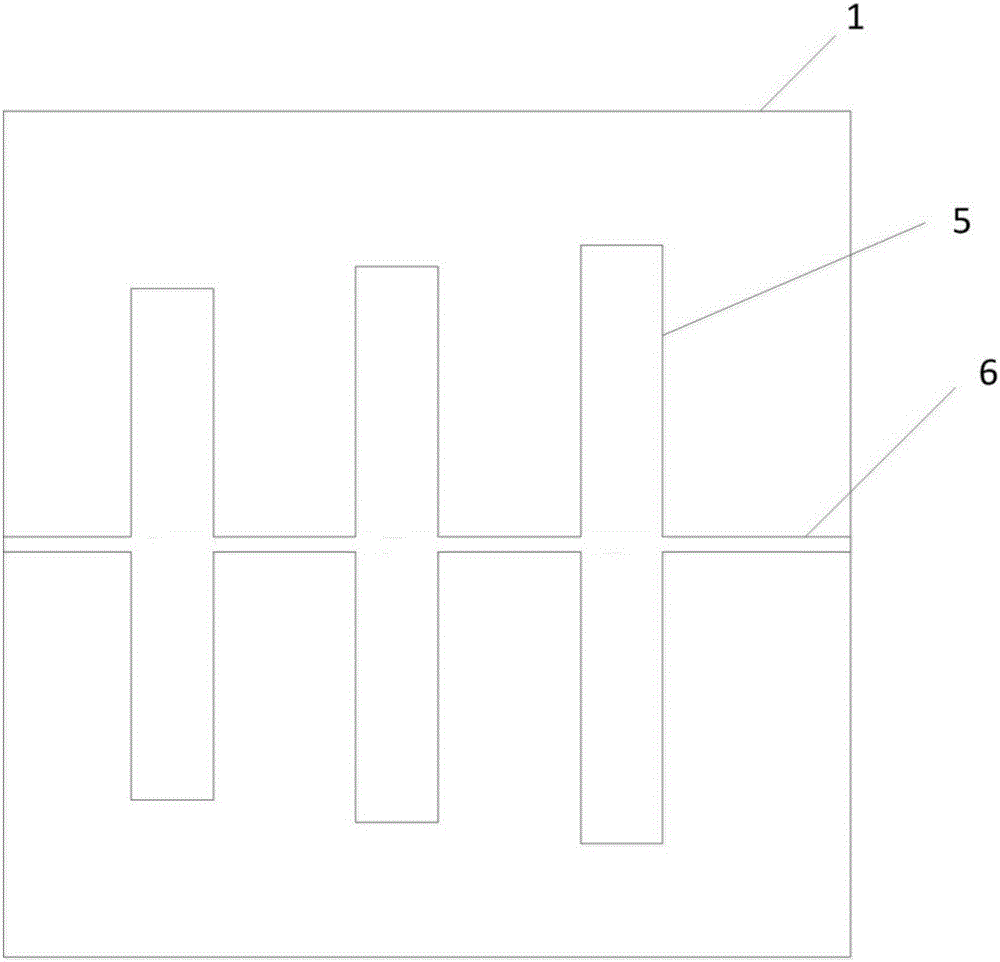

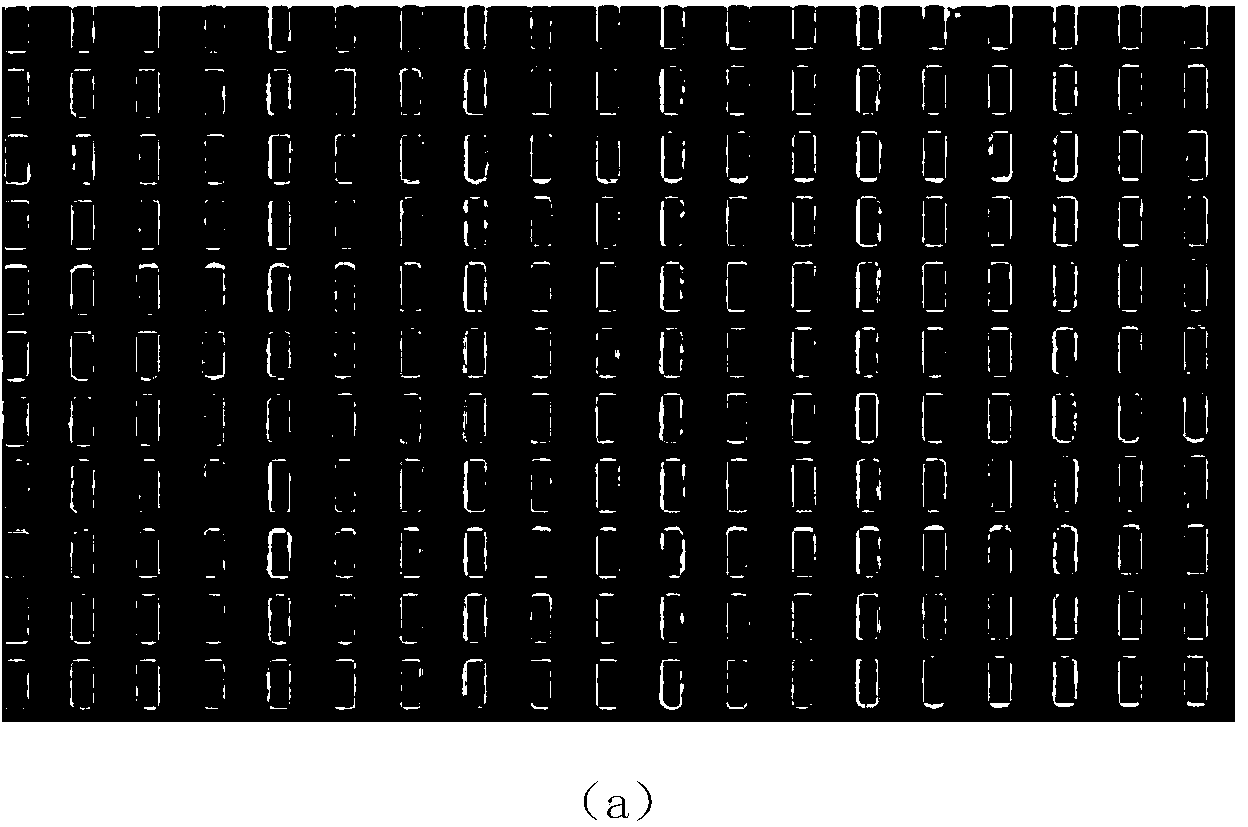

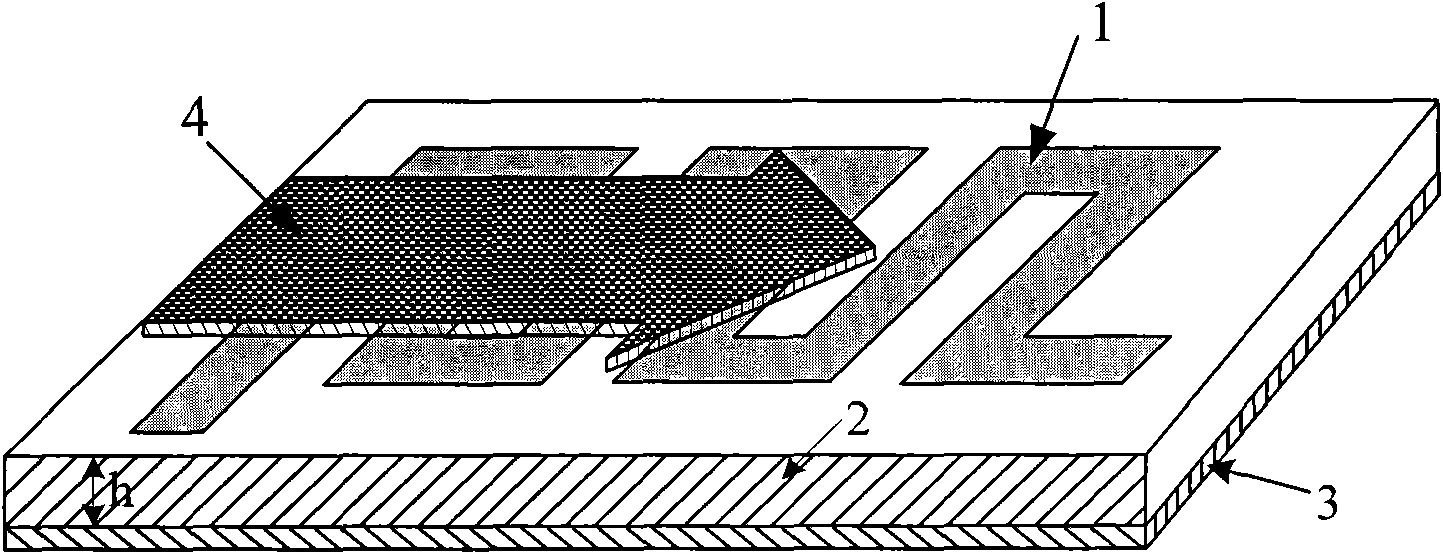

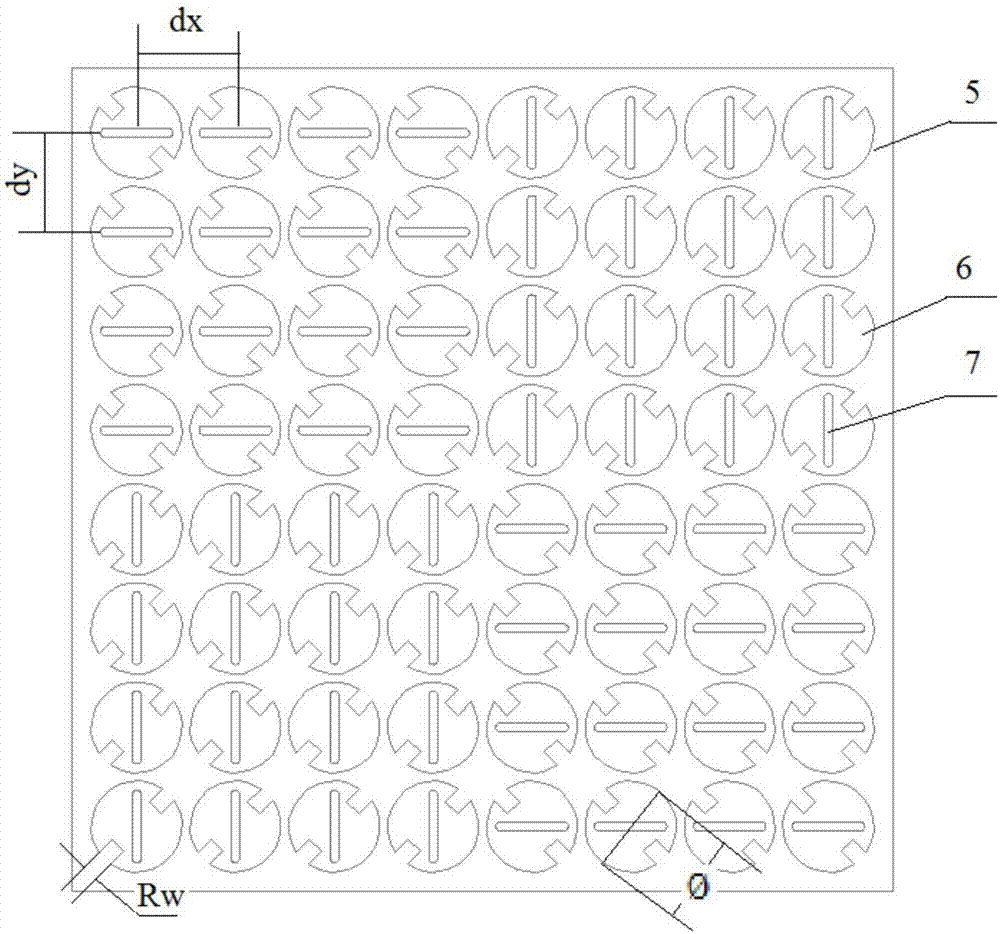

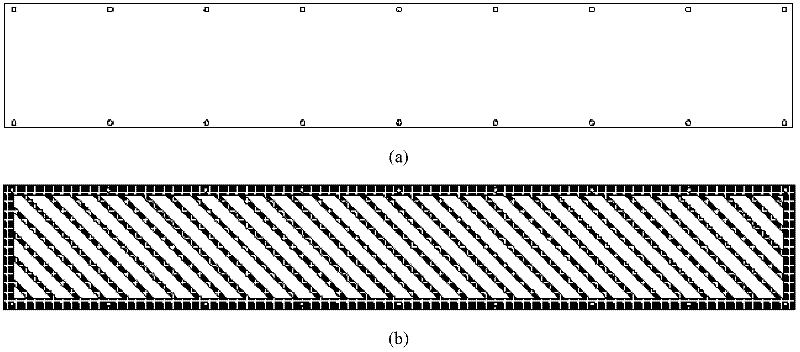

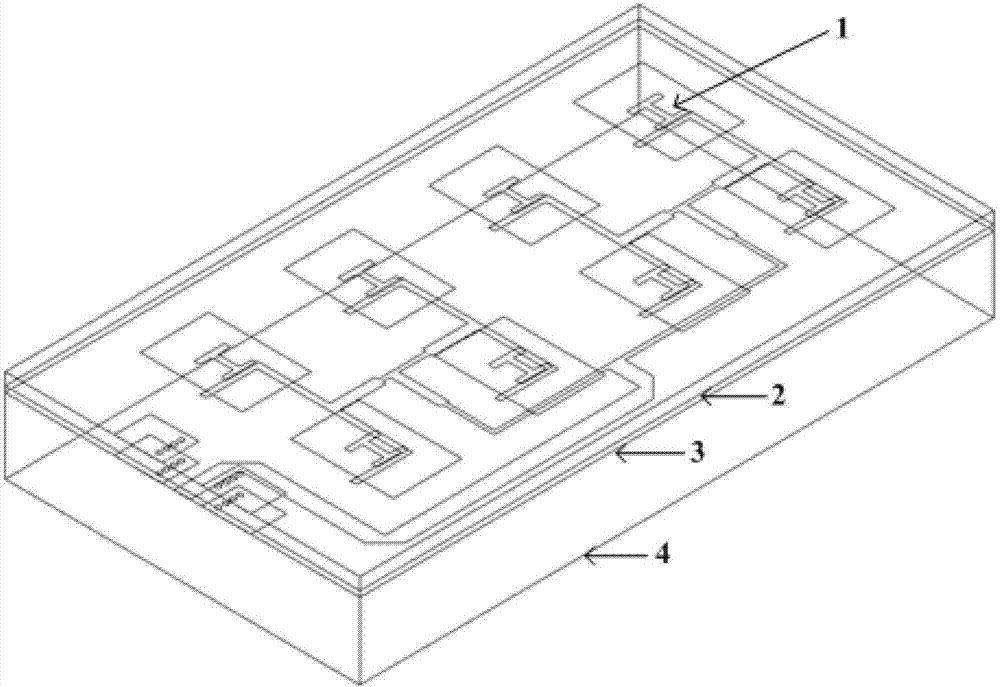

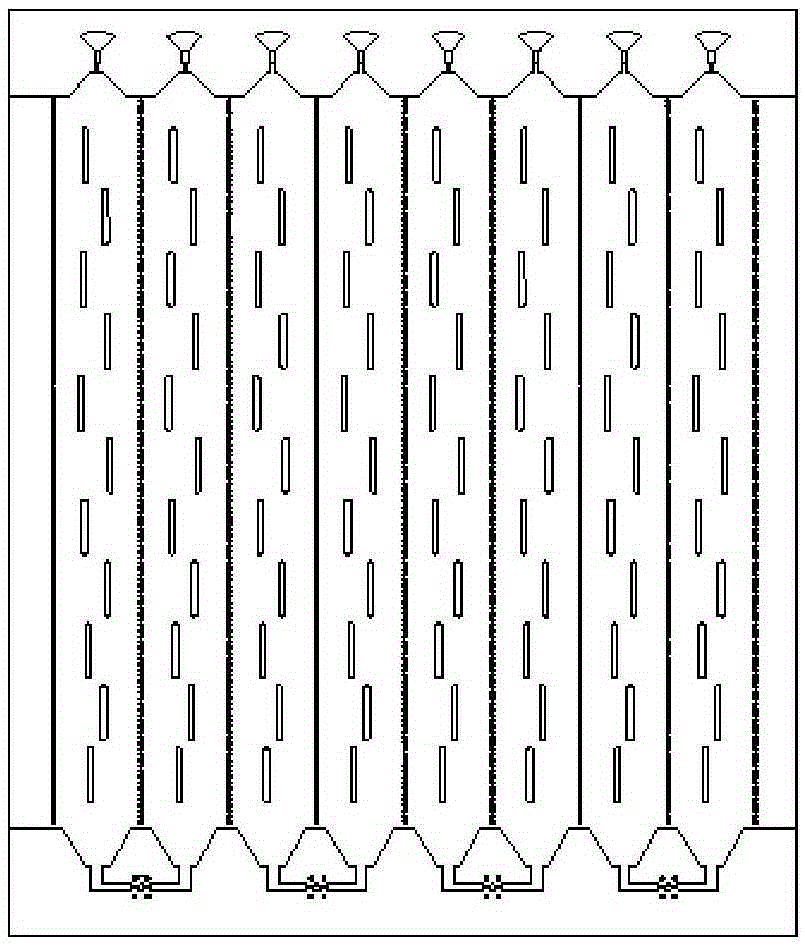

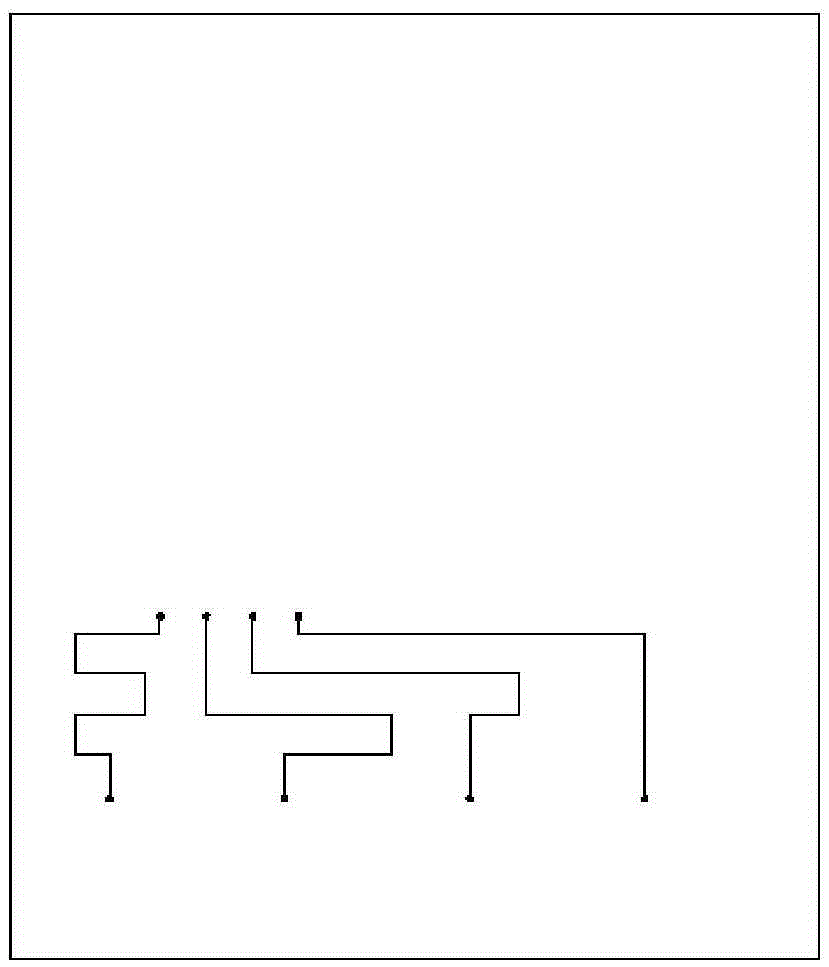

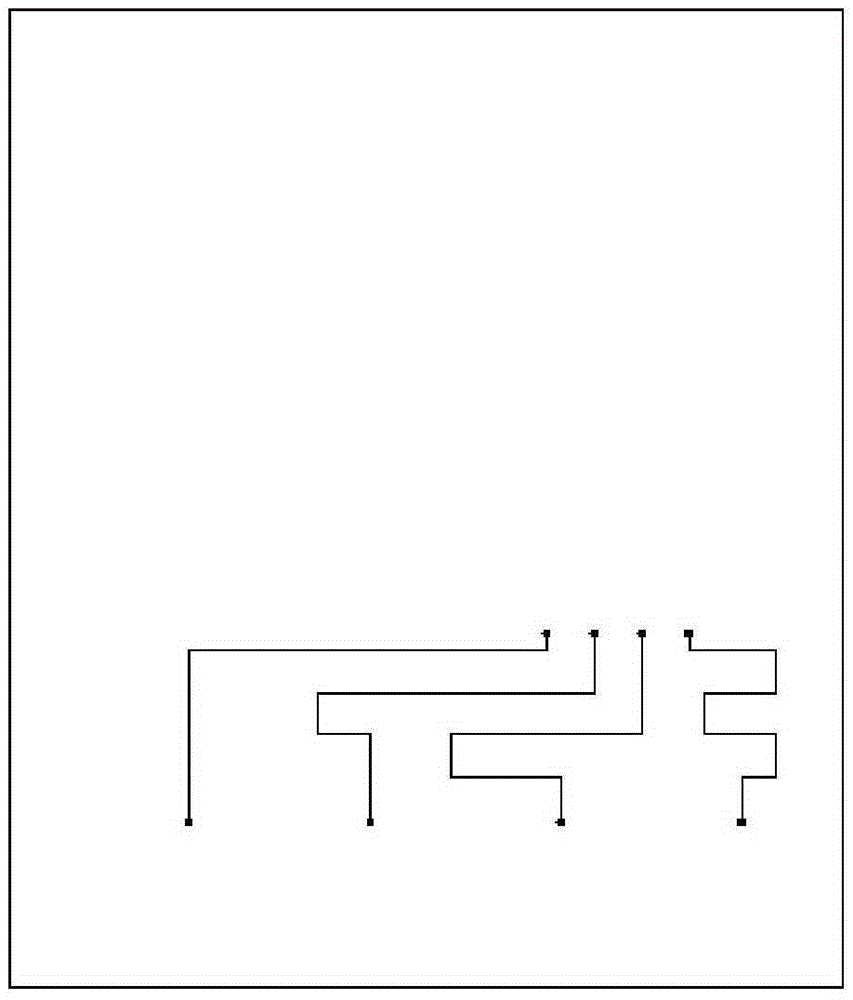

Broadband low-section dual polarization microstrip antenna adopting latticed radiation pastes

InactiveCN107394378AImprove working bandwidthLow profileRadiating elements structural formsIndividually energised antenna arraysCouplingImpedance matching

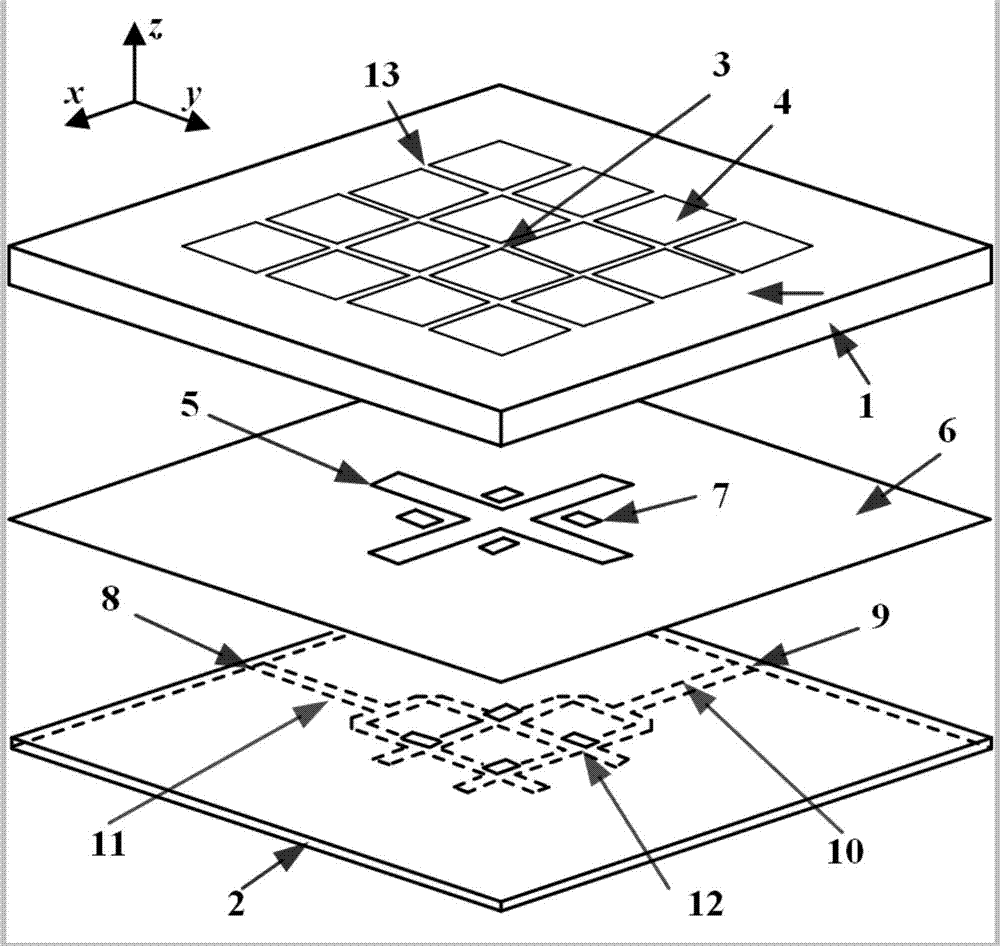

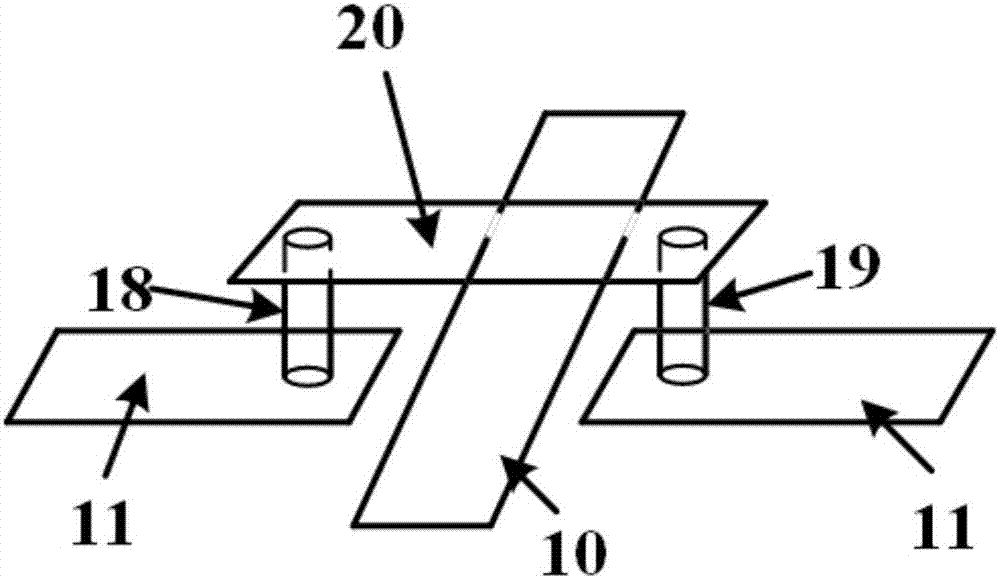

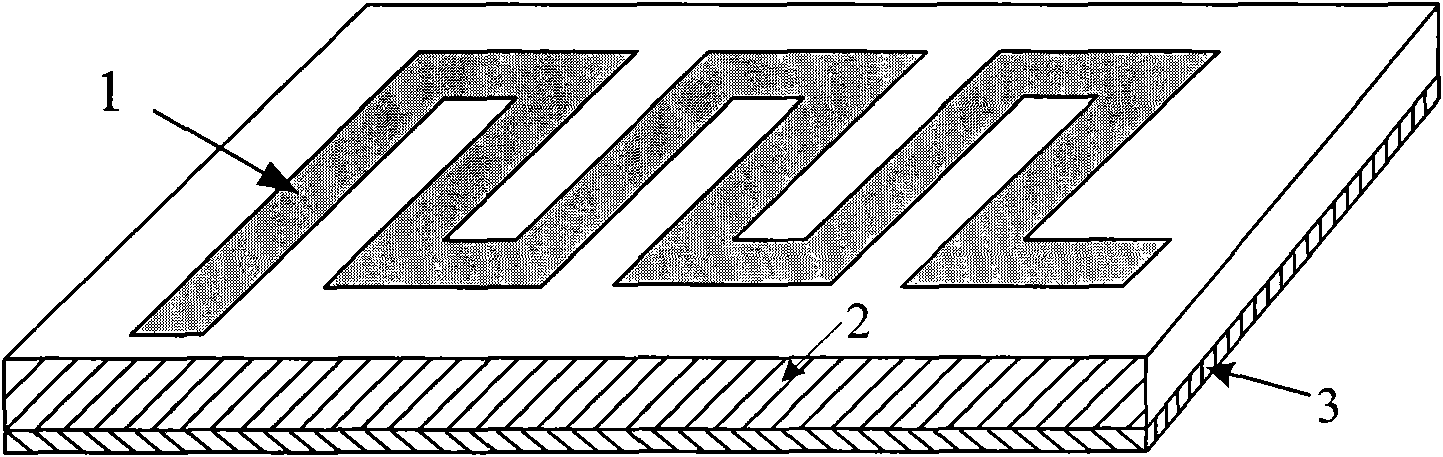

The invention provides a broadband low-section dual polarization microstrip antenna adopting latticed radiation pastes. The broadband low-section dual polarization microstrip antenna comprises two layers of substrates which are placed up and down; 4*4 latticed radiation pastes placed on the front face of the upper layer of substrate, and the lattices have the same sizes and are periodically arranged; cross coupling grooves engraved on the metal floor on the front face of the lower layer of substrate are respectively symmetrical relative to the x axis and the y axis and are used for activating two orthogonal polarization on the radiation pastes; two Y-shaped microstrip feeder lines vertically to each other and placed on the back surface of the lower layer of substrate are used for activating the above cross coupling grooves, and in order to avoid the intersection of the two microstrip feeder lines, four symmetrical crossover structures are introduced. In the broadband low-section dual polarization microstrip antenna, the 4*4 latticed radiation pastes used by the microstrip antenna can activate the TM10 mode and the inverted TM 20 mode, the two modes can be coupled together by adjusting the sizes of the pastes so as to improve the working bandwidth; and in addition, the sizes of the Y-shaped microstrip feeder lines and the cross coupling grooves are adjusted to improve the impedance matching performance of the antenna, and the bandwidth is further improved.

Owner:TSINGHUA UNIV

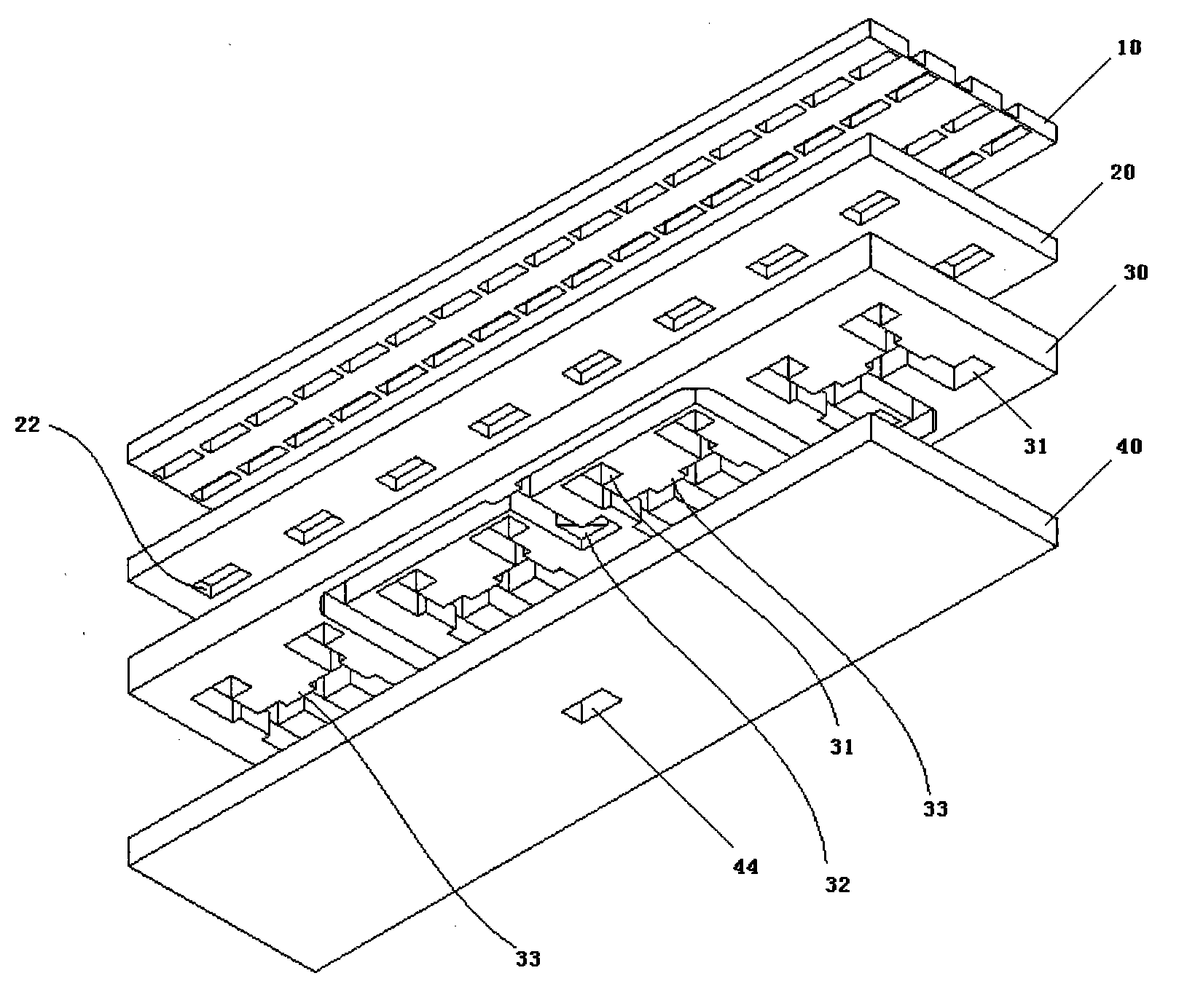

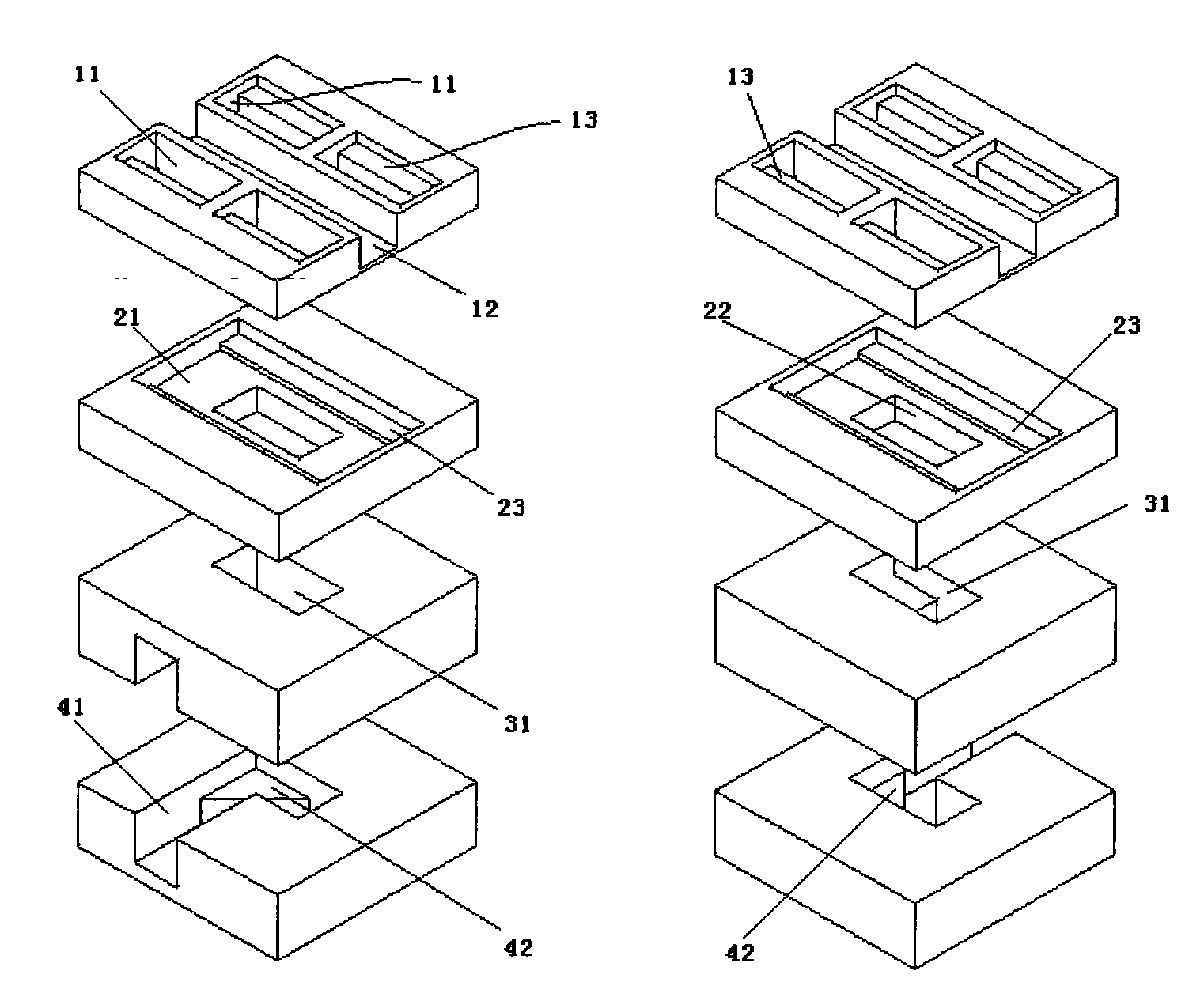

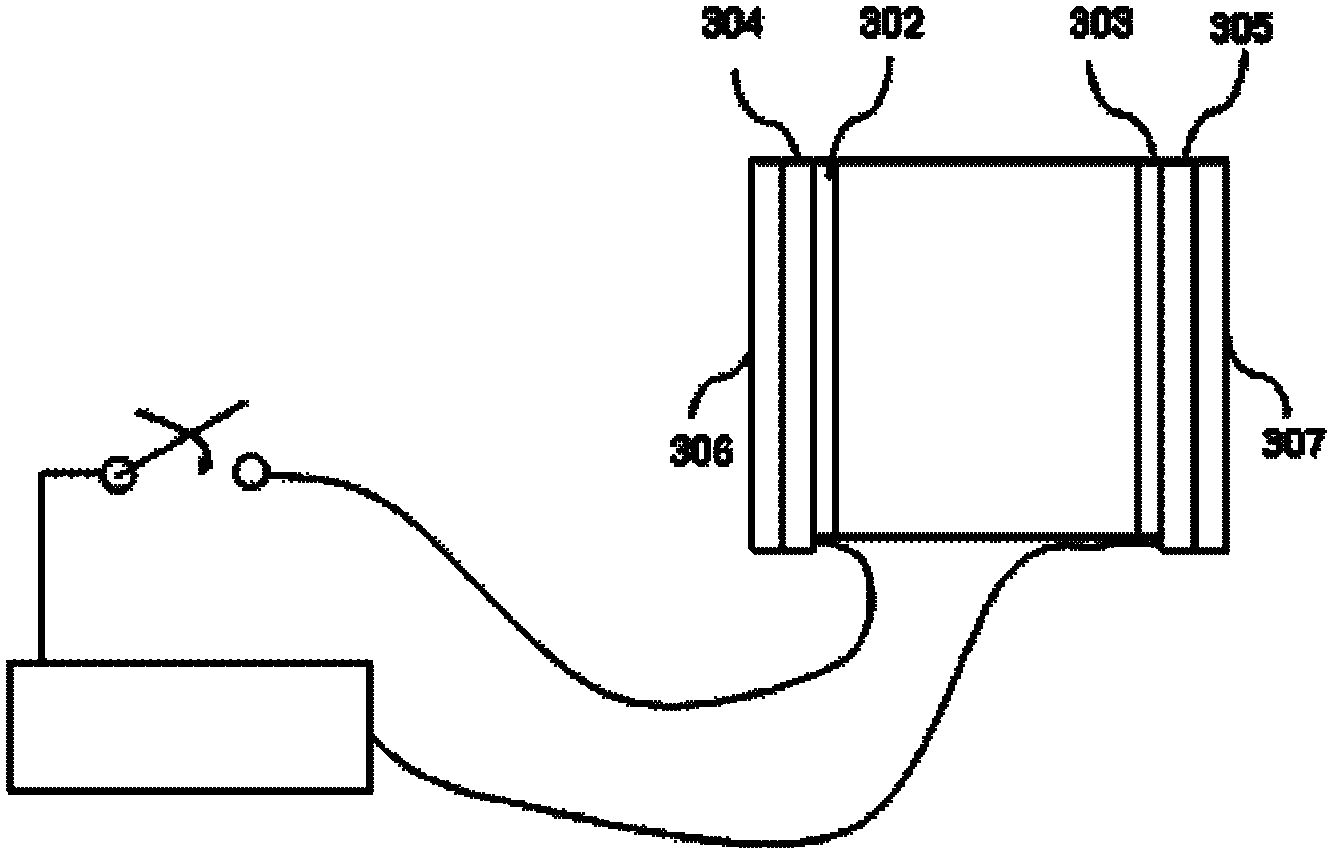

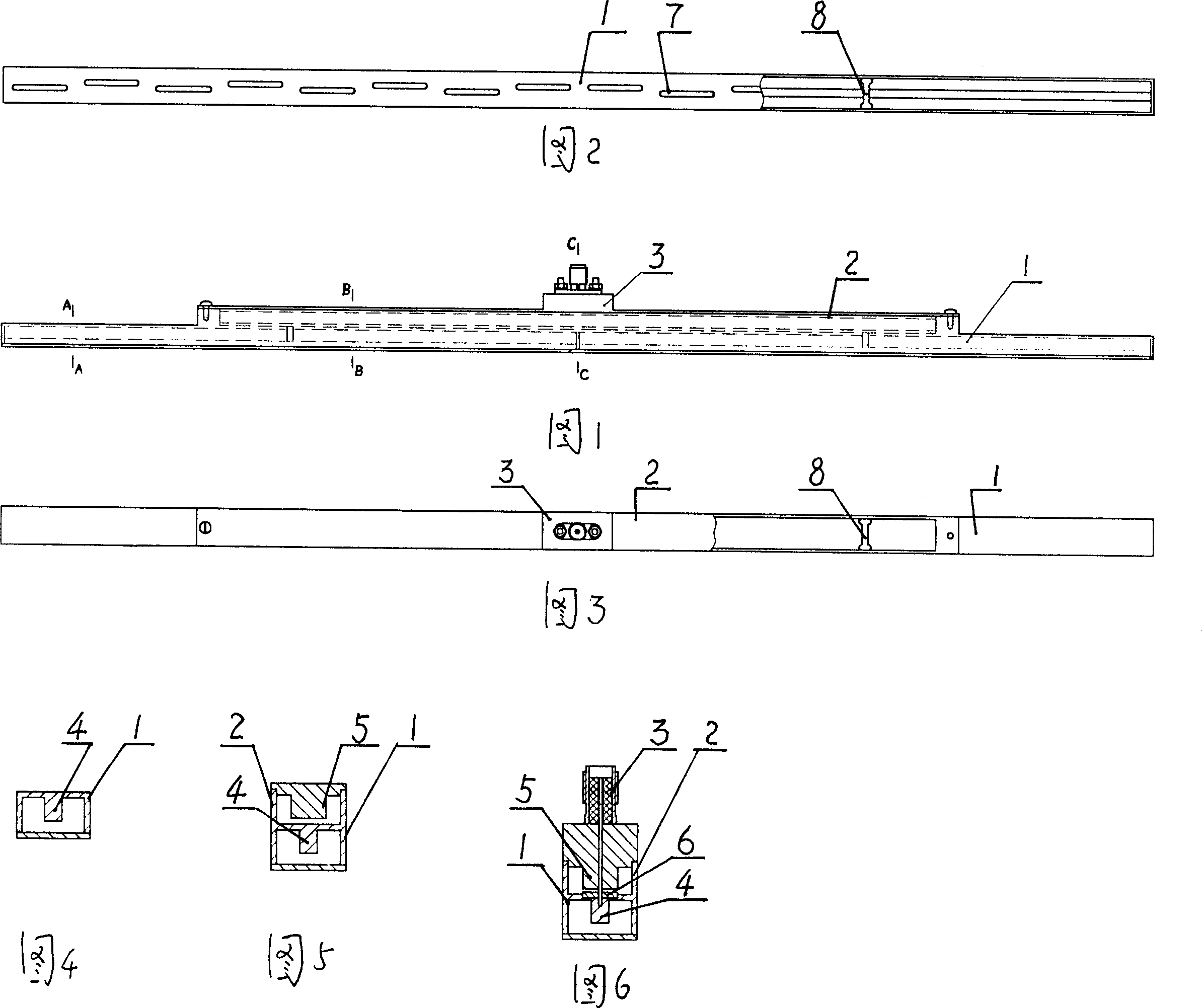

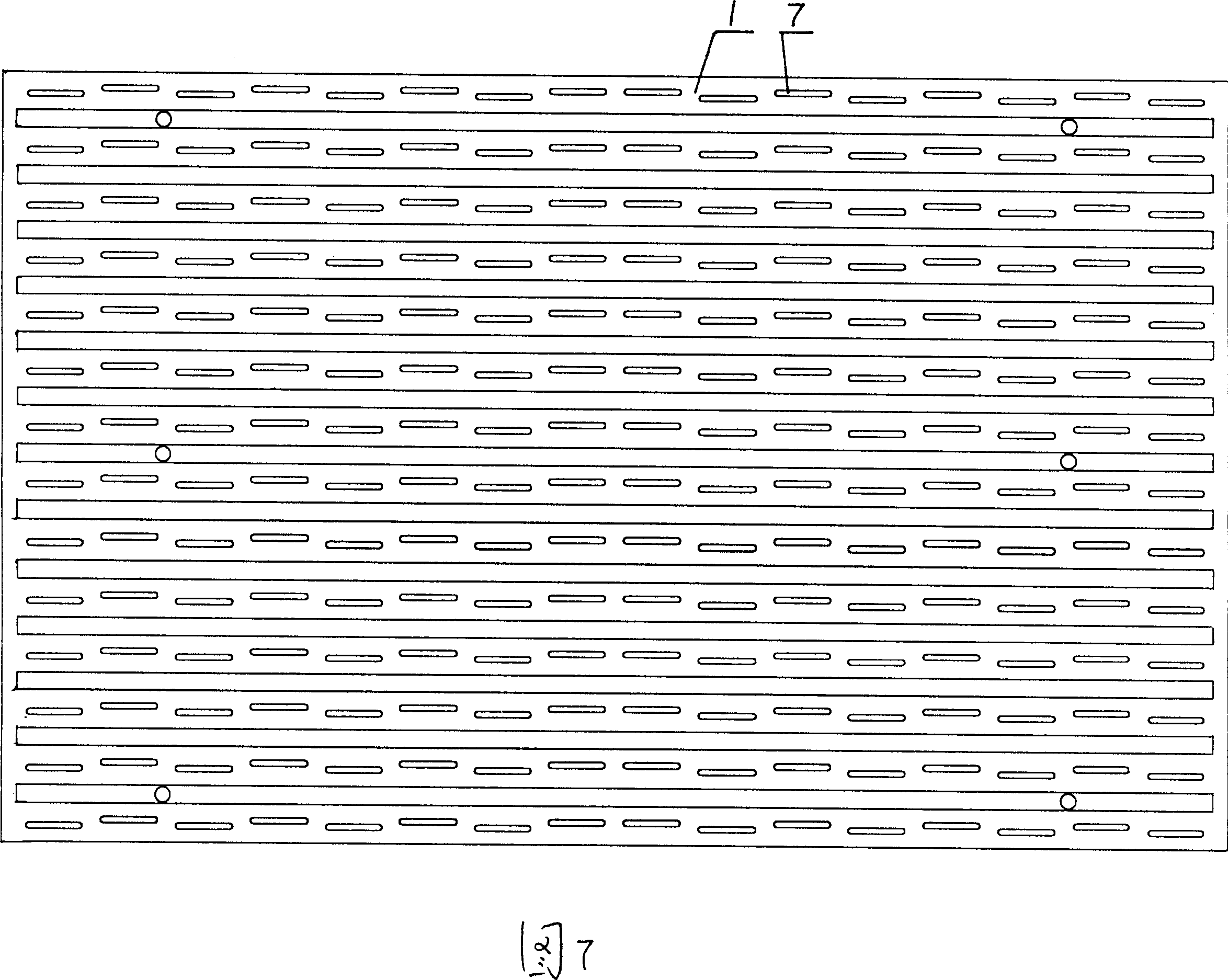

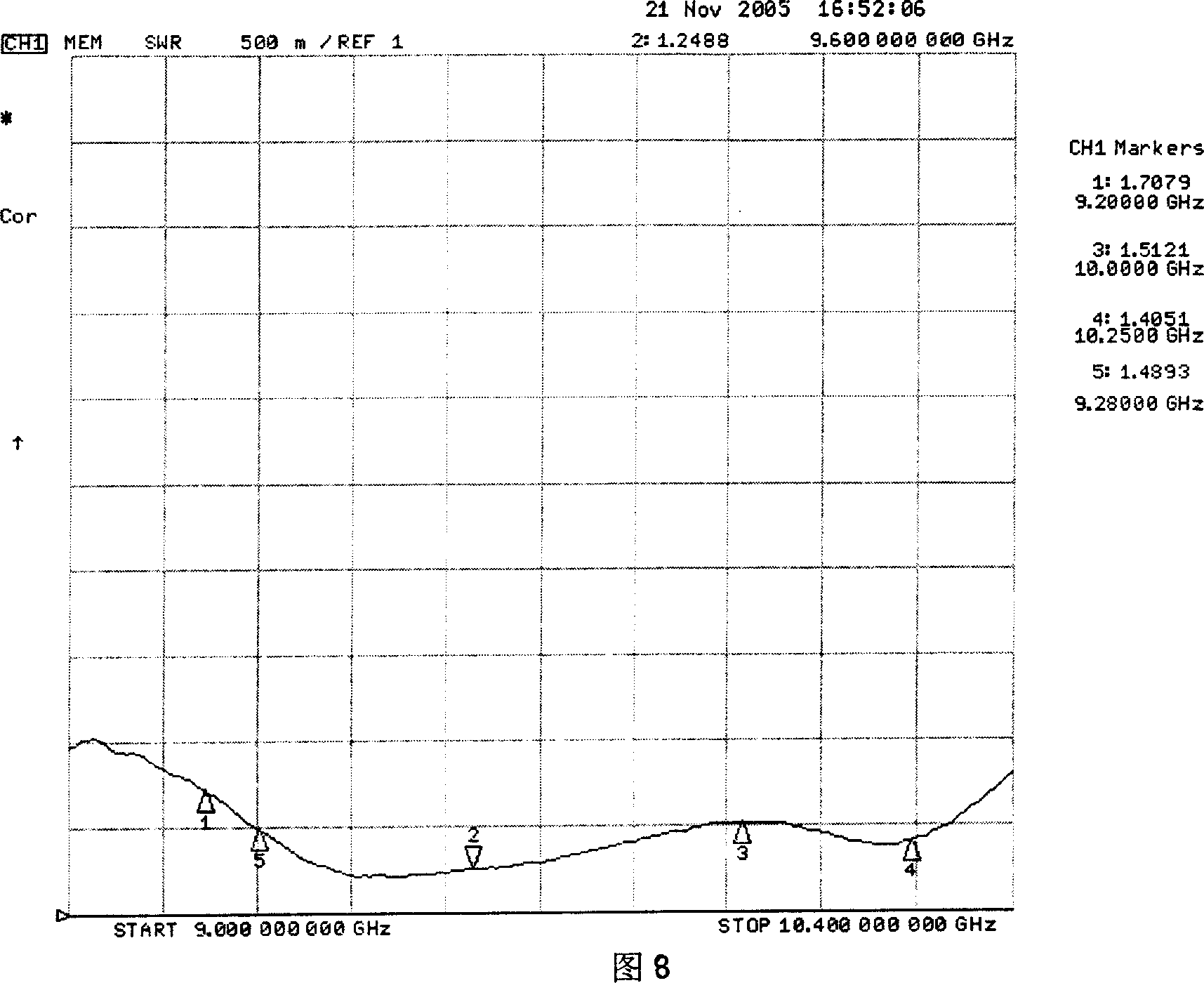

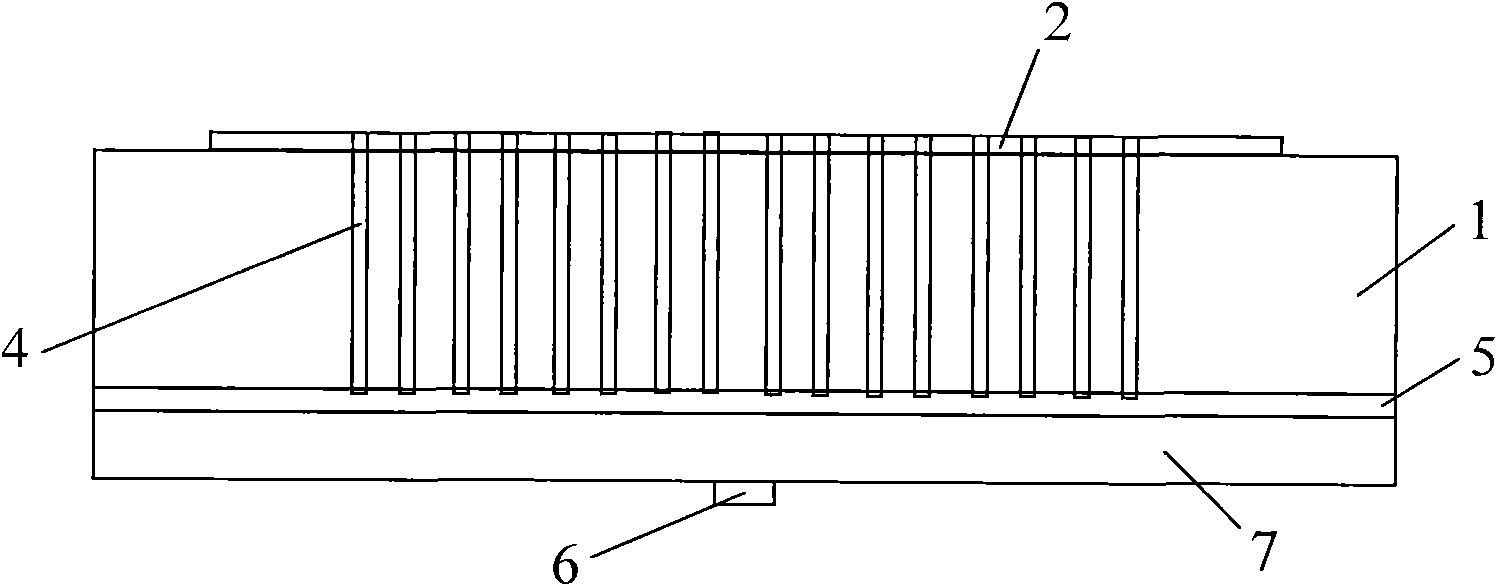

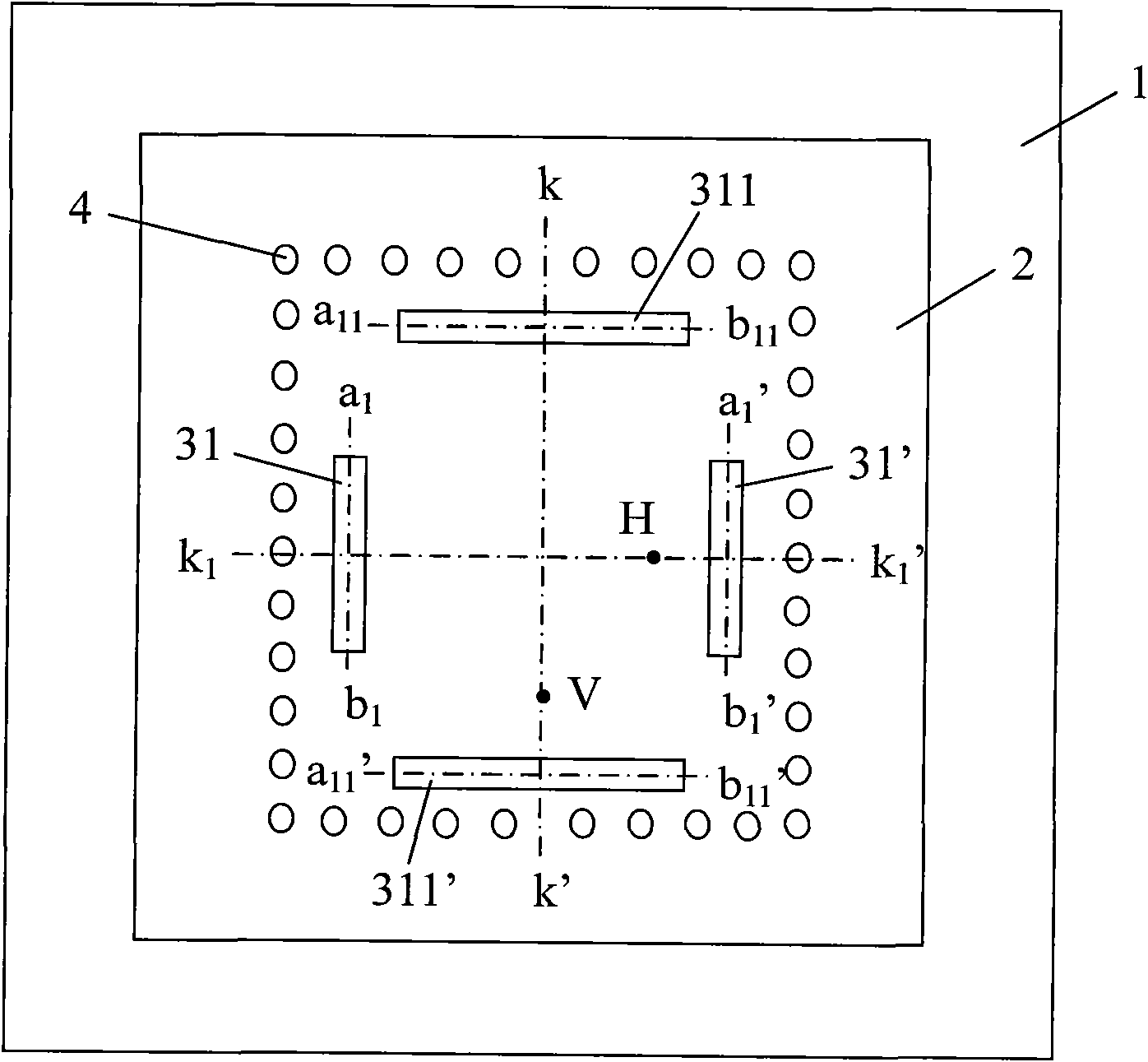

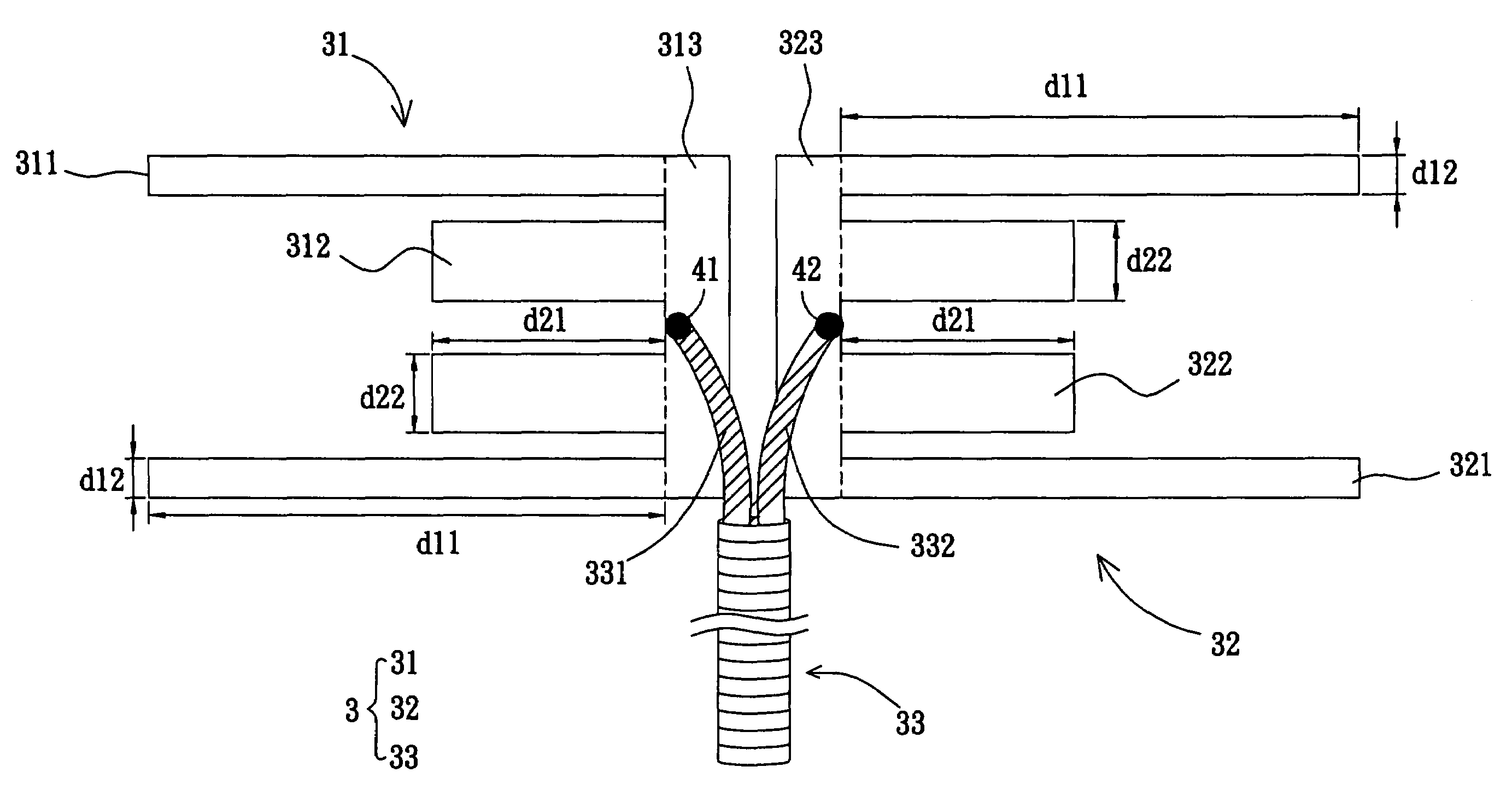

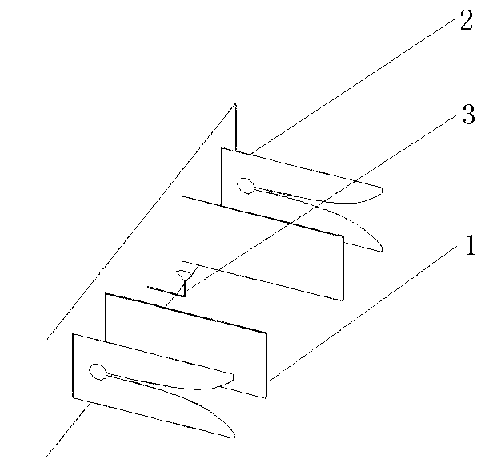

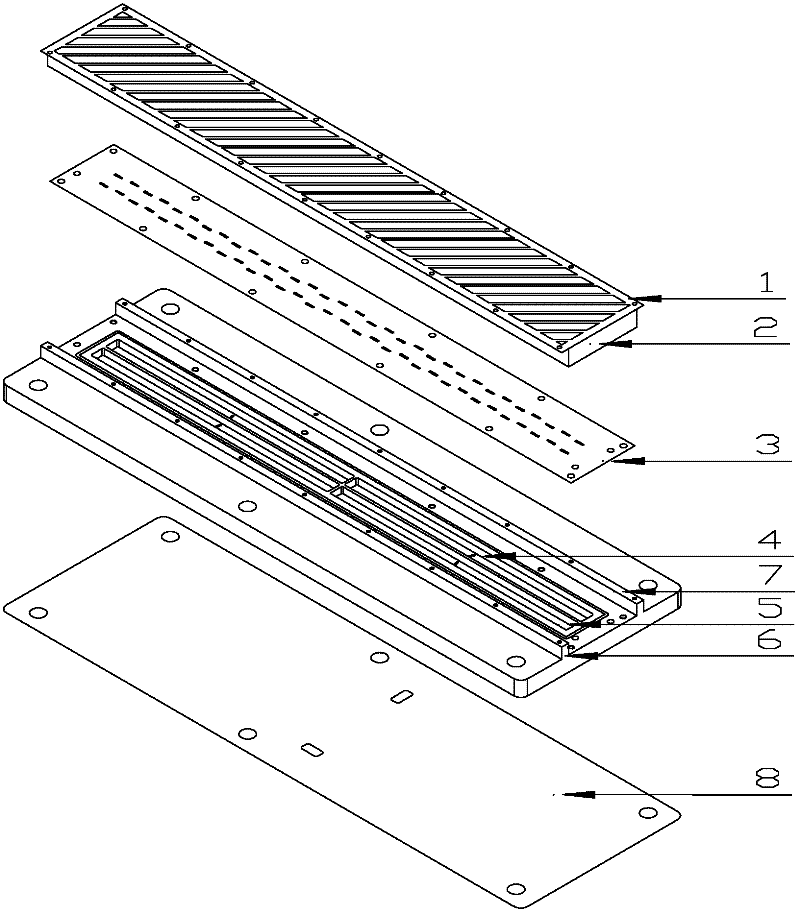

Inter-board perpendicular interconnection circuit structure for substrate integrated ridge waveguide

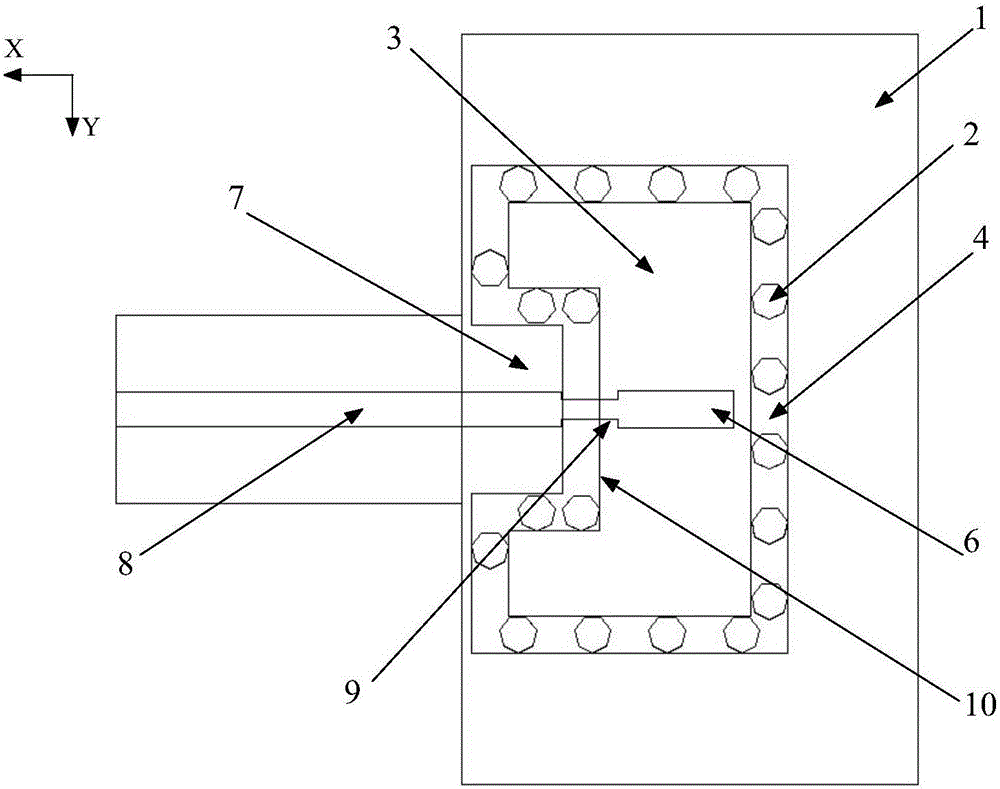

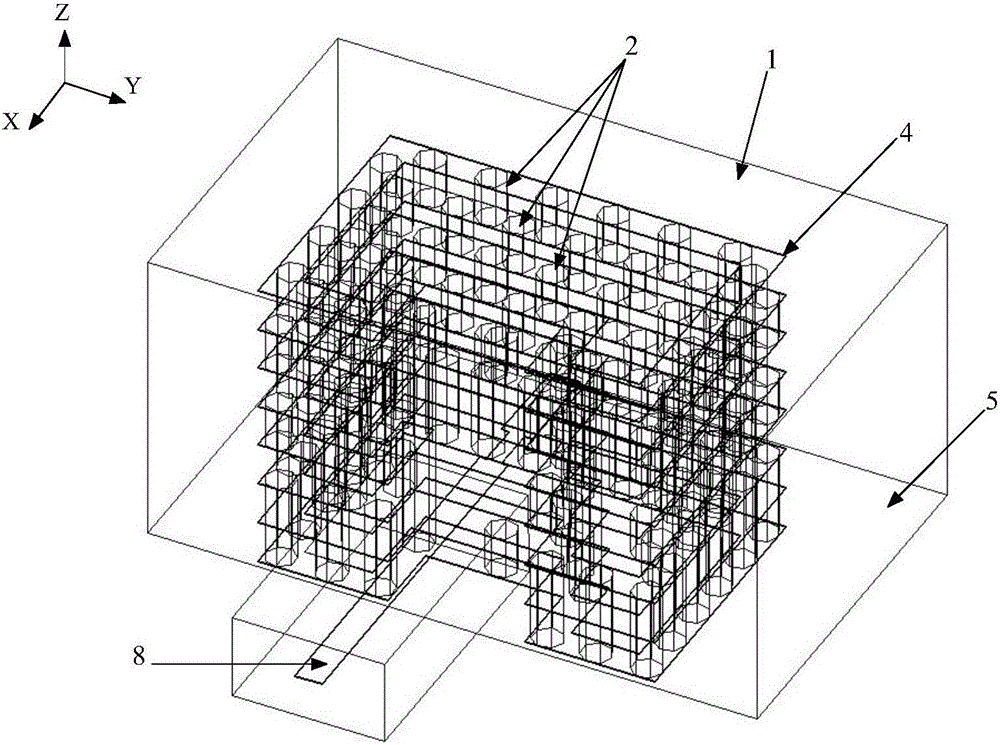

The invention provides an inter-board perpendicular interconnection circuit structure for a substrate integrated ridge waveguide (SIRW), and aims to provide a millimeter wave inter-board perpendicular interconnection circuit structure with small volume, easy integration, high interconnection property and long-term reliability. The inter-board perpendicular interconnection circuit structure is implemented by the following technical scheme: the SIRW (3) perpendicular to the surface of a base board is integrated on an LTCC multilayered circuit board (1); a substrate integrated ridge waveguide opening is etched in a corresponding outlet in the metal ground on the surface of the LTCC multilayered circuit board (1); Z-direction metalized filling holes (2) are arranged to form a metal hole gate array to equivalently form the waveguide wall and single-side ridges in the waveguide; metallic shield holes and probe restraining cavities (7) on the two sides of a 50-ohm strip line (8) are arranged at the equal spacing; and the alignment pressing and connection of the SIRW interfaces on the opposite sides between two boards is realized through pin hole alignment, so that the perpendicular interconnection transition of the millimeter wave signal between two boards in a way of 50-ohm strip line-SIRW-SIRW-50-ohm strip line is realized consequently.

Owner:10TH RES INST OF CETC

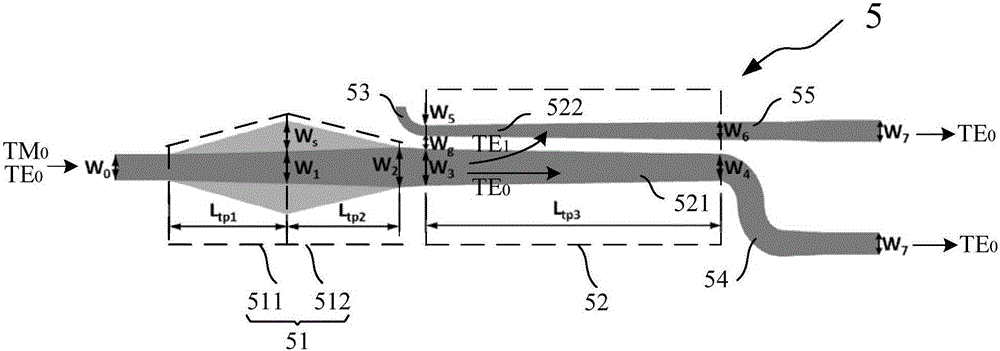

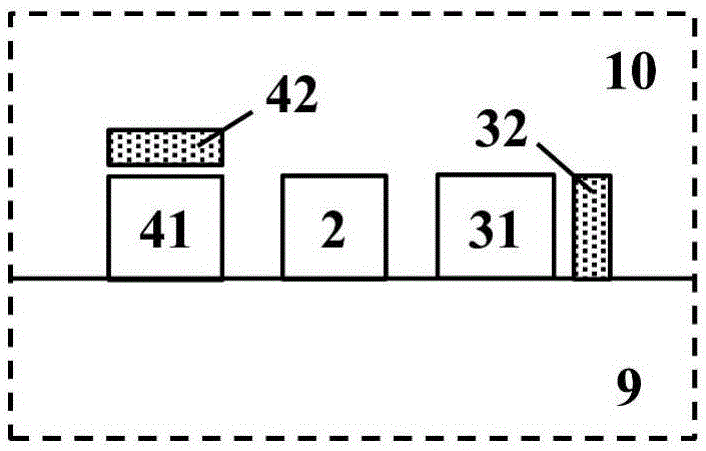

Polarization beam splitter rotator and design method thereof

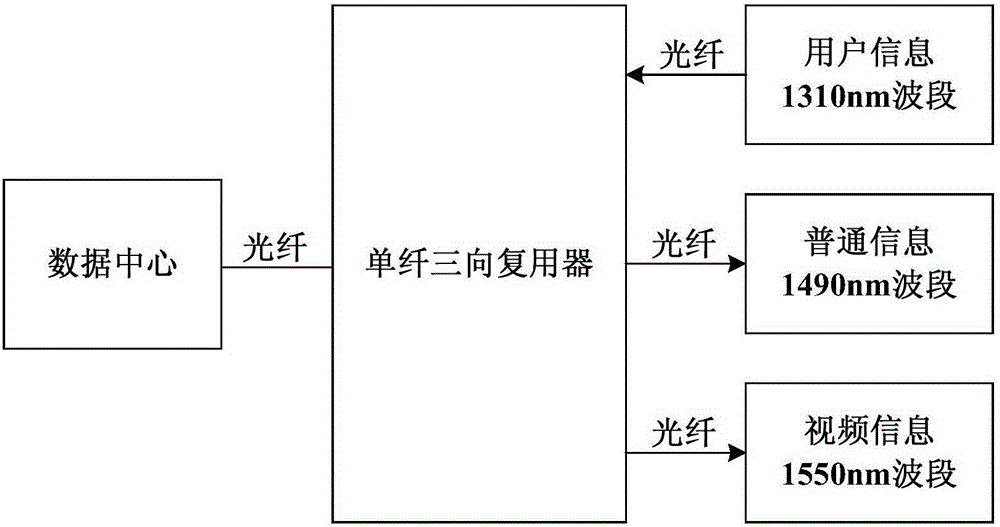

InactiveCN105223647AImprove practicalityImprove working bandwidthOptical light guidesMultiplexerSingle fiber

The invention provides a polarization beam splitter rotator and a design method thereof. The polarization beam splitter includes a double-layer trapezoidal mode converter and a reverse tapered coupler which are connected in series; the double-layer trapezoidal mode converter converts a transverse magnetic wave zero-order mode into a transverse electric wave first-order mode, and the reverse tapered coupler converts the transverse electric wave first-order mode into a transverse electric wave zero-order mode. The width of a first trapezoidal waveguide and a second trapezoidal waveguide is selected, and according to a relation between waveguide length and mode conversion efficiency, the length of the first trapezoidal waveguide and the second trapezoidal waveguide is determined; and the width of a third trapezoidal waveguide and a fourth trapezoidal waveguide is selected, and according to a relation between the waveguide length and mode conversion loss, the length of the reverse tapered coupler is determined. Characteristics of large working bandwidth, high conversion efficiency and high manufacturing tolerance and the like are realized through parameter optimization, the polarization beam splitter rotator can be used for improving practicability of a single-fiber three-way multiplexer, in addition, a manufacturing method is simple, is compatible with a standard silicon photon processing technological process, and the polarization beam splitter rotator and the design method thereof have relatively high practical value and good application prospects.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

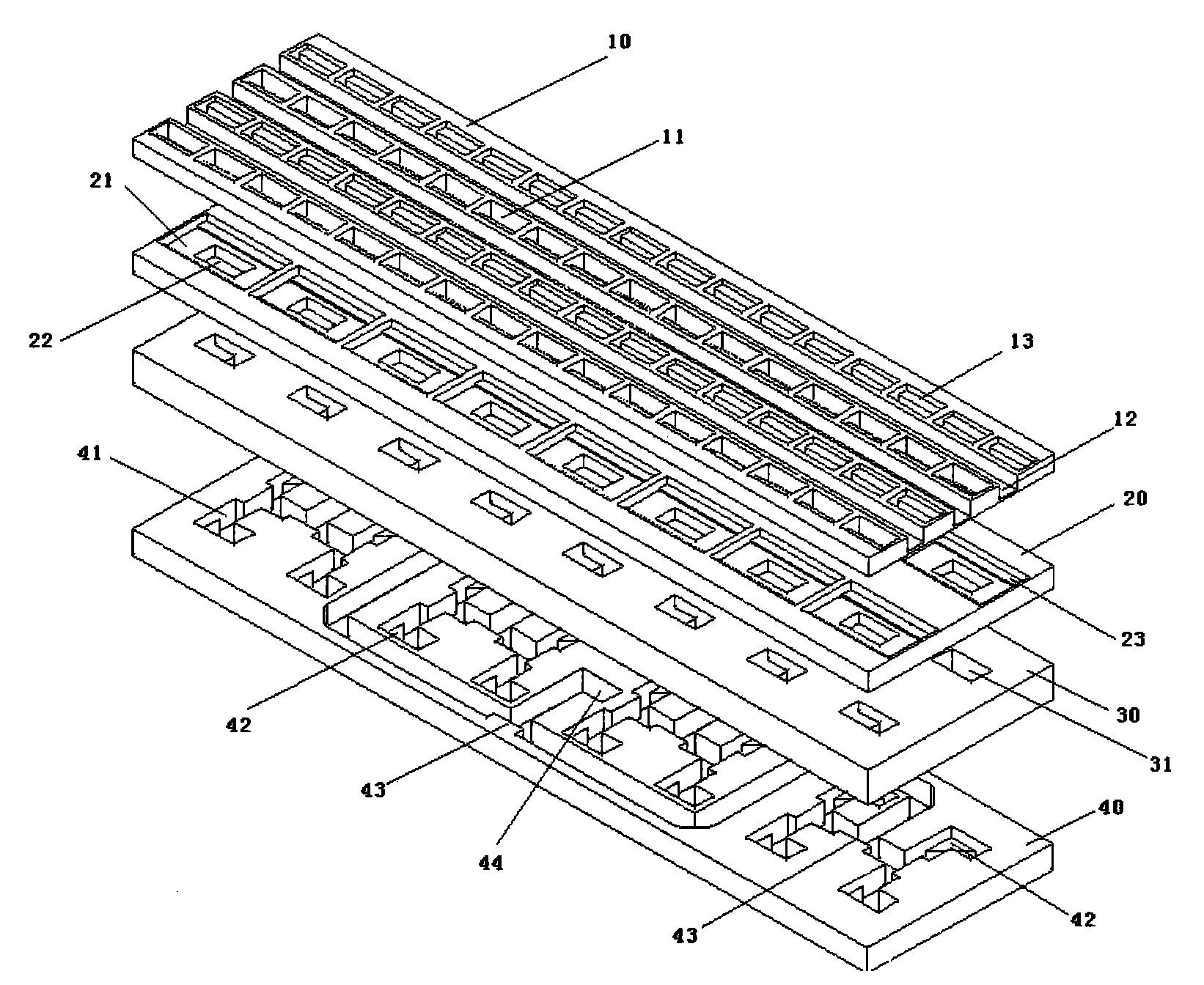

Waveguide flat array antenna

InactiveCN102064380AAvoid complex welding processesExpand standing wave bandwidthWaveguide mouthsAntenna arraysElectricityWaveguide

The invention provides a waveguide flat array antenna, which has the characteristics of broadband and high-efficiency feed. Rectangular open waveguides 11 are used as radiation units; four rectangular open waveguides in one group form a sub array, and are arranged in a 2*2 rectangle and supplied with broadband equal-amplitude in-phase feed by a rectangular cavity 21; and in order to ensure efficient transmission of electromagnetic wave, the joint of each rectangular open waveguide 11 and the rectangular cavity 21 is provided with matched steps 13 and 23. The center of the rectangular cavity 21 is provided with a rectangular window 22 which is connected with a feed network of the next layer. In order to ensure smooth signals, a rectangular matching block 42 is arranged at the feed network corner connected with each rectangular window 22. The feed network consists of multistage parallel E-T so as to ensure that the antenna has enough bandwidth. The transceiving capacity of circularly polarized wave is realized by arranging a circularly polarized cover. Compared with the conventional flat antenna, the waveguide flat array antenna has broader bandwidth and higher feed efficiency.

Owner:李峰

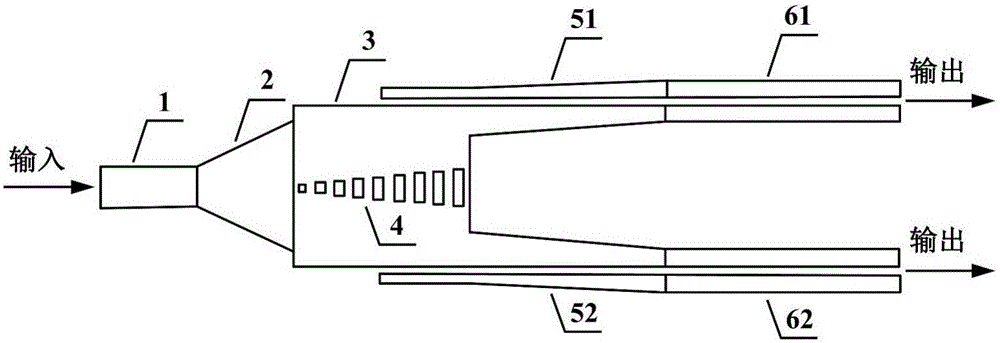

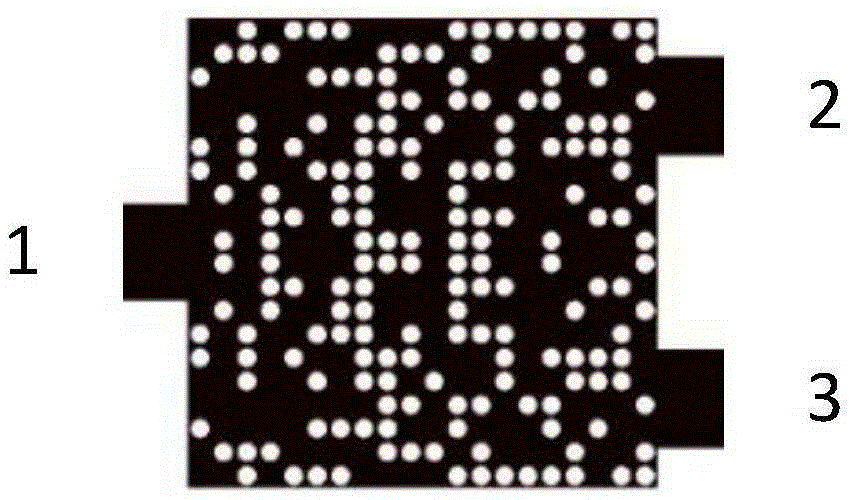

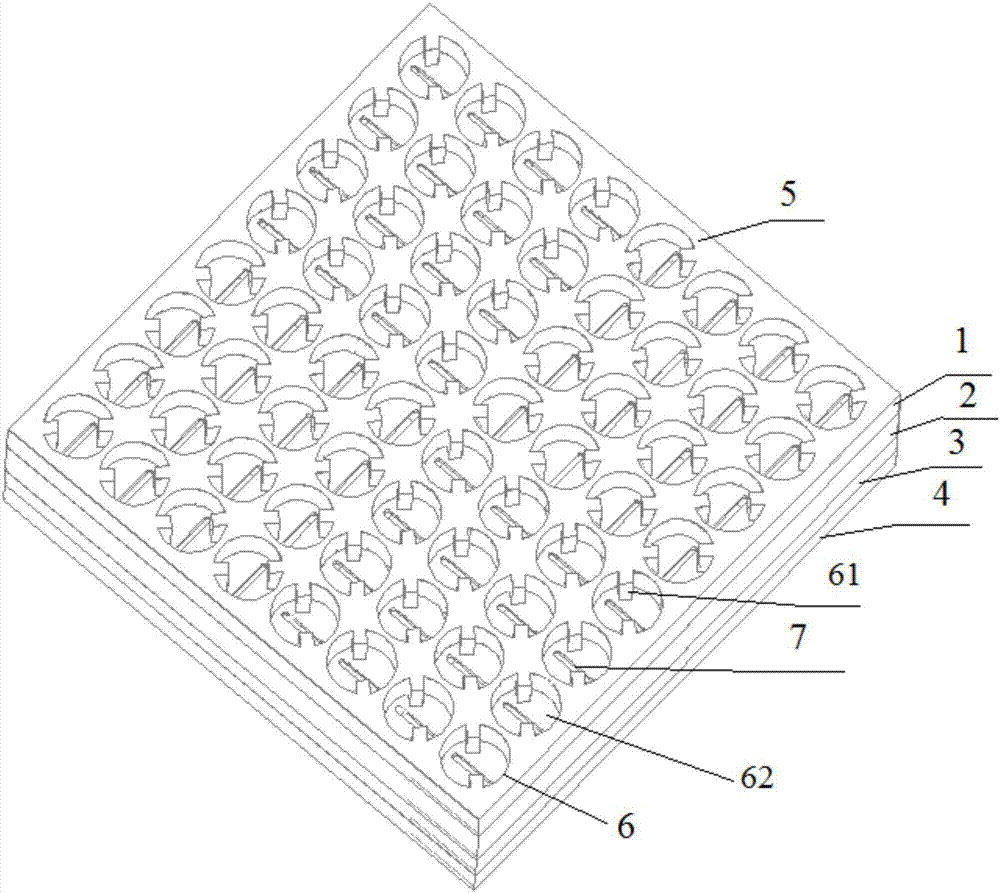

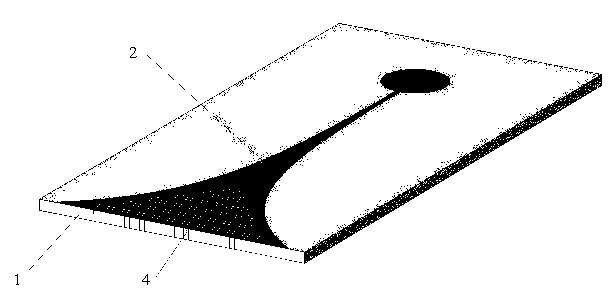

Silicon-based groove waveguide integrated type optical power splitter

The invention discloses a silicon-based groove waveguide integrated type optical power splitter, which can be applied to the field of silicon-based photonics. The output end of an input nano wire waveguide (1) is connected to a taper transition waveguide (2). The output end of the taper transition waveguide (2) is connected to an embedded sub-wavelength grating type multi-mode waveguide (3). A first mode conversion waveguide (51), a second mode conversion waveguide (52), a first output groove waveguide (61) and a second output groove waveguide (62) are positioned at the two sides of the embedded sub-wavelength grating type multi-mode waveguide (3). A sub-wavelength grating (4) is positioned in the middle of the embedded sub-wavelength grating type multi-mode waveguide (3). The silicon-based groove waveguide integrated type optical power splitter has the advantages of being low in insertion loss and low in reflection loss, enabling balanced power splitting, being convenient to manufacture, etc. Moreover, the optical power splitter can be integrated with a groove waveguide type Mach-Zehnder interferometer type optical modulator, and then the performance of a silicon-based optical modulator can be further improved.

Owner:SOUTHEAST UNIV

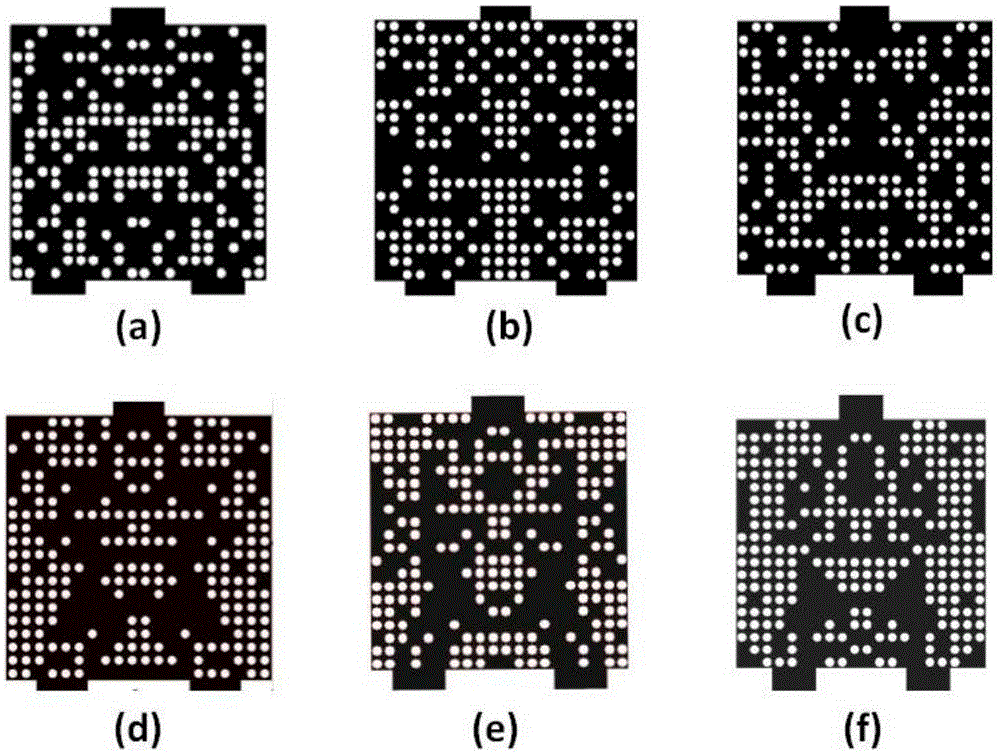

Silicon-based optical beam splitter and manufacturing method thereof

The invention discloses a silicon-based metamaterial optical beam splitter and a manufacturing method thereof and belongs to the field of integrated photoenic devices. A 50:50 optical power beam splitter in the prior art is narrow in working broadband, poor in port consistency and high in loss. The optical beam splitter comprises a substrate. The substrate comprises an input waveguide and two output waveguides. A coupling area composed of N*N pixel blocks of the same size are positioned between the input waveguide and the output waveguides. By punching the pixel blocks, a special punching array is formed through an optimization algorithm. Due to the fact that configuration of an air hole array of sub-wavelength sizes can be equivalent to an evenly tempolabile refractive index distribution area, different wavelengths can be guided simultaneously, so that the goal of effectively outputting the different wavelengths at an output port can be achieved, and the goal of large working bandwidth is achieved.

Owner:HUAZHONG UNIV OF SCI & TECH

Graphene electrode-based reflecting liquid crystal phase shift unit

ActiveCN106532200AWorking bandwidthSimple structureWaveguide type devicesAntennasLiquid-crystal displayPhase shifted

The invention discloses a graphene electrode-based reflecting liquid crystal phase shift unit, which comprises two upper and lower layers of dielectric substrates, wherein a liquid crystal layer is injected into a gap between the two upper and lower layers of dielectric substrates; a plurality of metal patches which are sequentially connected in series through a connection line are arranged on the lower surface of the upper layer of dielectric substrate to form a layer of metal microstrip structure; a graphene layer completely covers the upper surface of the lower layer of dielectric substrate to form a graphene electrode; and a metal layer completely covers the lower surface of the lower layer of dielectric substrate to form a metal grounding electrode. The continuous phase shift characteristic is obtained within a broadband in an electric control manner; and the graphene electrode-based reflecting liquid crystal phase shift unit has the characteristics of being small and easy to process.

Owner:HEFEI UNIV OF TECH

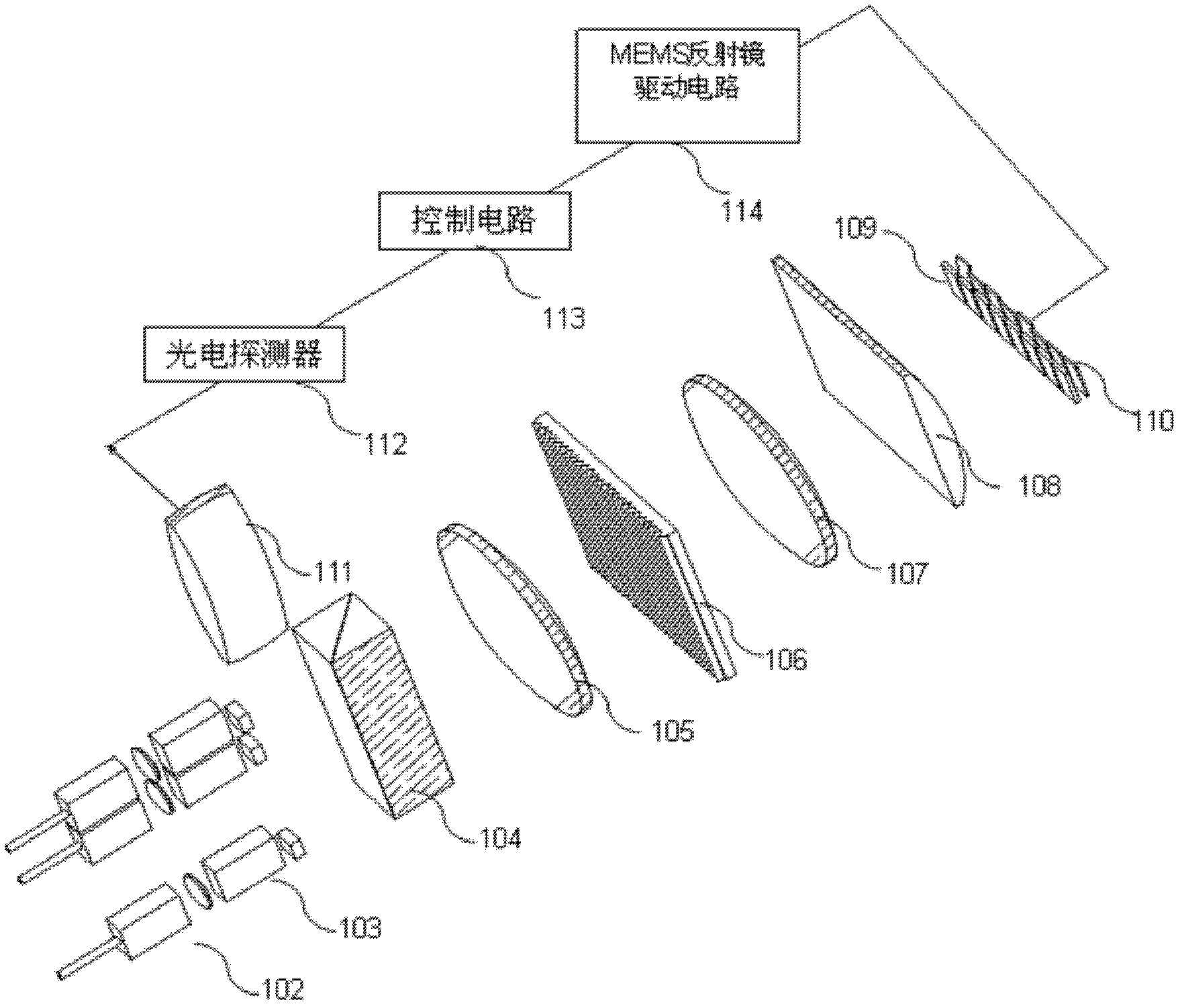

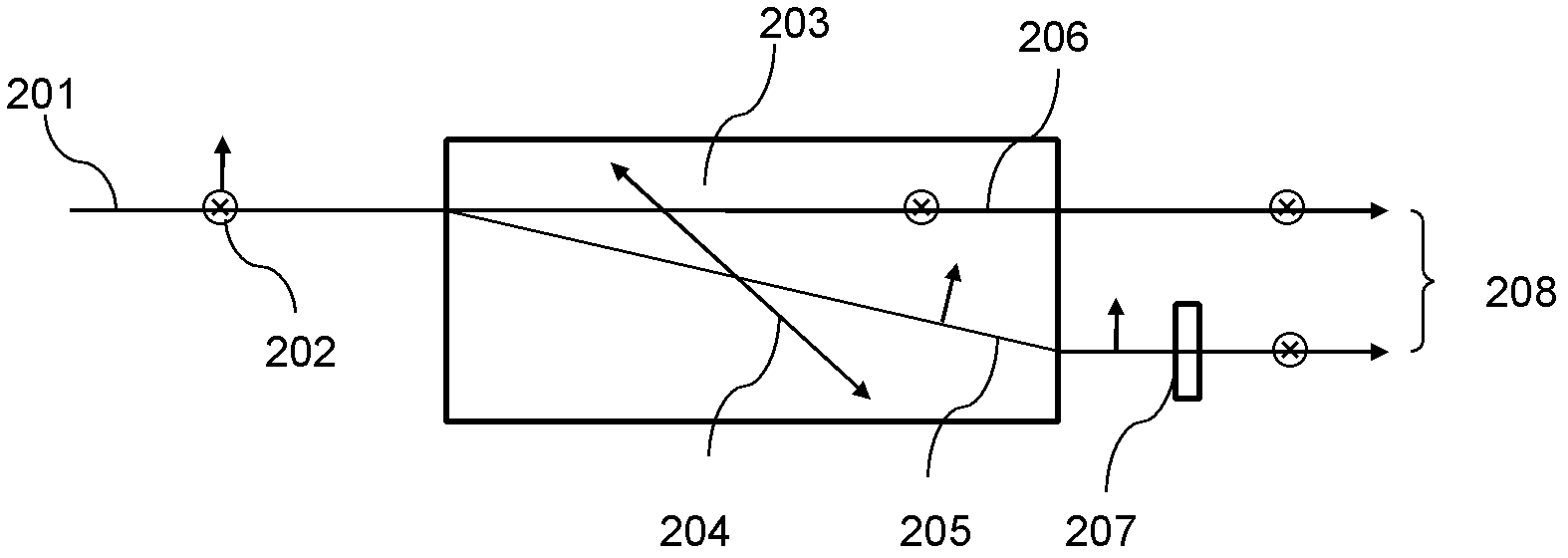

Wavelength-selective optical switch

ActiveCN102590953ASimple designRealize switchingCoupling light guidesUltrasound attenuationLength wave

The invention relates to a wavelength-selective optical switch which comprises a polarization conversion part, an attenuation reflectance part, a wavelength channel opening and closing unit and a reflecting mirror driving part. The polarization conversion part is arranged between an light inputting / outputting part and an light dividing part; the attenuation reflectance part comprises one-dimensional MEMS (micro-electronic-mechanical) reflecting mirror arrays, is arranged on the surface of the output end of the light dividing part and used for reflecting a part of wavelength channel irradiated in by the light dividing part; the wavelength channel opening and closing unit comprises a liquid crystal assembly and is used for controlling the opening and the closing of the wavelength channel; the liquid crystal assembly is arranged between the MEM reflecting mirror arrays; and the reflecting mirror driving part is used for setting the angels of the reflecting surfaces of MEMS reflecting mirrors in the attenuation reflectance part and outputting the light of each wavelength channel to a set output port. The wavelength-selective optical switch adopts a liquid crystal unit array and the one-dimensional MEMS reflecting mirror arrays to realize the optical path switching and attenuating and the non-interference switching function.

Owner:BROADEX TECH

Piezoelectric array ultrasonic transducer

InactiveCN103240220AAvoid the generation of parasitic capacitanceHigh sensitivityMechanical vibrations separationElectricityBasement

The invention provides a piezoelectric array ultrasonic transducer, and belongs to the technical field of transducers and micro-processing. The piezoelectric array ultrasonic transducer comprises array (distributed) type upper electrodes, an integrated common lower electrode, piezoelectric films, insulation layers, array elements, a supporting layer, and monocrystalline silicon basements. The piezoelectric films are arranged between the upper electrodes and the lower electrode. The insulation layers are arranged among the upper electrode, the lower electrode and the piezoelectric films. The array elements arranged on the insulation layers comprises acoustic energy transmission and absorption cavities and vibration films at the bottoms of the array elements. The monocrystalline silicon basements are provided with vibration cavities. By the arrangement of adopting the common lower electrode and the array (distributed) type upper electrodes, same or different thicknesses are adopted in the vibration films at the bottoms of the array elements (the acoustic energy transmission and absorption cavities) and the piezoelectric films, so that the array elements can operate under either a same working frequency or different working frequencies, comprehensive performances of sensitivity and working bandwidth and stability of the comprehensive performances of the transducer can be improved effectively, and the piezoelectric array ultrasonic transducer has the advantages that integration is good, packaging is facilitated, industrial production is benefited and the like.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

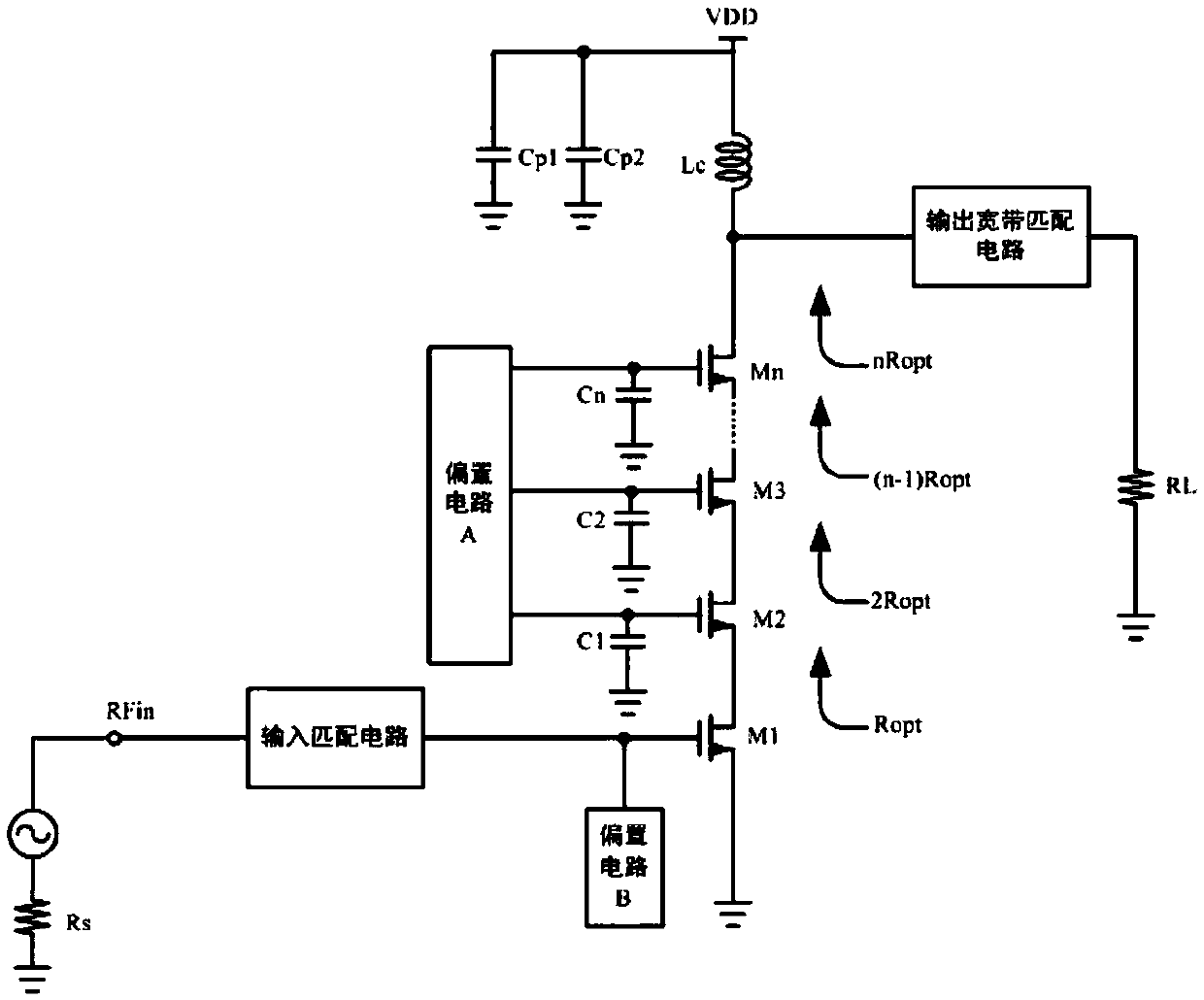

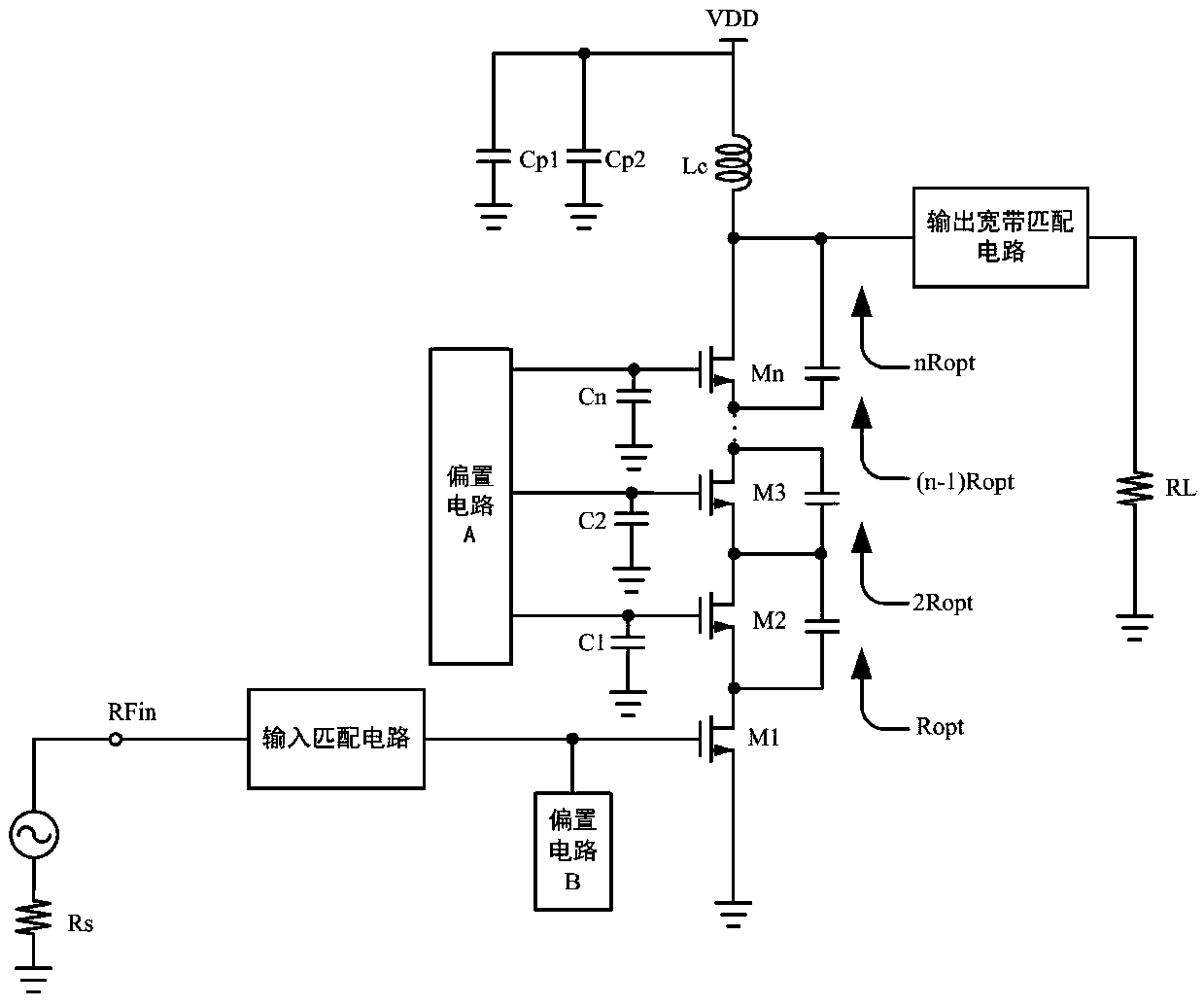

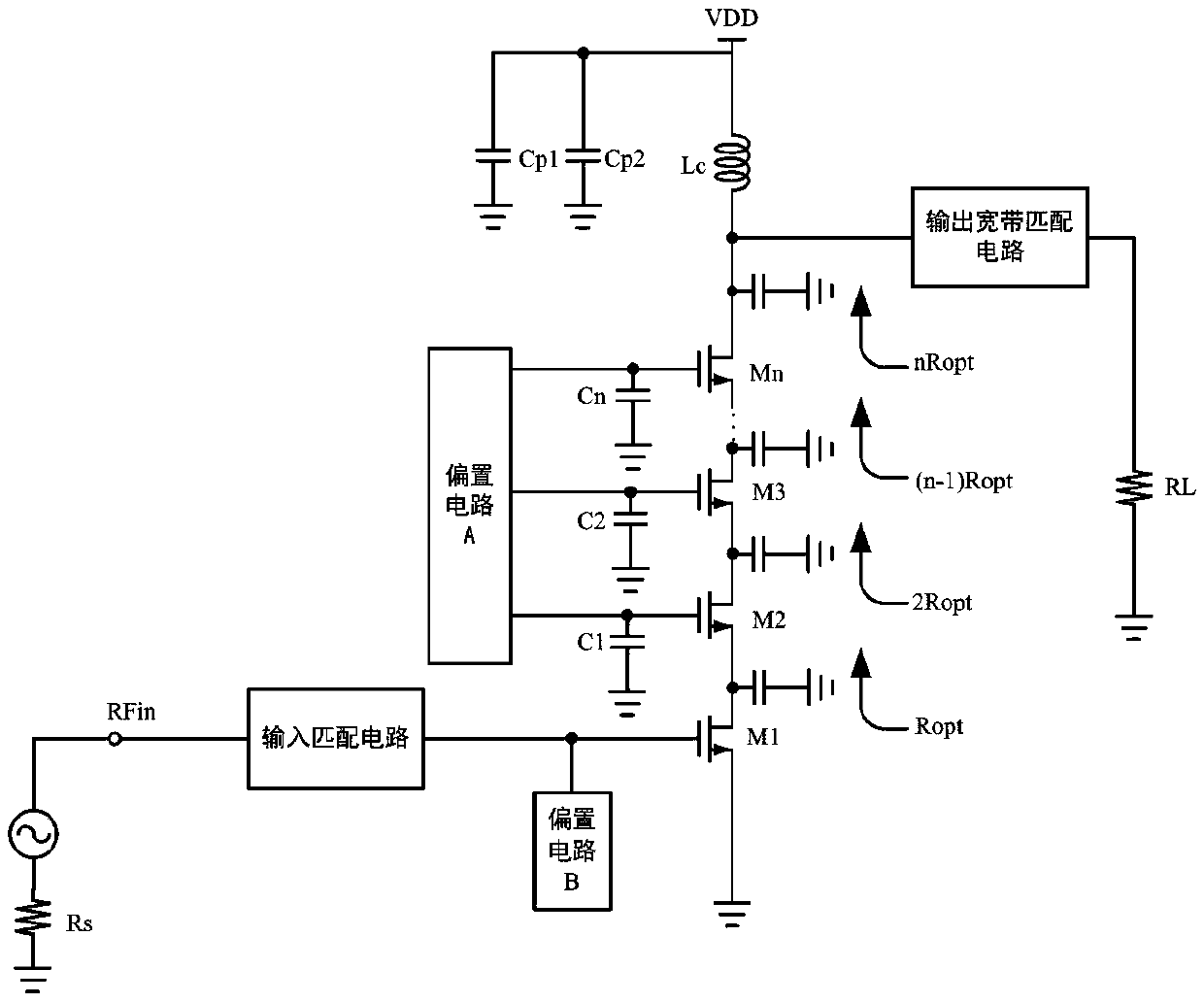

Radio-frequency power amplifier with stack structure

InactiveCN105515542AImprove pressure resistanceIncreased power output capabilityAmplifier modifications to reduce non-linear distortionHigh frequency amplifiersCapacitanceAudio power amplifier

The invention discloses a radio-frequency power amplifier with a stack structure. The radio-frequency power amplifier comprises an input matching circuit, an output broadband matching circuit, a biasing circuit A, a biasing circuit B and a power amplification circuit, and the power amplification circuit is formed by stacking of at least two transistors with drains and sources connected. A radio-frequency signal source is connected with a grid electrode of the bottom transistor of the power amplification circuit through the input matching circuit, the biasing circuit B is connected with the grid electrode of the bottom transistor, and the source of the bottom transistor is grounded. The drain of the top transistor of the power amplification circuit is connected with a load through the output broadband matching circuit. Integral linearity, output voltage swing, operation bandwidth, power efficiency, power gain and maximum output power of the radio-frequency power amplifier are increased, and excellent second harmonic inhibition effects are achieved.

Owner:臻智微芯(广州)技术有限公司

Broadband single ridge waveguide broadside longitudinal seam standing-wave antenna

InactiveCN101000979AReduce the overall heightReduce widthPolarised antenna unit combinationsWaveguidesCouplingImpedance matching

This invention relates to a broadband single ridge waveguide slot array, resolving that the size, weight, loss, scanning angle and other aspects of existing waveguide slot array can not meet the special requirements. Its features are: the radiation waveguide has symmetric metal-single ridge on the center line of hemline and rectangular cross section, which connects with the feeding waveguide just below the bottom. The feeding waveguide has symmetric metal-single ridge on the hemline centerline. Coupling gap is set between radiation and feeding waveguide horizontally. The invention uses a single-ridge radiation waveguide to reduce the width of antenna, divides array into a number of sub-ones and feeds by power divider to improve the working bandwidth, uses ridge waveguide antenna to improve efficiency and reduce processing difficulties, uses coaxial connectors to easily realize impedance matching.

Owner:CHINA ELECTRONIC TECH GRP CORP NO 38 RES INST

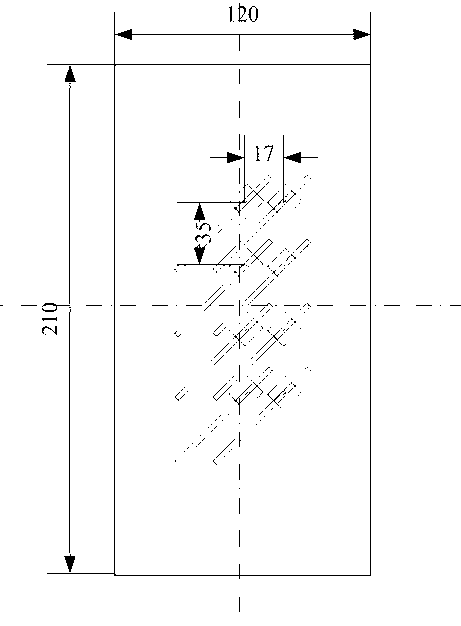

Millimetre wave planar antenna and array thereof

InactiveCN101982898ASmall dielectric lossUniform radiation patternAntenna arraysRadiating elements structural formsPhysicsRadiation

The invention discloses a millimetre wave planar antenna and an array thereof, wherein the millimetre wave planar antenna includes a metal patch, a medium substrate, a metal floor board and ground poles, the metal patch is placed on an upper surface of the medium substrate, and a lower surface of the medium substrate is fixed with an upper surface of the metal floor board; the metal patch is parallel to the upper surface of the metal floor board; the metal patch is provided with at least one pair of same first bar-shaped channels, each pair of first bar-shaped channels are distributed in bilateral symmetry form, symmetrical centre lines of each pair of bar-shaped channels are superposed, a centre line in a length direction of each first bar-shaped channel is parallel to each other, and length of each first bar-shaped channel is 1 / 2 of an operating wavelength; the ground poles vertically penetrate through the medium substrate, the ground poles are circularly distributed at intervals at the periphery of a region where the first bar-shaped channels are distributed, and two ends of each ground pole are respectively contacted with the metal patch and the metal floor board. The invention can reduce loss of a millimetre wave antenna, improve radiation efficiency of the millimetre wave antenna, simultaneously, guarantee work bandwidth of the antenna, and improve antenna gain.

Owner:ZHEJIANG UNIV

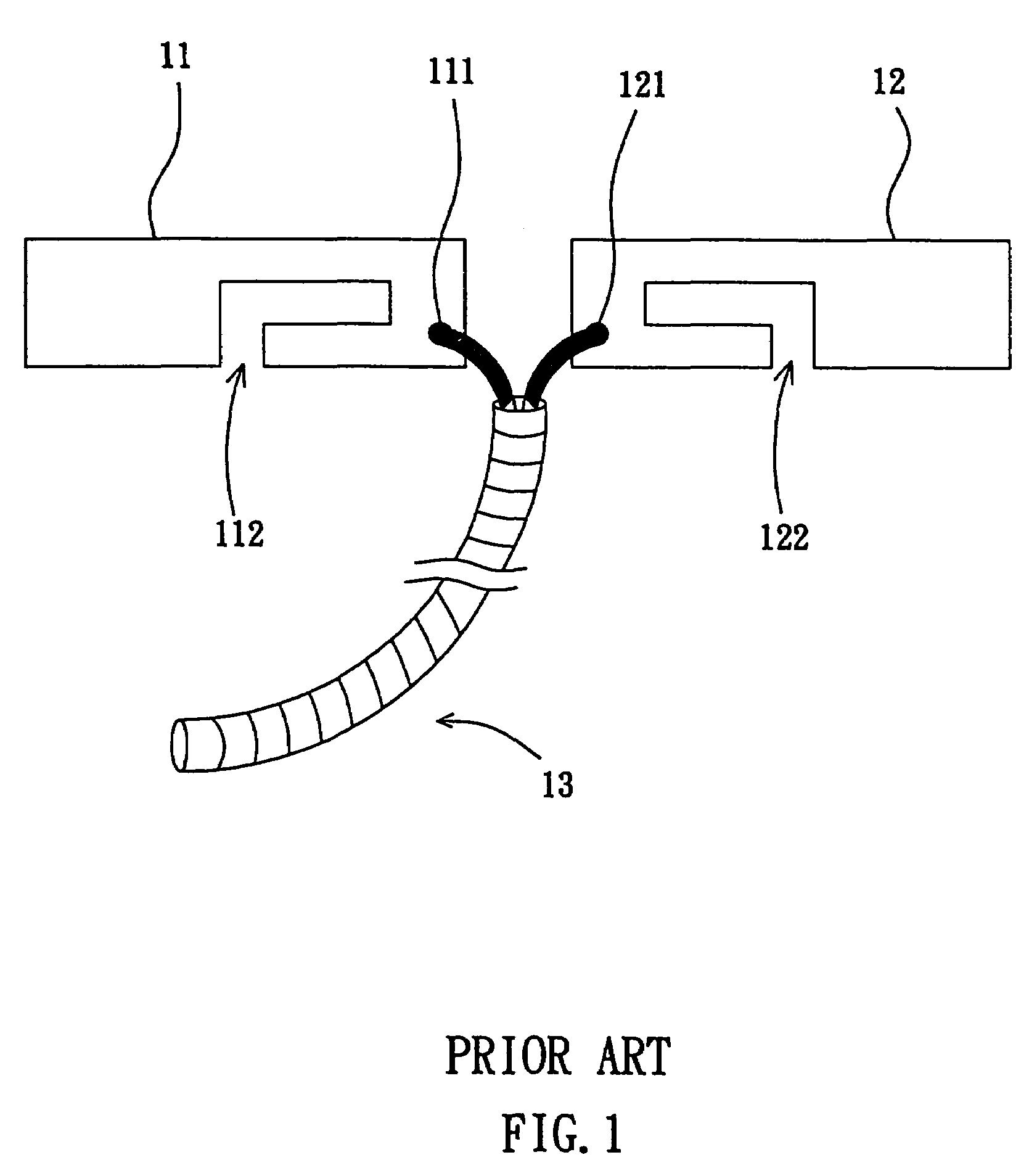

Dual band and broadband flat dipole antenna

InactiveUS7042415B2Improve working bandwidthUsable bandwidthSimultaneous aerial operationsIndividually energised antenna arraysBroadbandDipole antenna

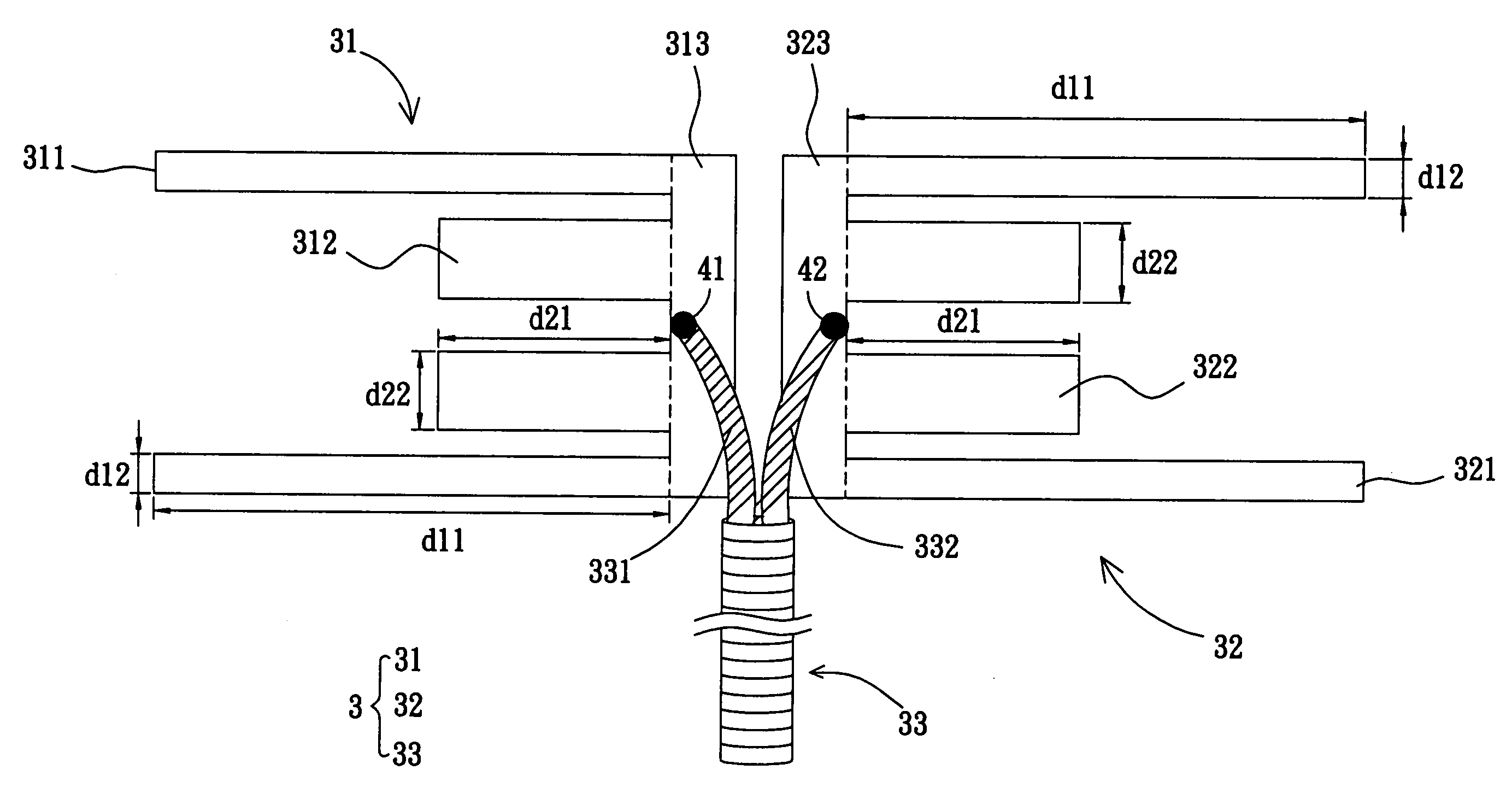

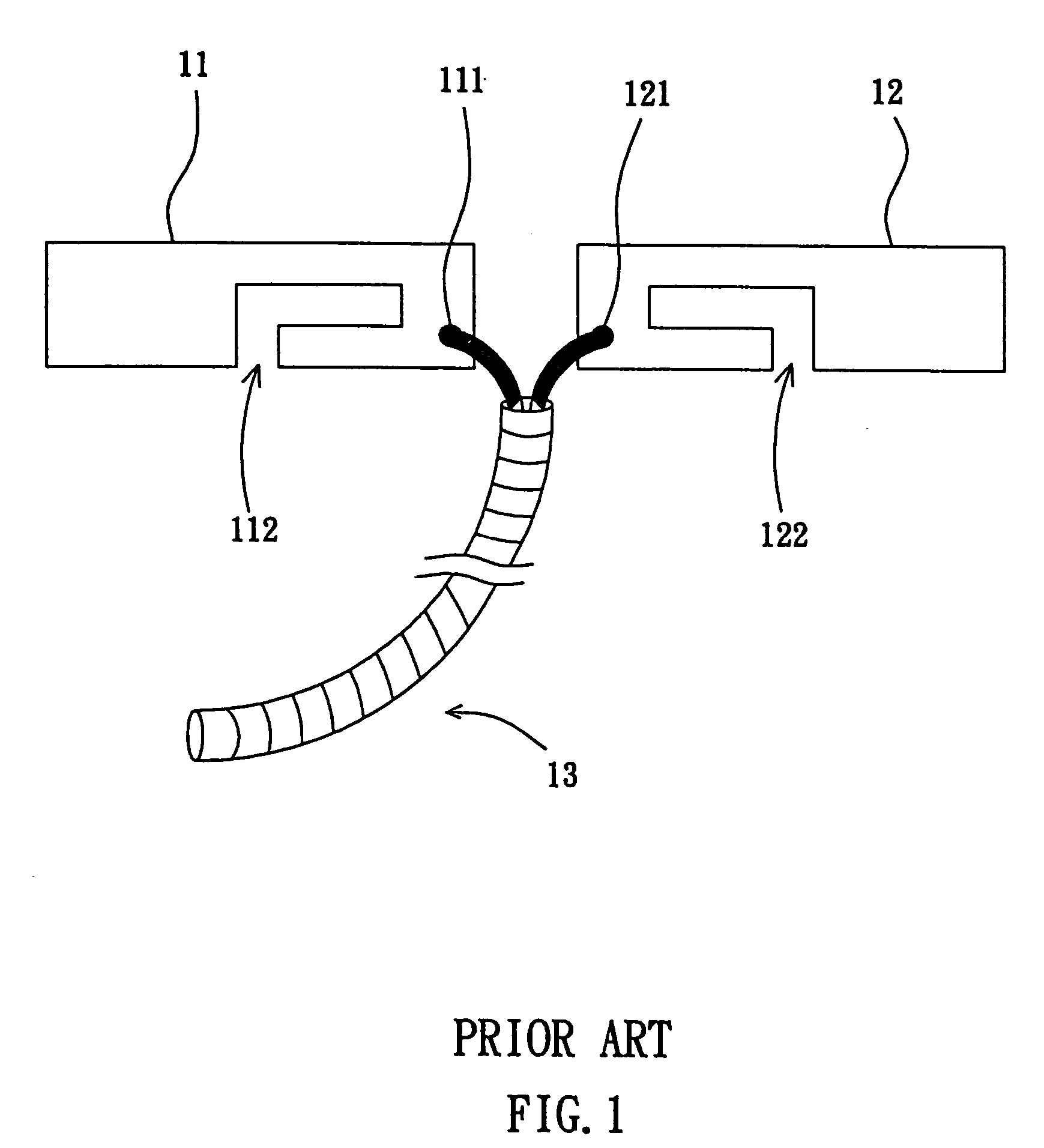

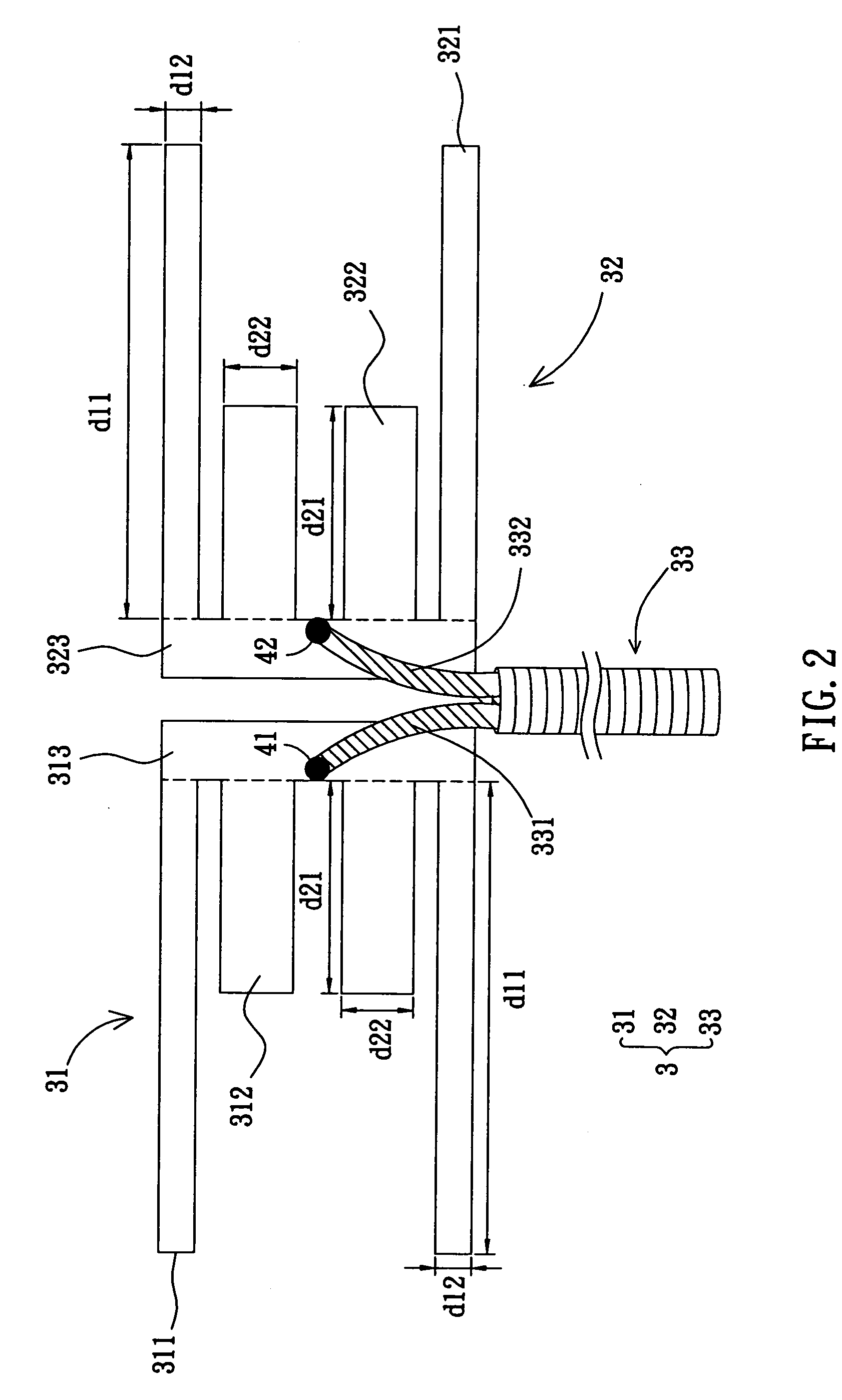

A dual band and broadband flat dipole antenna comprises a first radiating body, a second radiating body, and a conductivity element. The first radiating body has two first frequency-radiating parts, two second frequency-radiating parts, and a first electrically connecting part. The first and second frequency-radiating parts are extended from a side of the first electrically connecting part. The second frequency-radiating parts are disposed between the first frequency-radiating parts. The second radiating body similar to the first radiating body has two first frequency-radiating parts, two second frequency-radiating parts, and a second electrically connecting part. The first and second frequency-radiating parts are extended from a side of the second electrically connecting part with the direction reversing to the extending direction of the first radiating body. The conductivity element has a conductivity body and a grounding conductor electrically connected with the first electrically connecting part and the second electrically connecting part, respectively.

Owner:ARCADYAN

Multi-frequency dual-polarized omnidirectional antenna

ActiveCN106848530AImprove working bandwidthRealize slot coupling feedParticular array feeding systemsAntenna supports/mountingsOmnidirectional antennaWi-Fi

The invention discloses a multi-frequency dual-polarized omnidirectional antenna and relates to the technical field of dual-polarized omnidirectional antennas. The multi-frequency dual-polarized omnidirectional antenna comprises upper and lower two microstrip antenna arrays, an asymmetric bi-conical antenna, a multiplexer, a side feed structure and an antenna radome, wherein the upper and lower two microstrip antenna arrays are parallel to each other and are arranged at the top and the middle of the asymmetric bi-conical antenna separately; the multiplexer is arranged at inner side of the bottom of the asymmetric bi-conical antenna; and the side feed structure is arranged on the side of the whole antenna and connected with upper and lower two microstrip antenna array feed points and two output ports of the multiplexer separately. The multi-frequency dual-polarized omnidirectional antenna covers 2 / 3 / 4G and WLAN and Wi-Fi working bands, and has multi-frequency vertical and horizontal dual-polarized omnidirectional radiation functions. The upper microstrip antenna array is arranged at the top of the asymmetric bi-conical antenna to form orthogonal arrangement; the asymmetric bi-conical antenna is arranged at the center of the lower microstrip antenna array to form cored orthogonal arrangement. According to a structure combination method, the isolation degree between a vertically polarized port and a horizontally polarized port in a full band can be significantly improved and the operation bandwidth of the antenna is improved.

Owner:SOUTHEAST UNIV +1

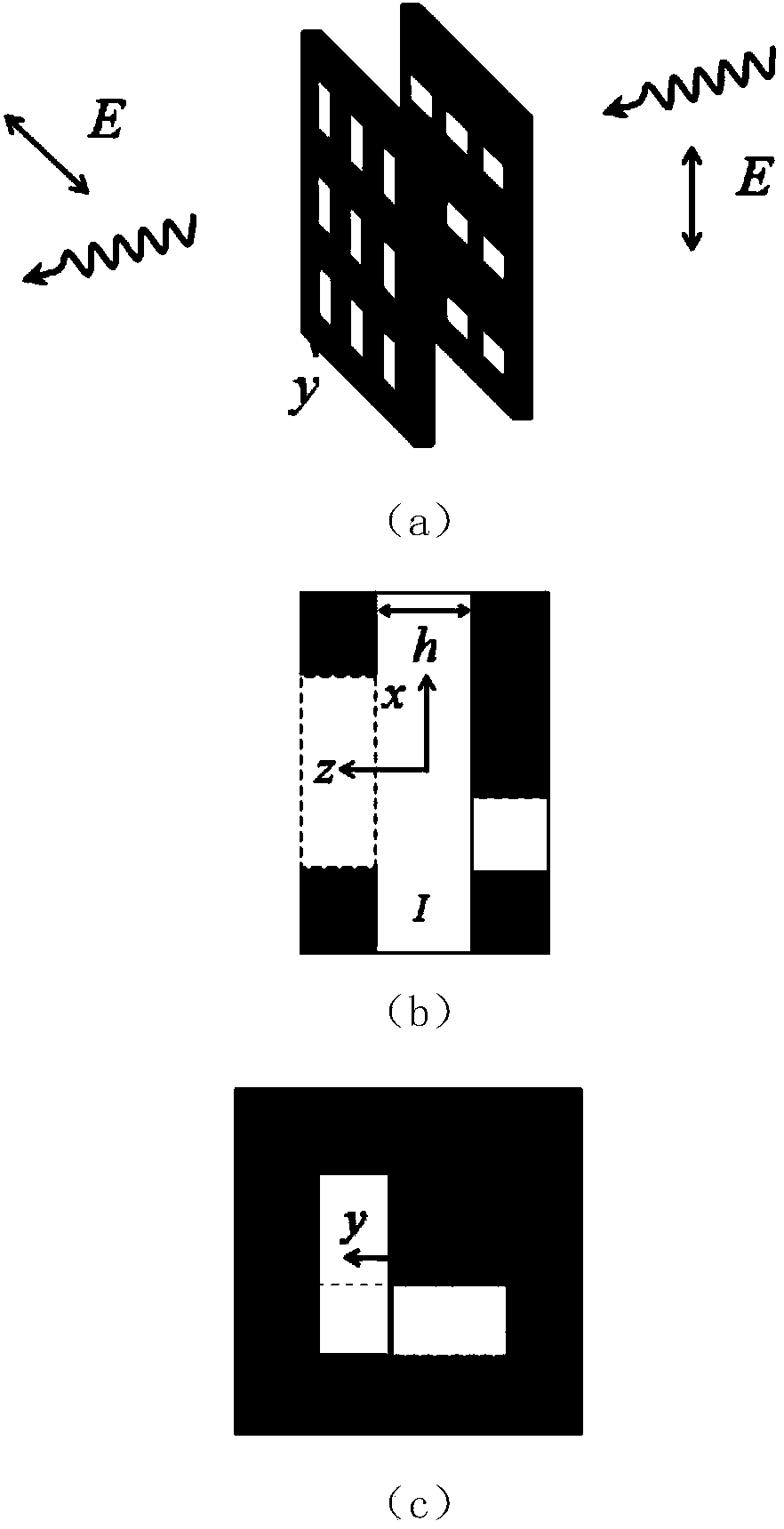

Subwavelength plasmon polarization converter

InactiveCN103645565AImprove the coupling effectImprove transmission/conversion efficiencyAntennasOptical elementsPolarizerWavelength

The invention discloses a subwavelength plasmon polarization converter which comprises an incident polarizer and an emission polarizer which are separated by a medium or air layer. Both the incident polarizer and the emission polarizer are made of plasmon materials, small holes with subwavelength dimensions are engraved on the two polarizers, an included angle is formed between each small hole on the incident polarizer and the corresponding small hole on the emission polarizer, and the end points of the above two small holes are in intersection. When the included angle of two small holes is less than 90 degrees, the incident polarizer only allows the coupling entering of one polarized electromagnetic wave, and the emission polarizer only allows the emission of an electromagnetic wave which is orthogonal with the above polarized direction. By using a near field coupling effect between orthogonal rectangular holes, according to the system, the limitation of the Malus law can be broken, and thus the electromagnetic wave generates effective transmission and the polarization direction is rotated for 90 degrees. The converter can be used as a single-direction transmitter, a subwavelength switch and a modulator.

Owner:NANJING UNIV OF TECH

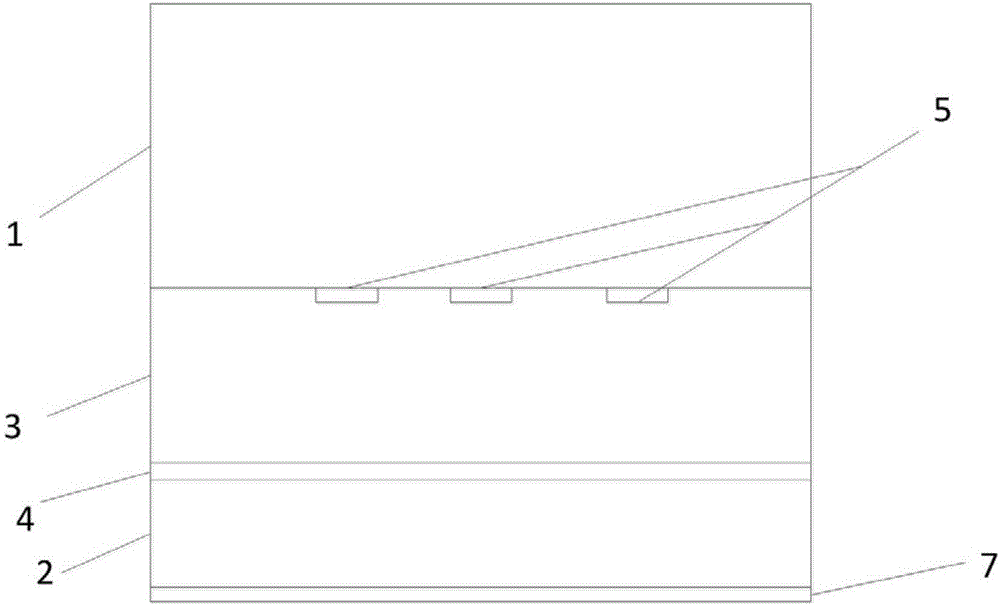

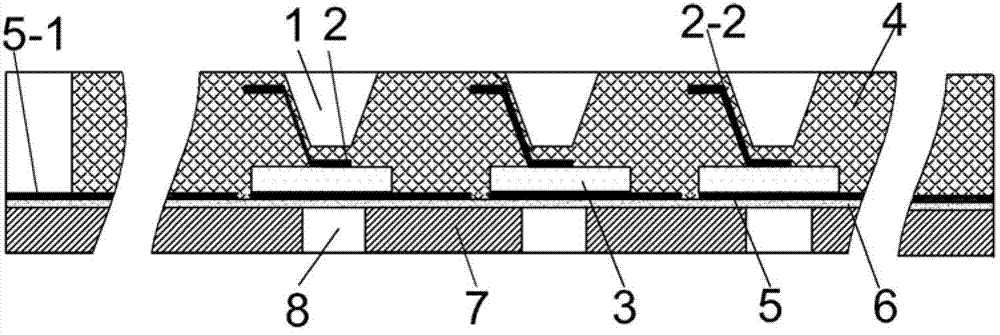

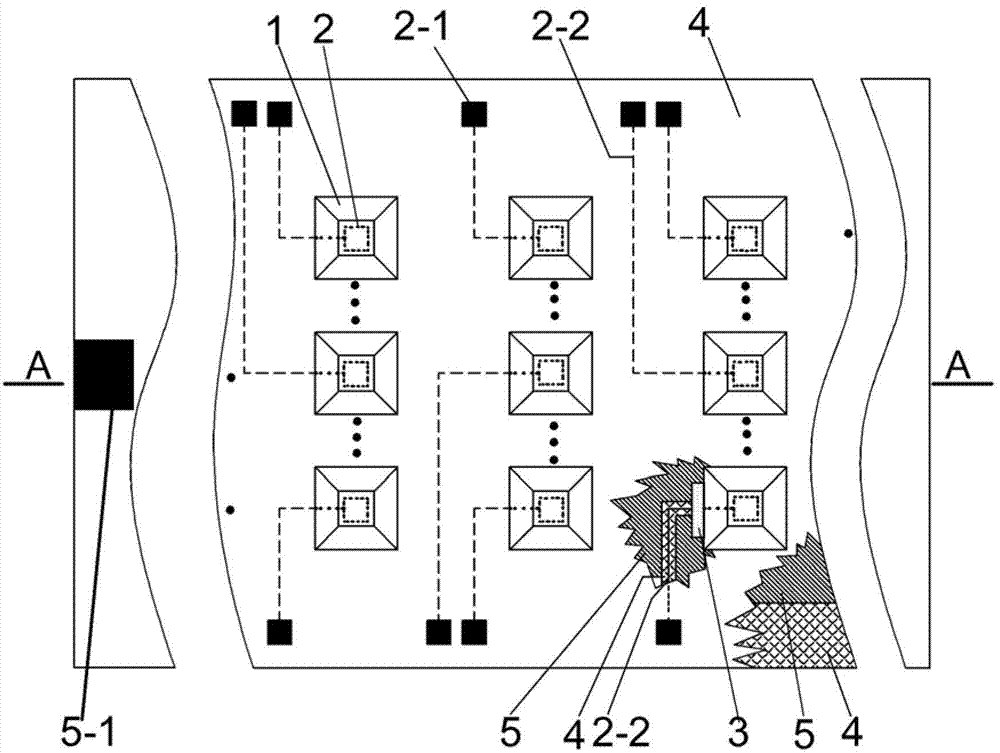

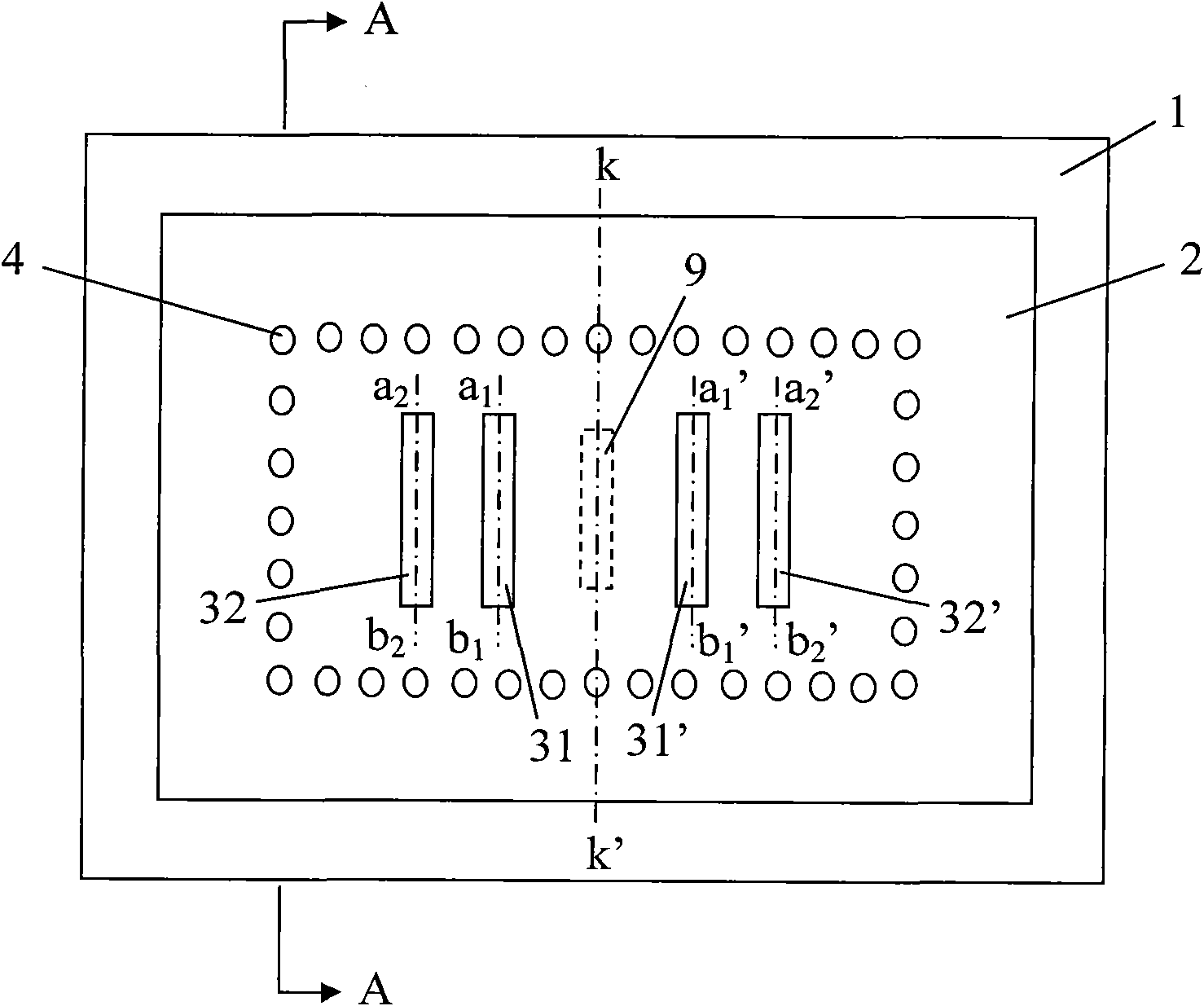

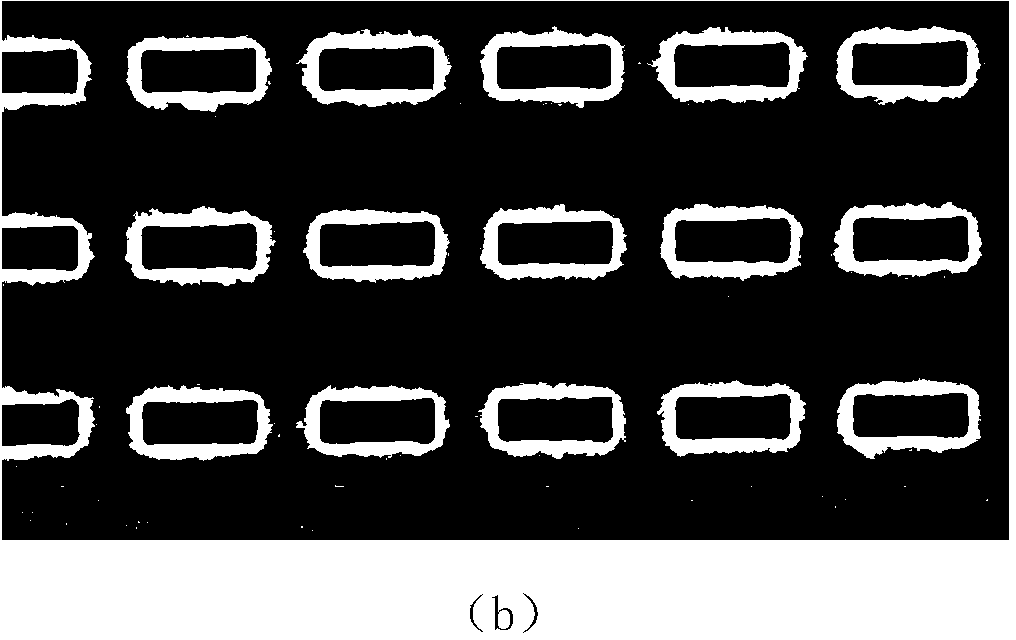

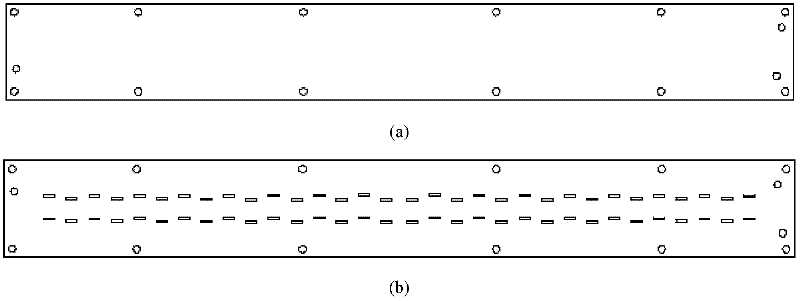

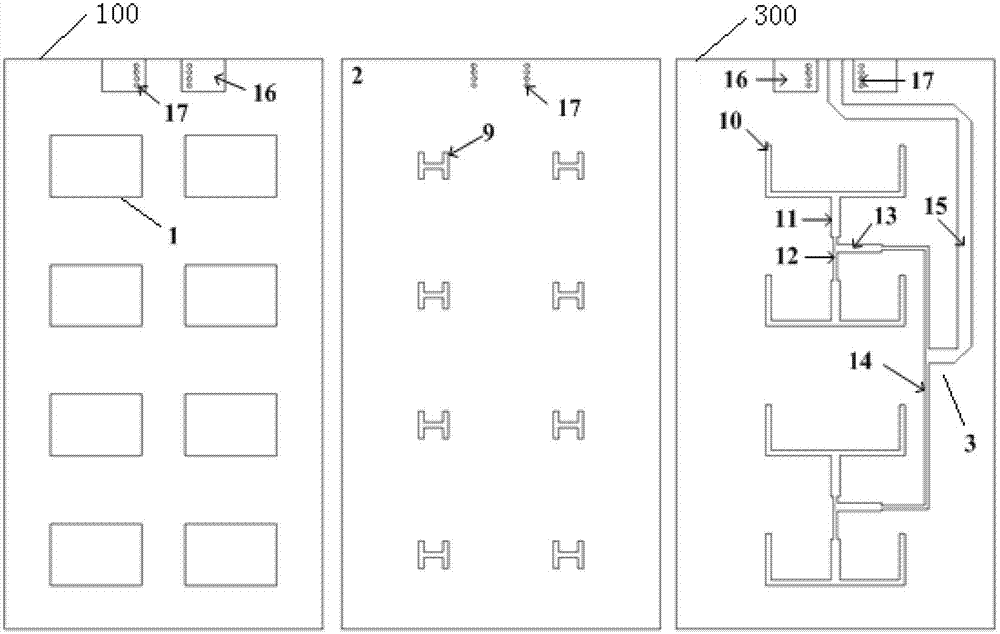

SIC technology-based four-element dual-polarization microstrip antenna array

InactiveCN108493626ABandwidthHigh bandwidthParticular array feeding systemsIndividually energised antenna arraysMicrostrip antenna arrayBroadband

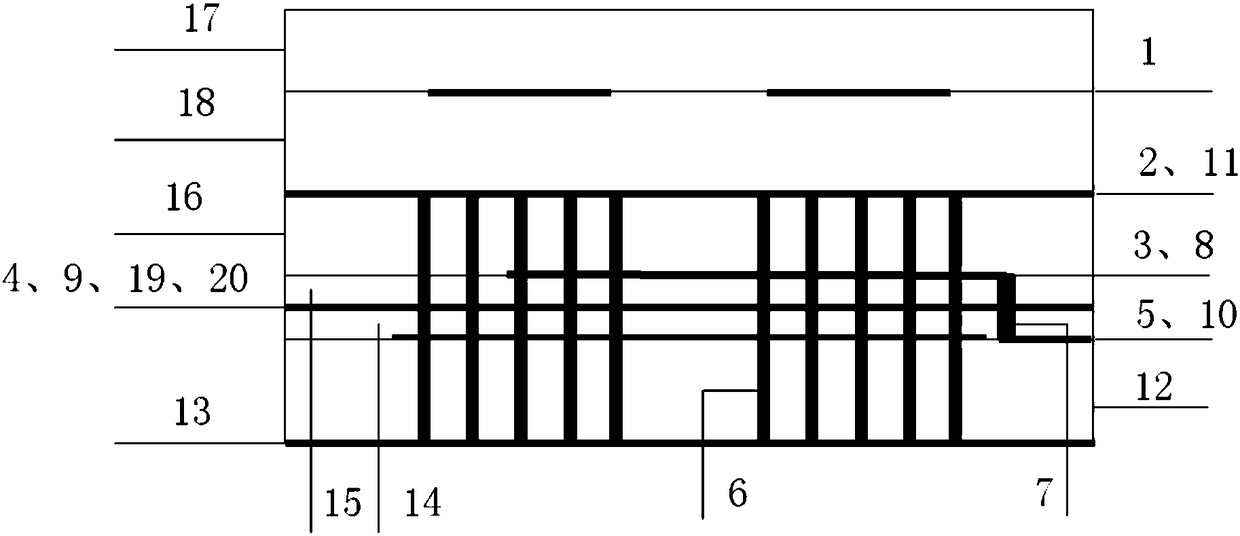

The invention relates to an SIC technology-based four-element dual-polarization microstrip antenna array, which comprises six layers of printed circuit boards and metal supports (6), wherein the lowersurface of a top layer of printed circuit board (17) is printed with rectangular parasitic patches (1); the upper surface of a third layer of printed circuit board (16) is printed with rectangular main patches (2) and a main patch layer reflection plate (11); the upper surface of a fourth layer of printed circuit board (15) is printed with a vertical-polarization feeder line (3) and a ring (8); the upper surface of a fifth layer of printed circuit board (14) is printed with a grounding plate (4); cross gaps (9), circular openings (19) and circular openings (20) are etched on the grounding plate (4); a horizontal-polarization feeder line (5) and a strip line (10) are printed on the lower surface of the fifth layer of printed circuit board (14); and the lower surface of the bottom layer ofprinted circuit board (12) is provided with an antenna bottom reflection plate (13). The SIC technology-based four-element dual-polarization microstrip antenna array has the advantages of wider bandwidth, higher port isolation and lower cross polarization level.

Owner:HARBIN ENG UNIV

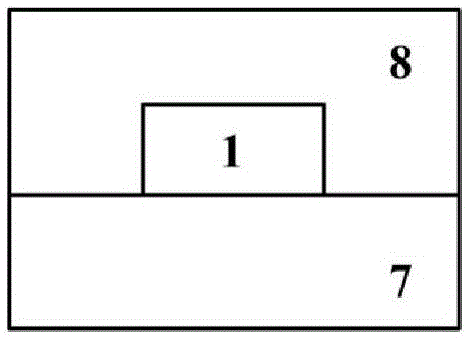

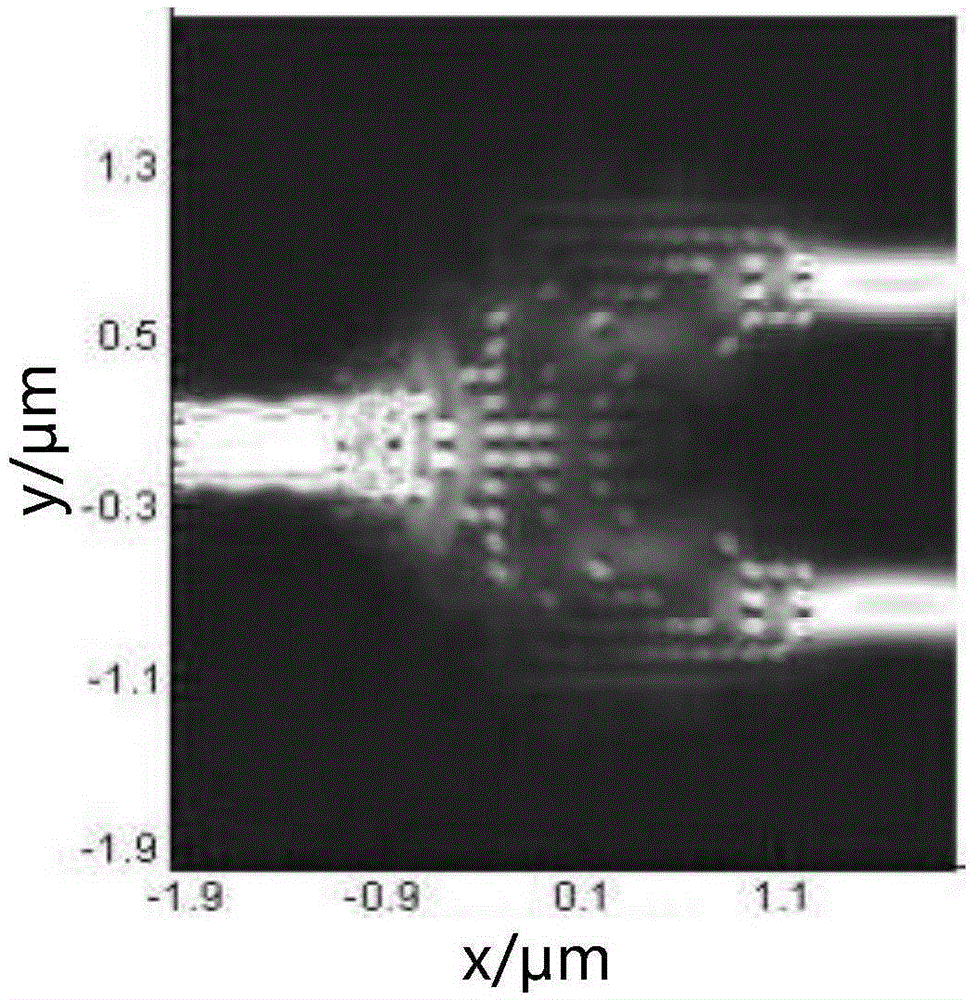

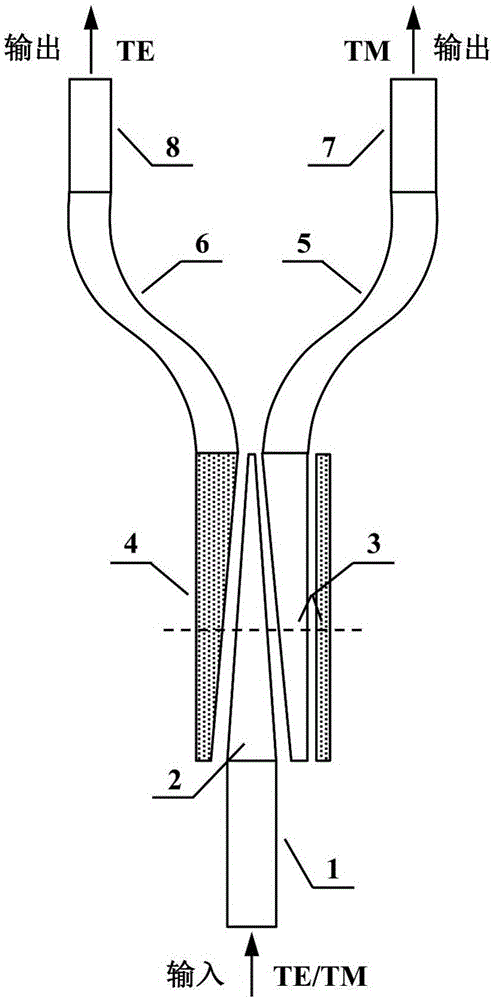

Silicon-based nanowire polarization beam splitter based on mode evolution principle

ActiveCN105093408APolarization beam splitting efficiency is highImprove working bandwidthOptical light guidesPlasmonic waveguideNanowire

The invention discloses a silicon-based nanowire polarization beam splitter based on the mode evolution principle, and can be used for the fields of integrated optics and silicon-based photonics. A vertical hybrid plasma waveguide (3) and a horizontal hybrid plasma waveguide (4) are respectively arranged at the two sides of a tapered transitional waveguide (2), and distance to the tapered transitional waveguide (2) is maintained to be consistent. An input waveguide (1) is connected at the lower end of the tapered transitional waveguide (2). A first S-shaped waveguide (5) is connected at the upper end of the vertical hybrid plasma waveguide (3). A first output waveguide (7) is connected at the upper end of the first S-shaped waveguide (5). A second S-shaped waveguide (6) is connected at the upper end of the horizontal hybrid plasma waveguide (4). A second output waveguide (8) is connected at the upper end of the second S-shaped waveguide (6). The device has advantages of being high in polarization beam splitting efficiency, low in loss, high in manufacturing tolerance and high in work bandwidth, and can also be used for constructing an on-chip polarization diversity scheme so as to realize polarization independent transmission.

Owner:SOUTHEAST UNIV

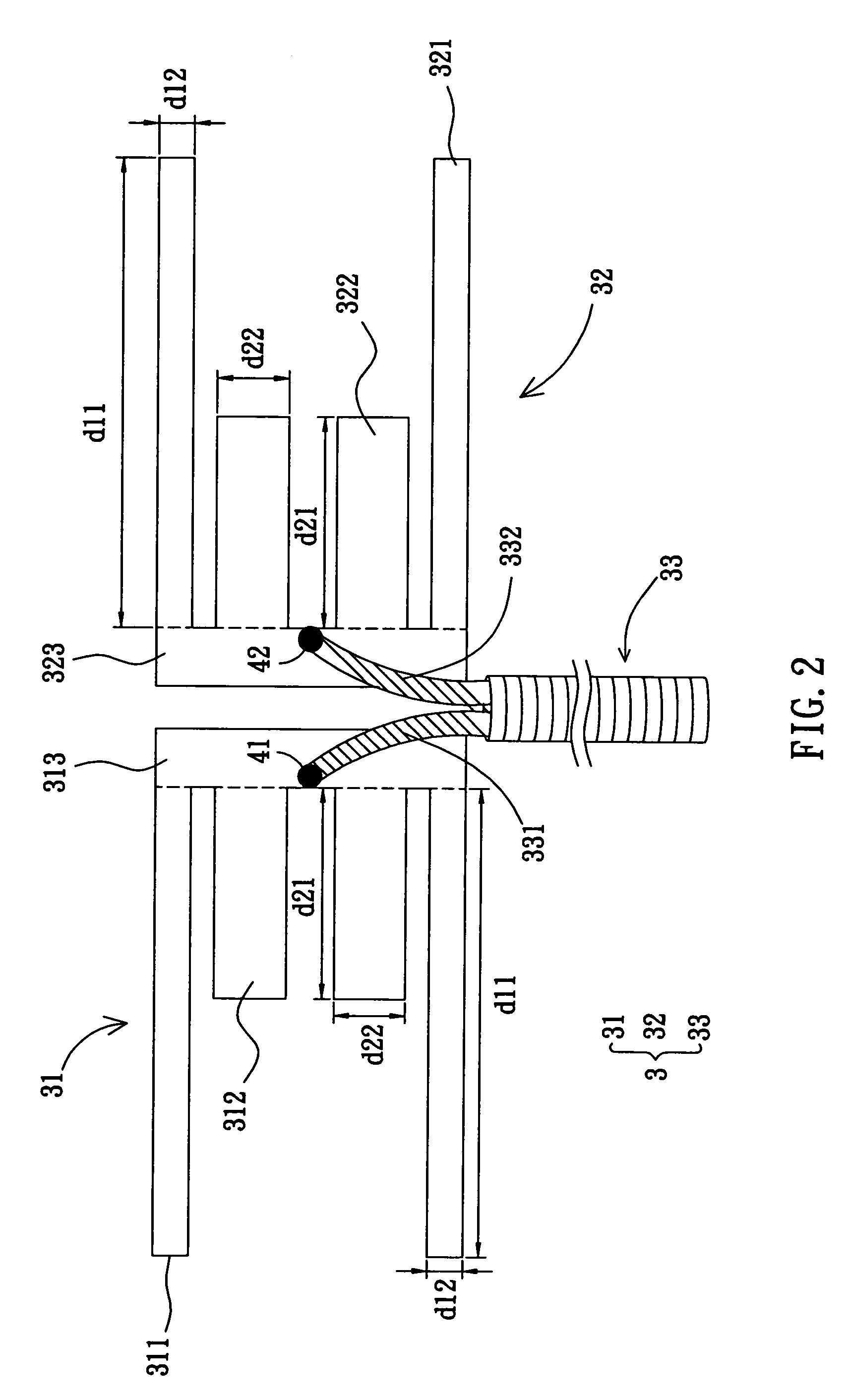

Dual band and broadband flat dipole antenna

InactiveUS20060022888A1Broaden usable rangeImprove working bandwidthSimultaneous aerial operationsIndividually energised antenna arraysPhysicsBroadband

A dual band and broadband flat dipole antenna comprises a first radiating body, a second radiating body, and a conductivity element. The first radiating body has two first frequency-radiating parts, two second frequency-radiating parts, and a first electrically connecting part. The first and second frequency-radiating parts are extended from a side of the first electrically connecting part. The second frequency-radiating parts are disposed between the first frequency-radiating parts. The second radiating body similar to the first radiating body has two first frequency-radiating parts, two second frequency-radiating parts, and a second electrically connecting part. The first and second frequency-radiating parts are extended from a side of the second electrically connecting part with the direction reversing to the extending direction of the first radiating body. The conductivity element has a conductivity body and a grounding conductor electrically connected with the first electrically connecting part and the second electrically connecting part, respectively.

Owner:ARCADYAN

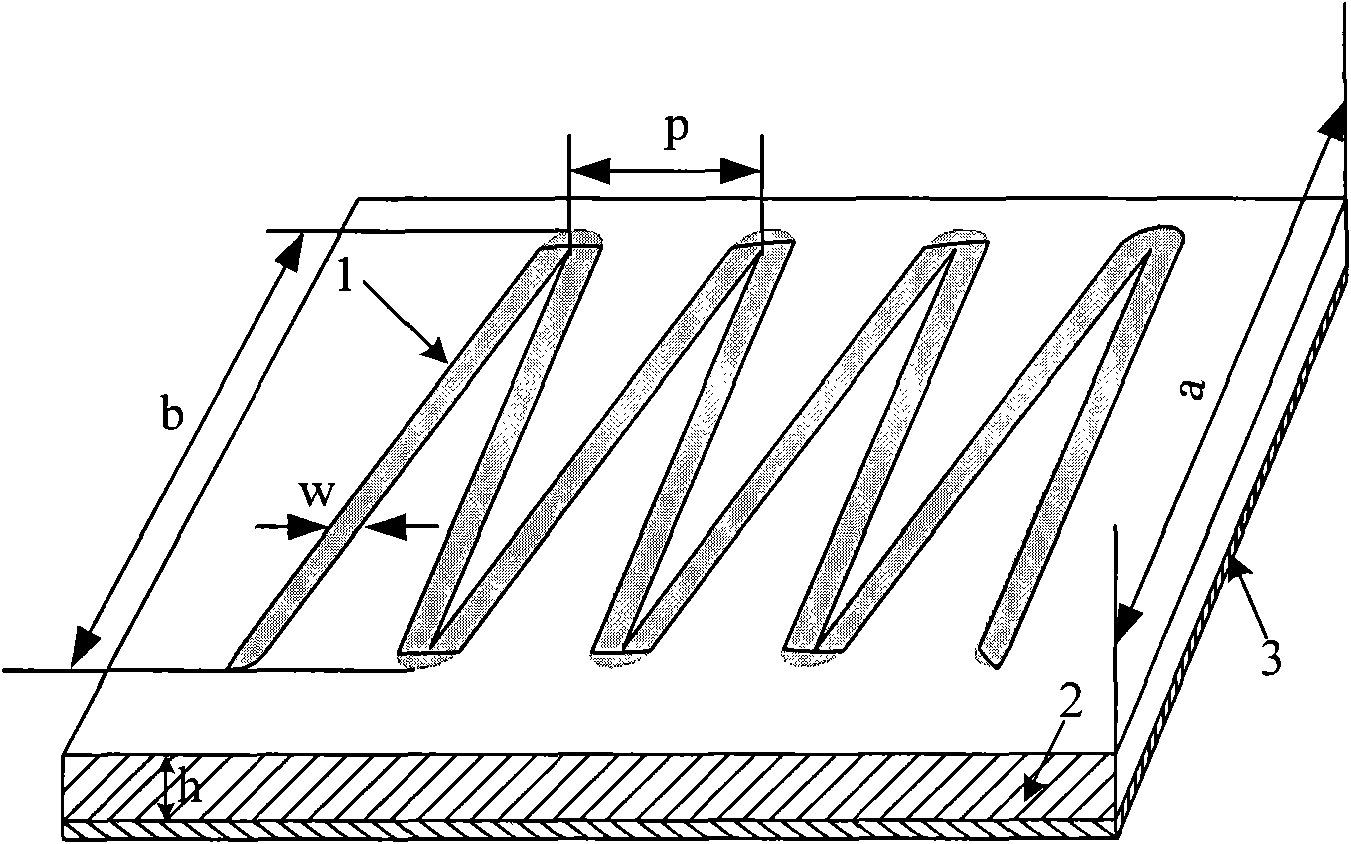

V-shaped micro-strip meander-line slow wave structure

InactiveCN101894724AImprove working bandwidthHigh coupling impedanceTransit-tube circuit elementsWave structureVacuum electronics

The invention discloses a V-shaped micro-strip meander-line slow wave structure, belongs to the technical field of microwave vacuum electronics, and relates to a traveling wave tube amplifier. The V-shaped micro-strip meander-line slow wave structure comprises a micro-strip transmission line structure consisting of a metal bottom plate (3), a dielectric layer (2) and a planar metal wire (1) and is characterized in that: the dielectric layer (2) is positioned between the metal bottom plate (3) and the planar metal wire (1); the planar metal wire (1) has a zigzag structure formed by connecting a plurality of sections of planar metal wires which have the same shape and dimension end to end; and the adjacent two sections of planar metal wires constitute a V shape or a reverse V shape, and the included angle 2theta of the V shape or reverse V shape is less than 180 degrees. The shape of the dielectric layer (2) can be the same as that of the metal bottom plate (3) or the planar metal wire (1). Compared with the conventional right-angle micro-strip meander-line slow wave structure, the V-shaped micro-strip meander-line slow wave structure has wider working band and higher coupling impedance and can further meet the requirements of an equipment system on the device in aspects of working bandwidth, output power, weight and volume.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

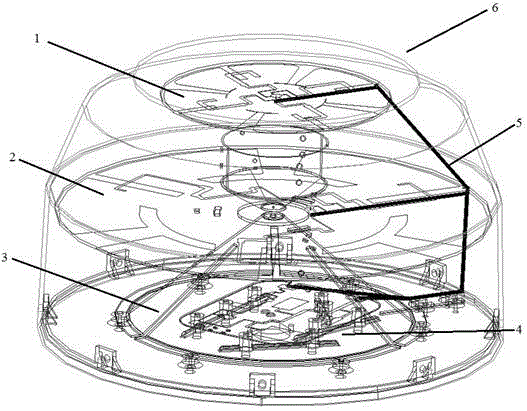

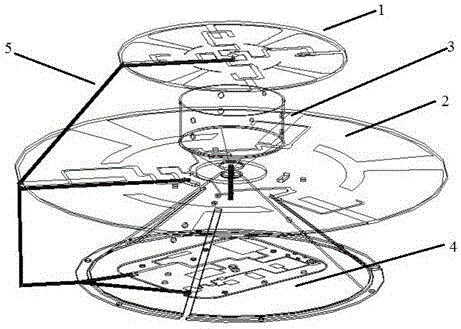

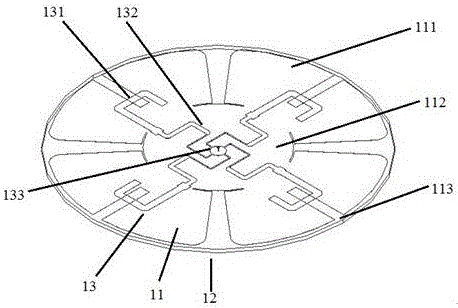

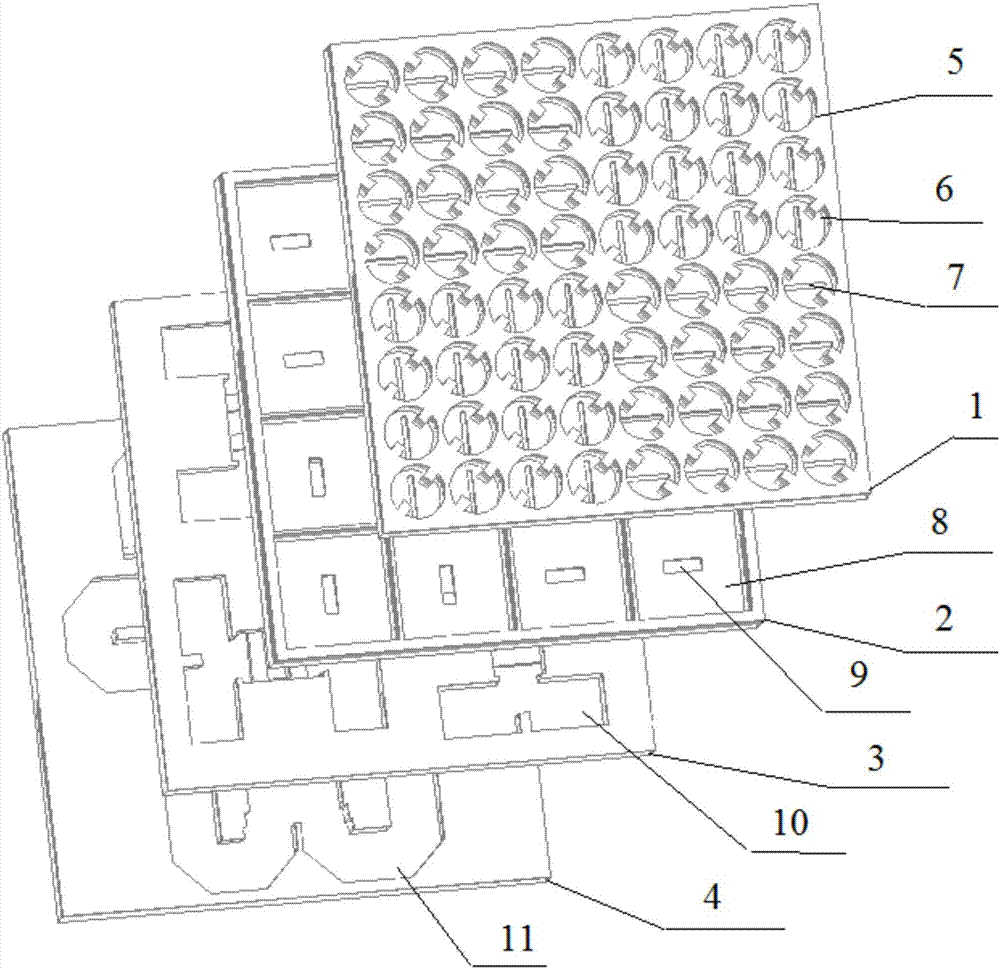

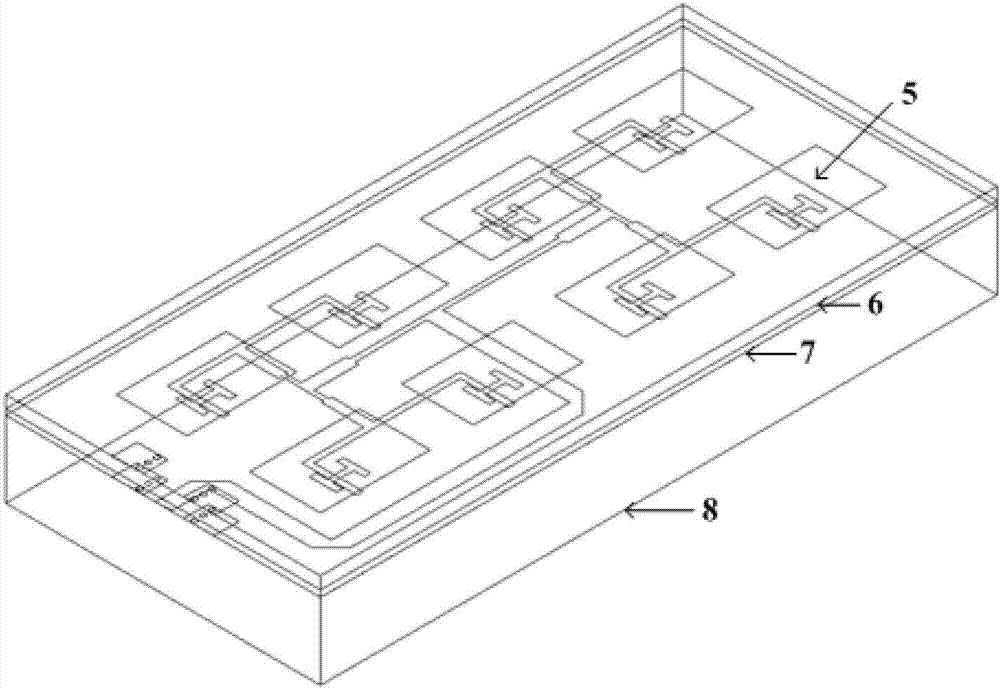

Broadband circularly-polarized waveguide antenna and antenna array thereof

ActiveCN106911003ALow axle ratioEasy to getParticular array feeding systemsIndividually energised antenna arraysCouplingBroadband

The invention discloses a broadband circularly-polarized waveguide antenna and an antenna array thereof. The antenna comprises a radiation layer, a cavity layer, a feed network layer and a circularly-polarized network layer, wherein the radiation layer, the cavity layer, the feed network layer and the circularly-polarized network layer are sequentially stacked to form a multilayer stacked structure. One side, backing on to the cavity layer, of the radiation layer is provided with 8*8 radiation units which are arranged in an array. Each radiation unit comprises a circular ridge opening waveguide with two symmetric ridges, and a first coupling feed straight gap which is disposed on a bottom wall of the circular ridge opening waveguide, wherein the two ridges are located at two opposite sides of the first coupling feed straight gap, and the vertical connection line of the two ridges and the first coupling feed straight gap form a 45-degree inclined angle. The 8*8 radiation units are divided into four radiation unit groups, and each radiation unit group comprises 4*4 radiation units which are arranged in an array. One radiation unit group is taken as a fixed point reference, and other three radiation unit groups sequentially rotate 90 degrees, 180 degrees and 270 degrees anticlockwise or clockwise.

Owner:CHINA ELECTRONIC TECH GRP CORP NO 38 RES INST

High gain broadband dielectric lens Vivaldi antenna

ActiveCN103326120ASmall reflection coefficientImproving Impedance MatchingRadiating elements structural formsResonant antennasAntenna gainVivaldi antenna

The invention relates to a high gain broadband dielectric lens Vivaldi antenna. The array antenna comprises a substrate, a radiation slot, a dielectric lens and a Chebychev tapered strip line feeder. According to the high gain broadband dielectric lens Vivaldi antenna, through changing the structural size of the dielectric lens, the fluctuation of antenna radiation impedance can be effectively improved so as to obtain better impedance matching, the transmission speed of an electromagnetic wave in the slot can be reduced according to the high dielectric constant of the lens, the current distribution on an antenna aperture is improved, thus a spherical wave is a nearly a plane wave, the antenna radiation efficiency is raised, and a higher antenna gain is obtained. According to a Chebychev tapered strip line, the impedance matching of the antenna can be improved further, and the working band is broadened. The array antenna in the invention has the characteristics of high gain and broad band and is suitable for a radiation unit of wideband array antennas of the field of mobile communication and a military radar.

Owner:THE 724TH RES INST OF CHINA SHIPBUILDING IND

Millimeter wave circularly polarized one-dimensional sum-difference vehicle-mounted communication antenna

InactiveCN102394376AGuaranteed working characteristicsHigh gainAntenna arraysAntenna adaptation in movable bodiesAdhesiveMetal sheet

The invention relates to a millimeter wave circularly polarized one-dimensional sum-difference vehicle-mounted communication antenna, belonging to the technical field of antennas. The antenna comprises a planar sum-difference network, coupled-fed slots, waveguide slots, metal walls, a microstrip slot surface, rigid support foam, a microstrip circularly polarized gate and a metal sheet, wherein a sum port and a difference port of the planar sum-difference network are ports connected with the outside; the waveguide slots are formed on the back of the planar sum-difference network; the waveguide slots and the planar sum-difference network are connected by the coupled-fed slots; the metal walls are positioned at the two sides of the waveguide slots; the planar sum-difference network, the coupled-fed slots, the waveguide slots and the metal walls integrally serve as an antenna back sheet; the metal sheet is positioned on the reverse side of the antenna back sheet and covers the planar sum-difference network; the microstrip slot surface is bonded with the waveguide slots by conductive adhesives; the rigid support foam is positioned between the metal walls, is fixed on the metal walls and covers the microstrip slot surface; and the microstrip circularly polarized gate is pasted on the upper surface of the rigid support foam. The antenna has the following beneficial effects: the defects of high processing cost, low yield, small work bandwidth and long processing period of metal waveguide slot arrays and the defect of low gain of microstrip patch array antennas are overcome.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

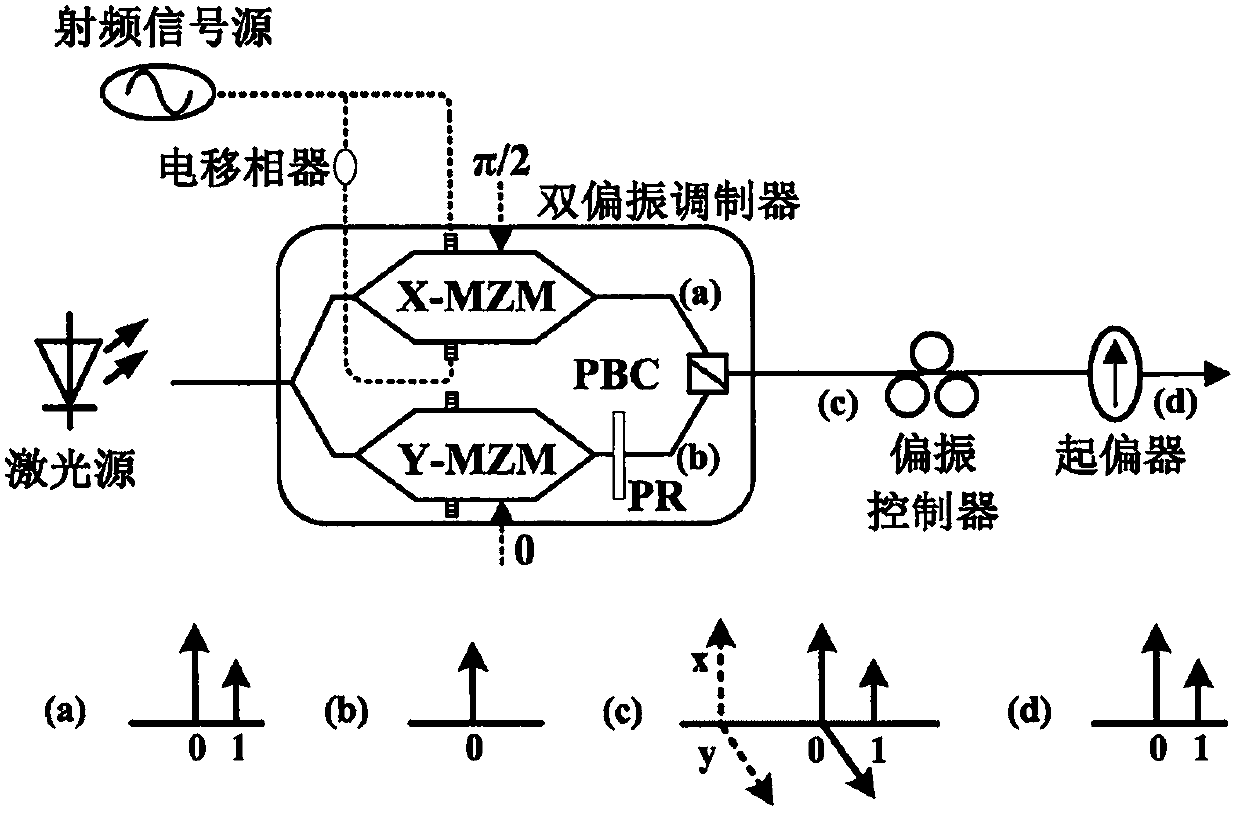

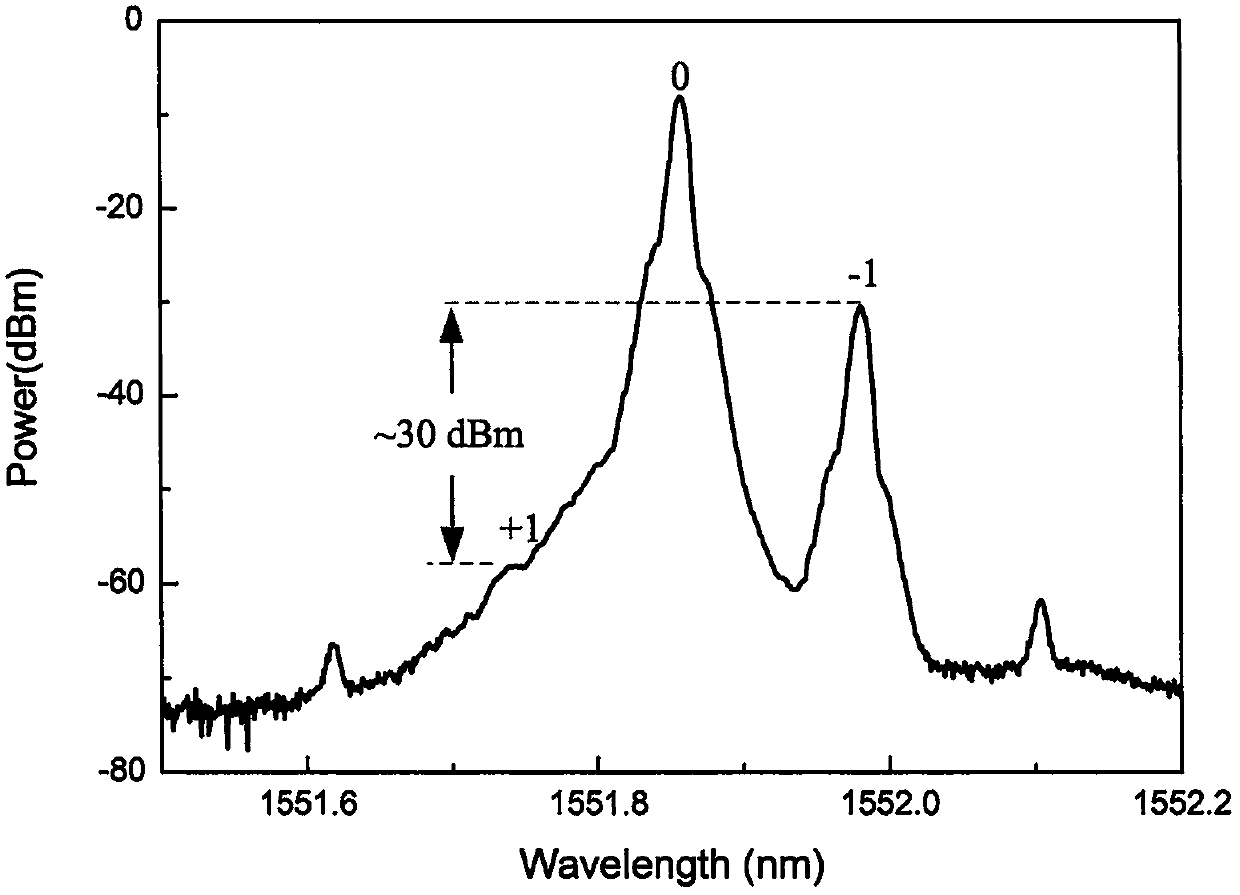

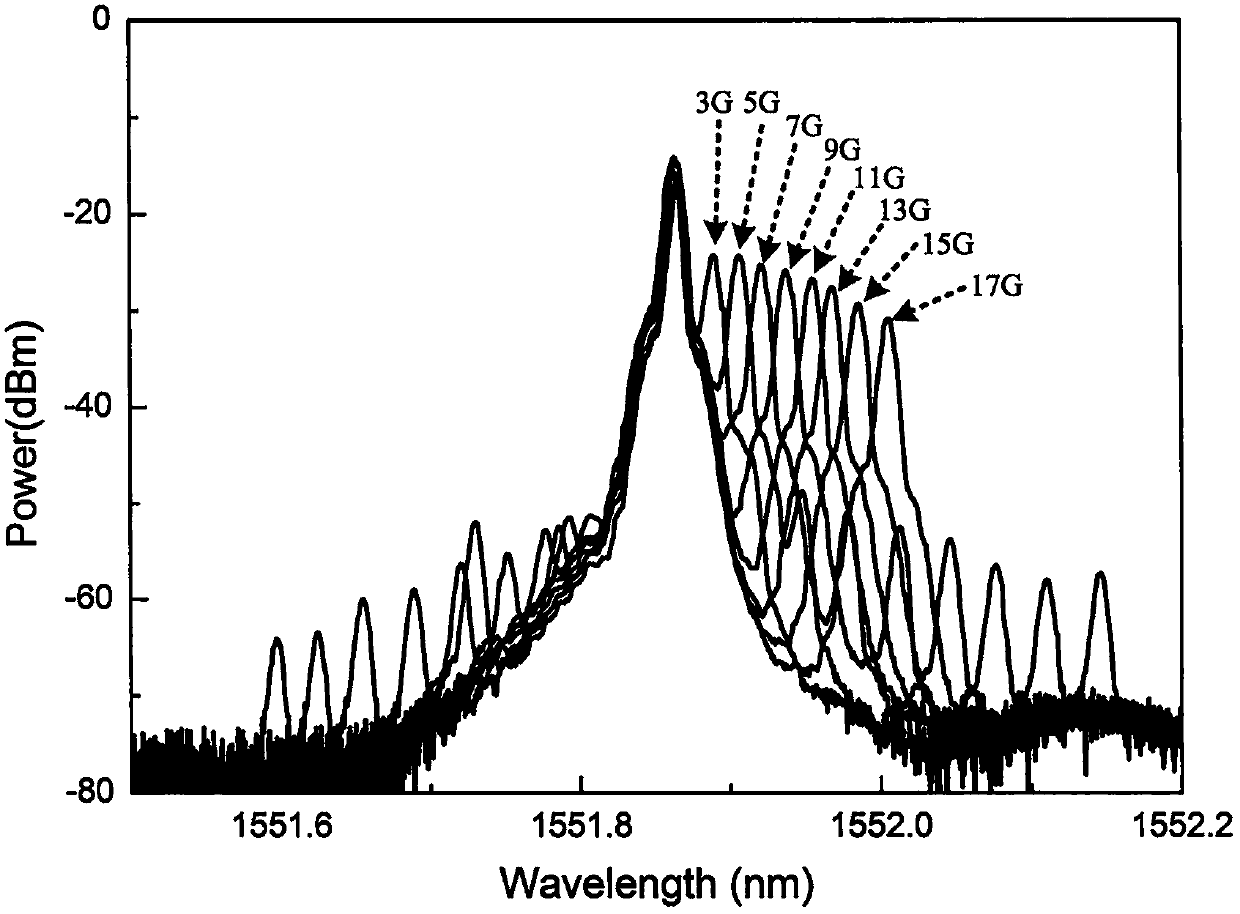

Optical single sideband modulation method capable of dynamically adjusting carrier-to-sideband ratio based on dual-polarization modulator

ActiveCN107947866AFlexible adjustment of carrier sideband ratioSimple structureElectromagnetic transmissionPolarization multiplexedCarrier signal

The invention discloses an optical single sideband modulation method capable of dynamically adjusting a carrier-to-sideband ratio based on a dual-polarization modulator, and relates to the technical field of optical communication and microwave. The method is as shown in the attached pictures, and relates to a laser source, a radio frequency signal source, a power phaser, a dual-polarization modulator, a polarization controller and a polarizer. By adoption of the method, a polarization multiplexing optical single sideband modulation signal is acquired by the dual-polarization modulator; and, the carrier-to-sideband ratio of the optical single sideband modulation signal can be flexibly adjusted by adjusting the polarization controller. The single sideband signal generated by the method can be applied to a radio frequency communication system over fiber; the problem that a periodic power fading is caused by the fiber dispersion when the signal is transmitted in a long distance is solved;and the transmission performance of the system is greatly improved by selecting the proper carrier-to-sideband ratio. Moreover, the method is simple in structure, has no selectivity for the wave length of the optical carrier, and has tenability for the broadband.

Owner:XIDIAN UNIV

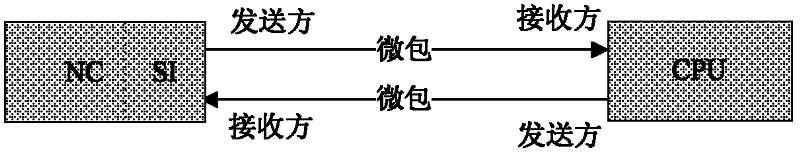

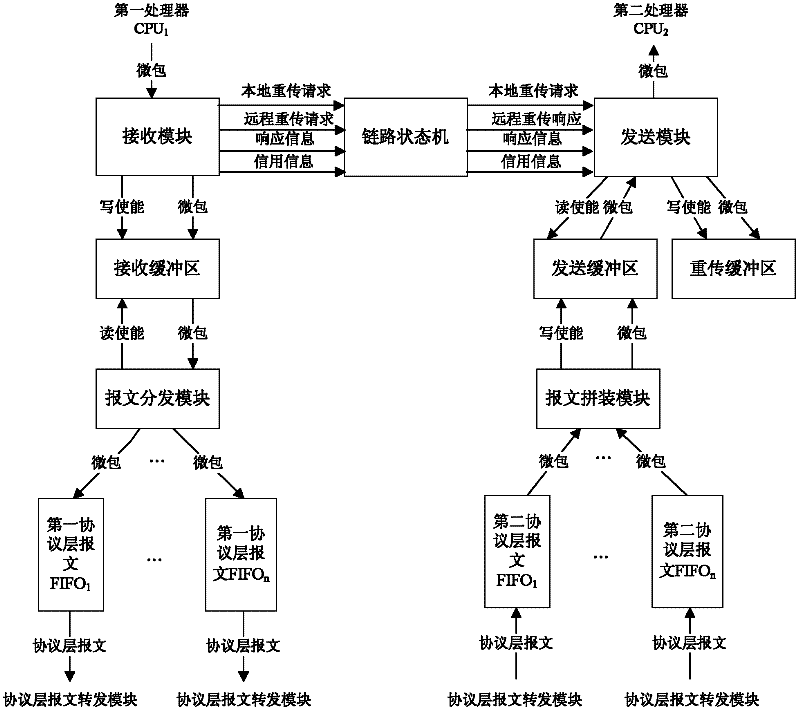

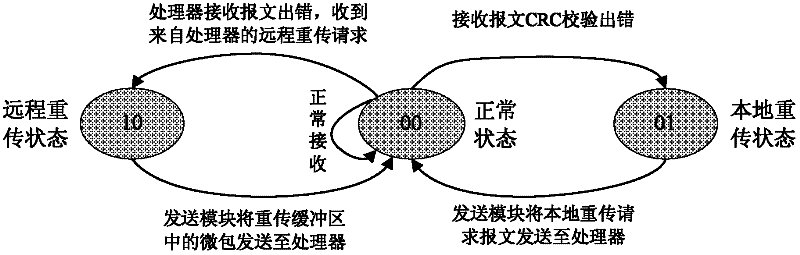

Multi-micropacket parallel processing structure

InactiveCN102394732AProcessing speedThe data transfer rate is not bound by the link layerError prevention/detection by using return channelData switching networksPhysical layerInterprocessor communication

The invention discloses a multi-micropacket parallel processing structure, which aims to solve the problem that in a single-micropacket processing structure, the bandwidth of a physical layer and a link layer is not matched, so that the speed of the processing of the chip of a node controller to the communication among processors is reduced. The multi-micropacket parallel processing structure comprises an interface conversion module, a receiving module, a receiving buffer area, a message distribution module, a first protocol layer message FIFO (First In First Out), a second protocol layer message FIFO, a link state machine, a message assembly module, a send buffer area, a retransmission buffer area and a sending module, wherein the interface conversion module works under a physical layer clock domain, other modules work under a link layer clock domain, the interface conversion module comprises asynchronous receiving FIFO and asynchronous transmission FIFO, and data paths in the receiving module and the sending module are multi-path parallel data paths aiming at multi micropackets, and can process the multi micropackets in parallel. According to the invention, the bandwidth of the physical layer / the link layer is matched, so that the speed of the processing of the chip of the node controller to the communication among the processors is improved.

Owner:NAT UNIV OF DEFENSE TECH

Broadband directional microstrip patch antenna

InactiveCN102738572AEasy to processEase of mass productionRadiating elements structural formsPolarised antenna unit combinationsMicrostrip patch antennaPatch array

The invention discloses a broadband directional microstrip patch antenna which is sequentially provided with a first medium layer, a microstrip feeder network arranged on the first medium layer, a second medium layer, a slit grounding surface arranged on the second medium layer, a third medium layer and a radiation patch array arranged on the third medium layer from bottom to top. The broadband directional microstrip patch antenna is simple to process and easy to assemble.

Owner:SOUTHEAST UNIV

Multi-beam integrated waveguide antenna use for on-board anti-collision radar

ActiveCN105428800AReduce volumeReduce weightRadiating elements structural formsAntennas earthing switches associationRadar antennasMicrowave

The present invention provides a multi-beam integrated waveguide antenna, belongs to the field of radar antennas, and aims to solve the problems that an anti-collision radar in an existing phased array system is expensive, has high difficulty in extracting a target algorithm in a complex environment, is complex in system hardware and the like. The multi-beam integrated waveguide antenna has the technical key points that the antenna is formed by integrating a substrate integrated waveguide antenna array at a first layer, (2n-2) layers of strip-shaped lines and a microwave circuit at a bottom layer; and the microwave circuit mainly comprises X one-in-(2n-1) unequal power dividers, and (2n-1) one-in-X unequal power dividers, wherein n+1 is the number of formed beams, n is greater than or equal to 2, and X is the number of units of an array antenna. The multi-beam integrated waveguide antenna has the effects that array amplitude and phase distribution are implemented by means of the power dividers and the shift-phase micro-strip lines so as to implement multiple beams, and on the basis, the number of the beams can be extended.

Owner:DALIAN ROILAND SCI & TECH CO LTD

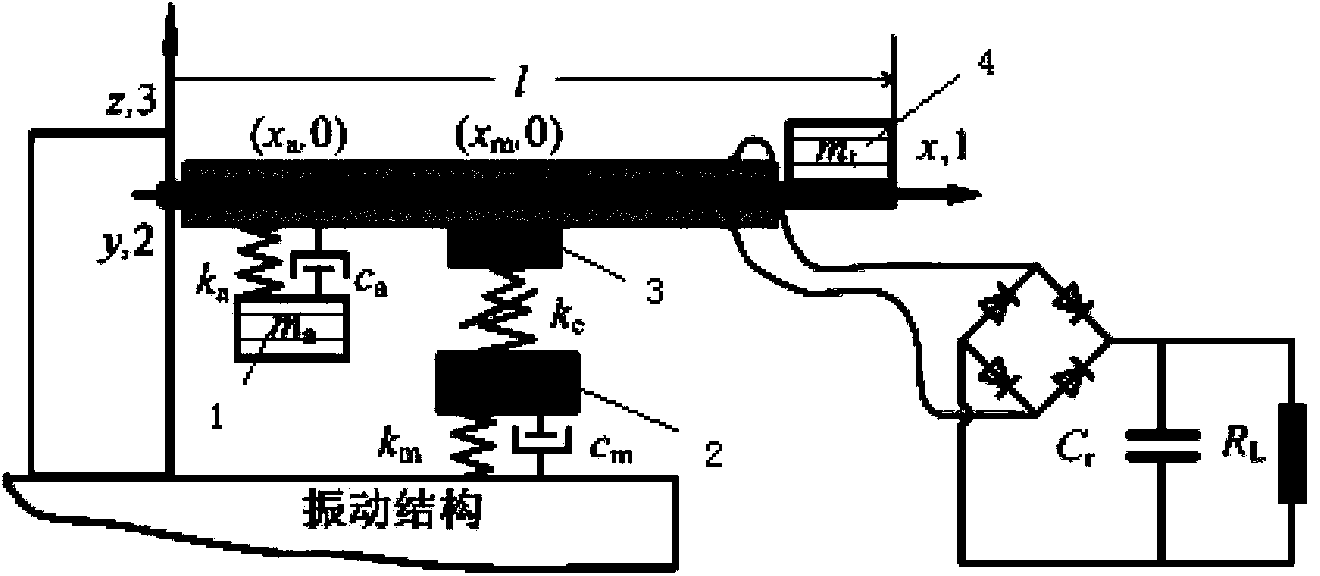

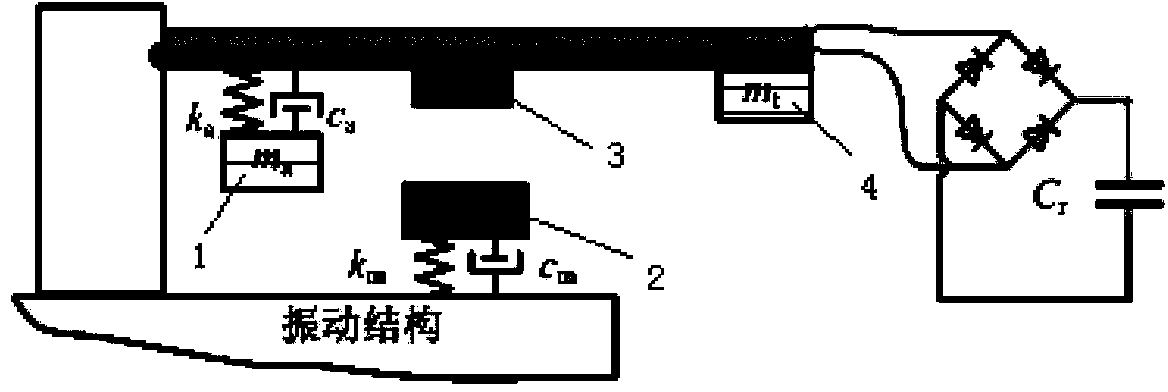

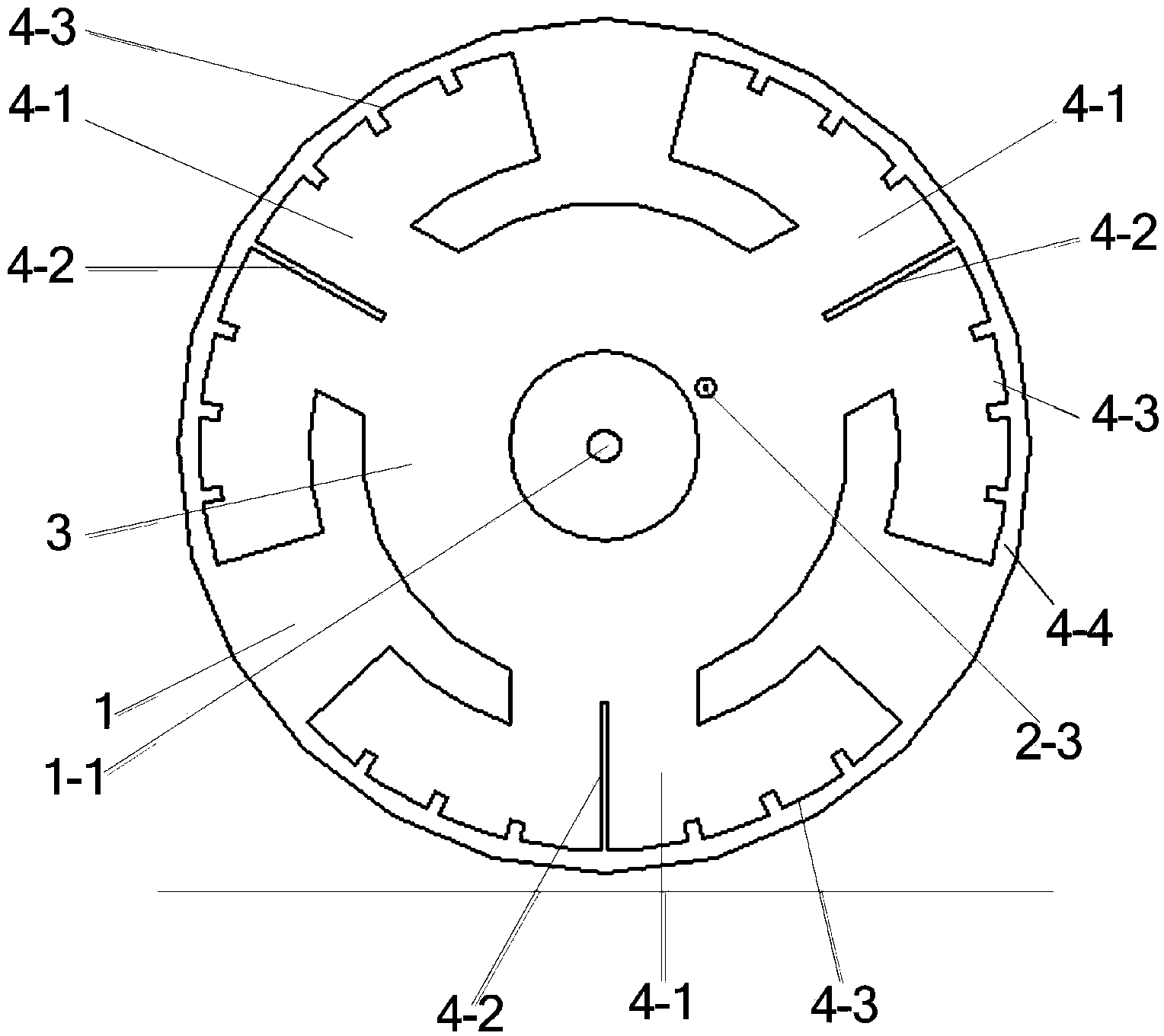

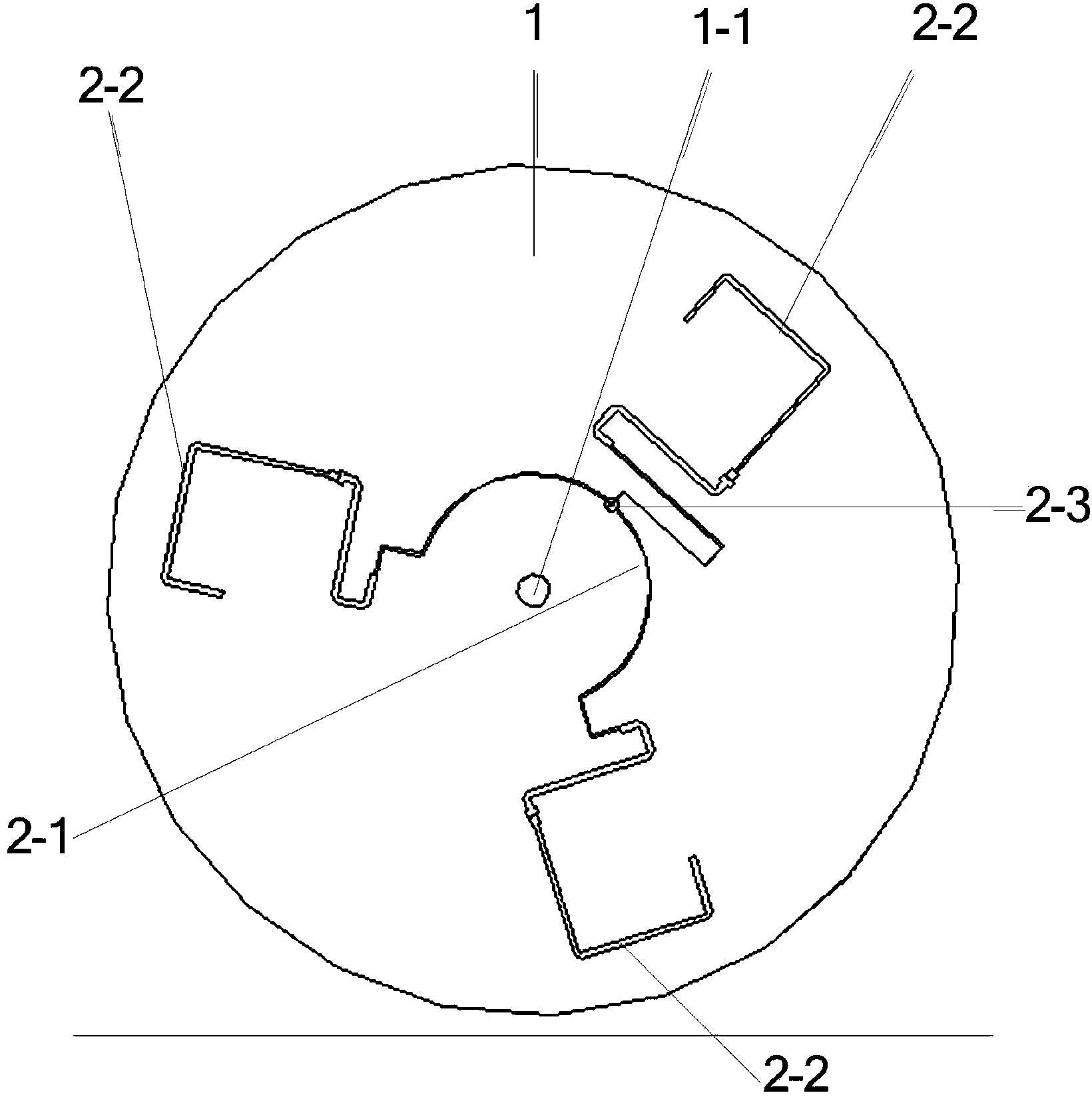

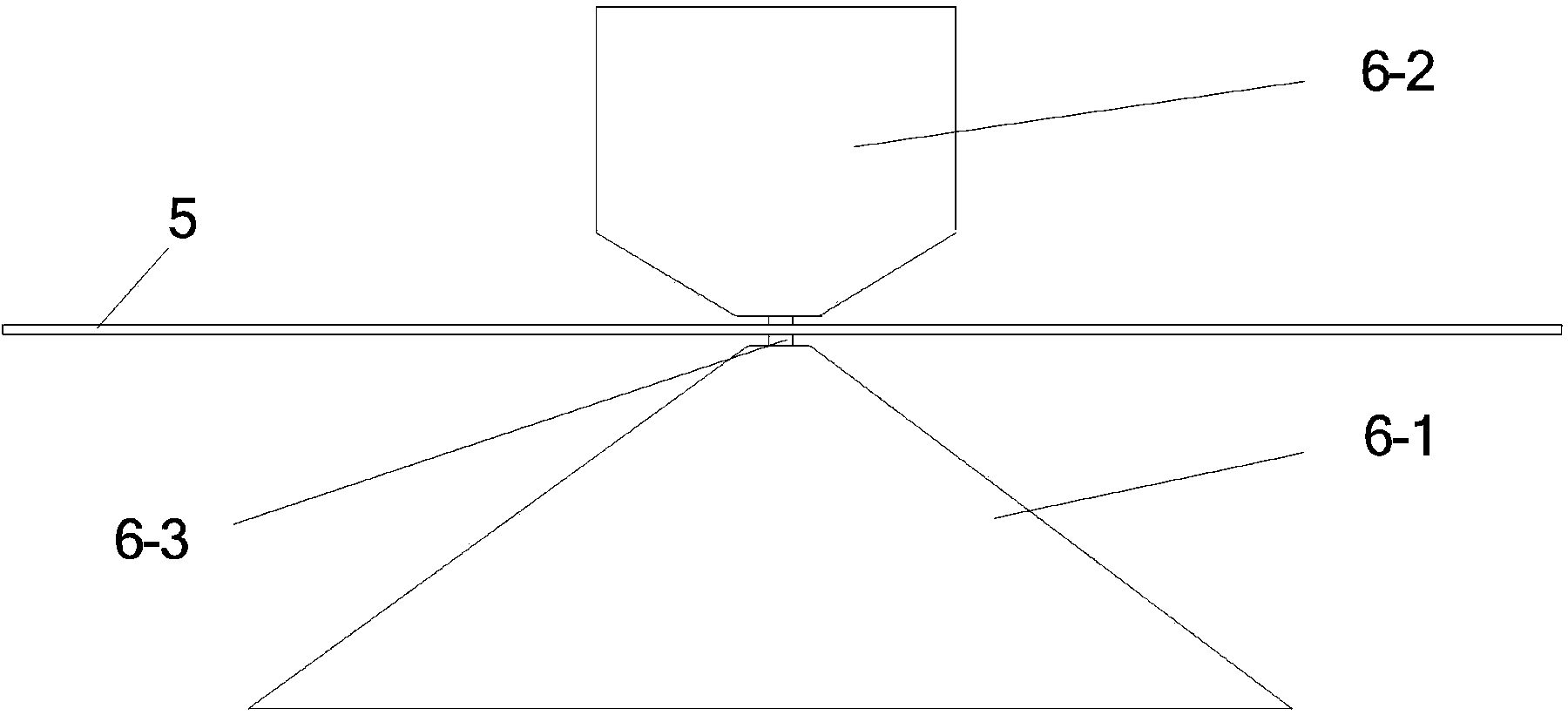

Piezoelectric energy collector based on linear resonator and nonlinear vibration exciter

InactiveCN103414379AIncrease the number ofWorking frequency bandwidthPiezoelectric/electrostriction/magnetostriction machinesFrequency bandResonator

The invention discloses a piezoelectric energy collector based on a linear resonator and a nonlinear vibration exciter. The piezoelectric energy collector comprises an energy collecting structure and an energy collecting circuit, wherein the energy collecting structure comprises a piezoelectric cantilever beam, the linear resonator and the nonlinear vibration exciter. According to the piezoelectric energy collector, the linear resonator is further arranged on the piezoelectric cantilever beam, so that two resonance peaks which are close to each other are obtained, and a reverse resonance peak of the energy collector can be further moved outside of the two resonance peaks through designing parameters such as the mass ratio, the frequency ratio and the position ratio of the linear resonator and the piezoelectric cantilever beam, so that a wider working band can be obtained; the arrangement of the nonlinear vibration exciter can increase the number of the resonance peaks of a system, and the working band of the system can be further expanded through designing system parameters, or the performance at a valley between the two resonance peaks can be improved.

Owner:SHANGHAI JIAO TONG UNIV

Common-grounded edge rippled horizontal polarization broadband omnidirectional antenna array and adjusting method thereof

ActiveCN104319475AEasy to realize integrated designRealize integrated designAntenna arraysRadiating elements structural formsOmnidirectional antennaAntenna radiation patterns

Provided are a common-grounded edge rippled horizontal polarization broadband omnidirectional antenna array and an adjusting method of the common-grounded edge rippled horizontal polarization broadband omnidirectional antenna array. The antenna array comprises a circular dielectric slab, a power divider feed network, a public circular ring metal ground and an arc-shaped printed dipole array, wherein the circular dielectric slab is provided with a hole in the center, the power divider feed network is arranged on one surface of the circular dielectric slab and comprises a one-to-n eccentric equiamplitude same-phase power divider network and n feed microstrip lines, the public circular ring metal ground is arranged on the other surface of the circular dielectric slab and is concentric with the circular through hole, the arc-shaped printed dipole array is arranged on the other surface of the circular dielectric slab and composed of n arc-shaped printed dipoles which are evenly distributed in a circular ring shape, the middle of each arc-shaped printed dipole is connected with the public circular ring metal ground, and slits are formed in each arc-shaped printed dipole. According to the common-grounded edge rippled horizontal polarization broadband omnidirectional antenna array and the adjusting method for the common-grounded edge rippled horizontal polarization broadband omnidirectional antenna array, grooves are formed in the outer edge of each arc-shaped printed dipole, the outer edge of each arc-shaped printed dipole is made to be in a concave-convex rippled shape, and the out-of-roundness of radiation patterns of antennas is relieved.

Owner:SUZHOU TIANYE MECHANICAL IND

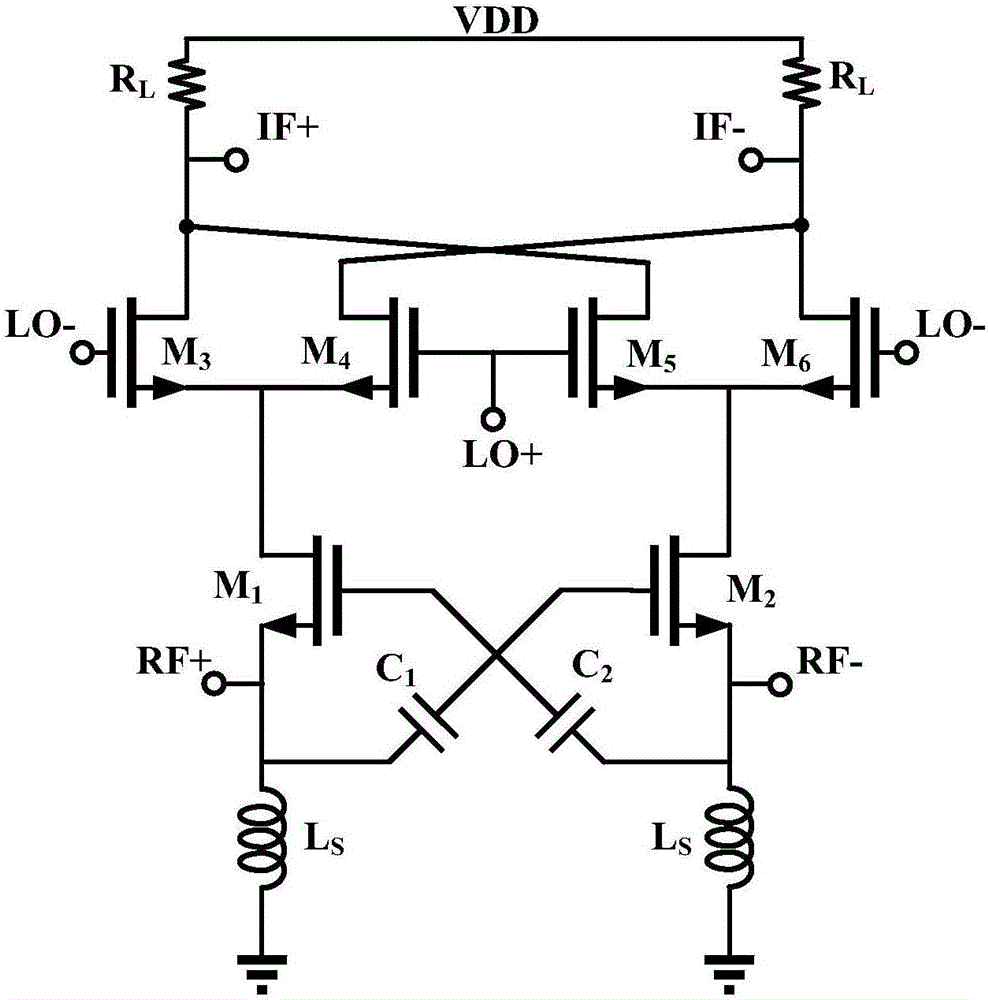

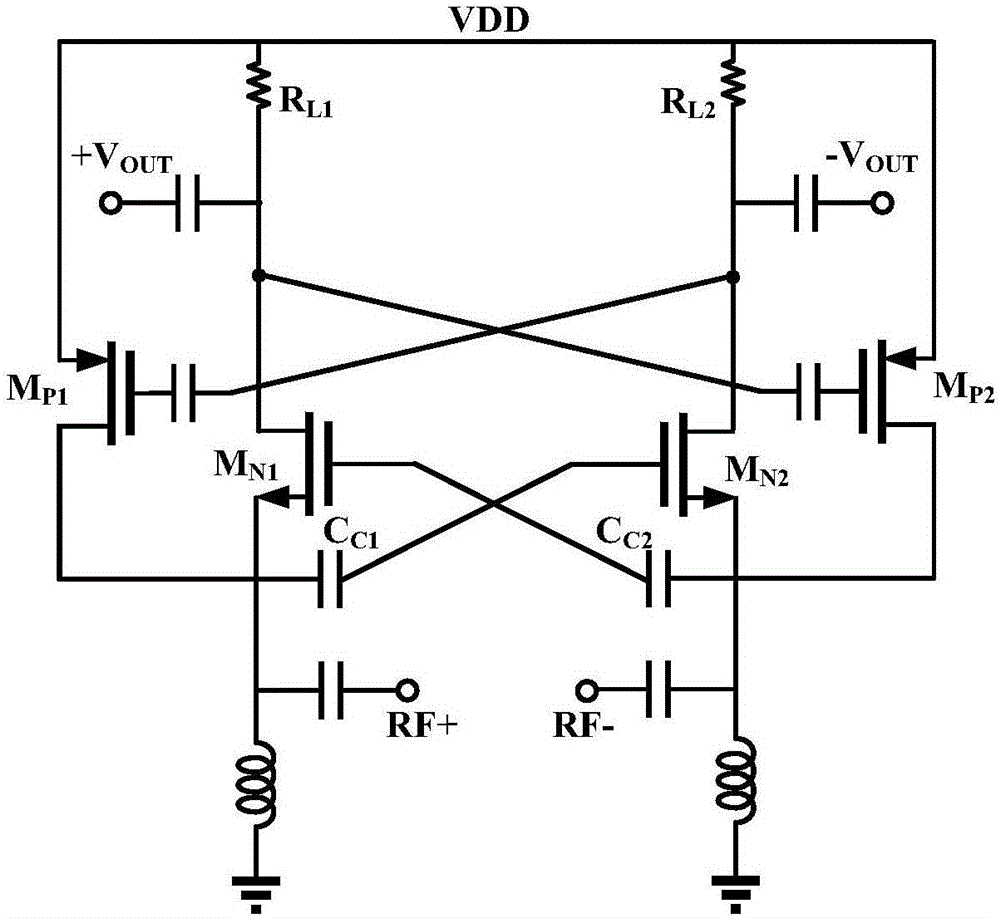

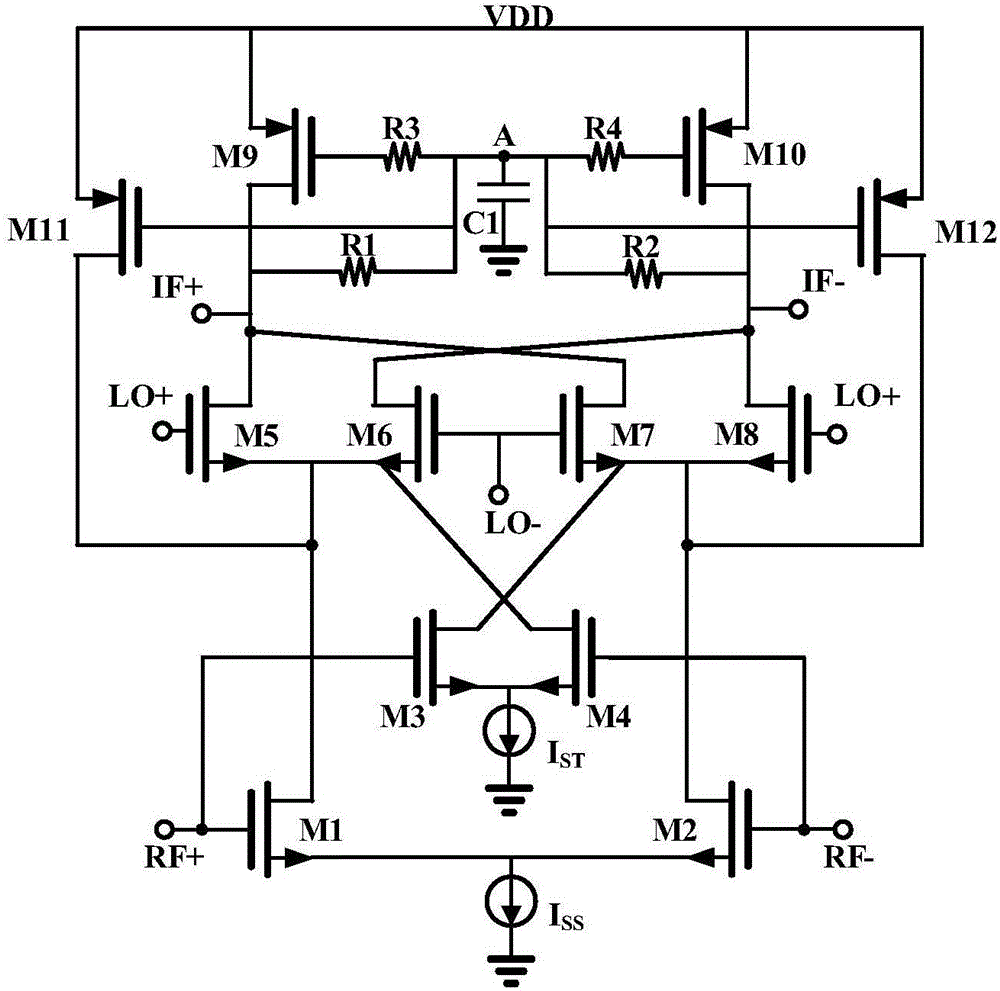

Low-power-consumption broadband radio frequency mixer adopting multichannel feedback transconductance enhancement and common mode feedback active load

ActiveCN106849876AReduce power consumptionImprove power performanceModulation transference balanced arrangementsCapacitanceLinearity

The invention discloses a low-power-consumption broadband radio frequency mixer adopting multichannel feedback transconductance enhancement and common mode feedback active load, in order to solve the problems of relatively narrow working band and relatively high noise coefficient of the existing mixer, and further improve the linearity and the power consumption performance. The mixer comprises a signal input stage (1) composed of resistors and capacitors, a transconductance stage (2) composed of a multichannel feedback dual transconductance enhancement structure, a switch stage (3) composed of symmetrical switch tubes and a load stage (4) composed of the common mode feedback active load. According to the low-power-consumption broadband radio frequency mixer disclosed by the invention, multichannel feedback is imported to the transconductance stage of the mixer to improve the conversion gain of the mixer, realize the compromise of the mixer gain and the input match, and expand the working band of the mixer. The multichannel feedback used in the low-power-consumption broadband radio frequency mixer disclosed by the invention also realizes noise cancelation and optimizes the noise performance of the mixer. According to the low-power-consumption broadband radio frequency mixer disclosed by the invention, the common mode feedback active load is used in the load stage to optimize the linearity performance of the mixer. The low-power-consumption broadband radio frequency mixer disclosed by the invention has the advantages of simple structure, easy realization and small occupation area.

Owner:UNIV OF SCI & TECH OF CHINA