Multi-micropacket parallel processing structure

A parallel processing, micro-packet technology, used in error prevention/detection using return channels, digital transmission systems, electrical components, etc. Problems such as the processing speed of the point controller chip and the increase in data transmission delay

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

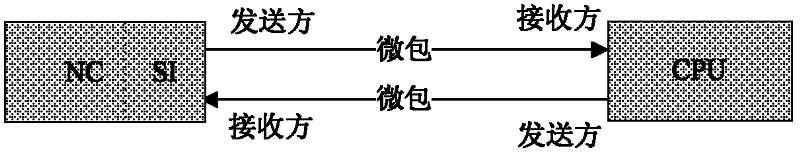

[0045] figure 1 It is a schematic diagram of the direct connection communication between the node control chip NC and the processor CPU in the background technology.

[0046] The node control chip is directly connected to the processor, and the processor interface access control component SI in the node control chip is responsible for reliable data transmission between the processor and the node control chip, and performs flow control and error detection / correction based on the credit mechanism . The SI includes a receiving module and a sending module. The sending module is responsible for sending messages to the processor, and the receiving module receives messages from the processor. Therefore, message transmission is divided into sender and receiver, and the receiver and sender belong to different ports: when SI sends a message to the processor, the sender is SI, and the receiver is the processor; when SI receives a message from the processor In the case of a message, the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More