Patents

Literature

34 results about "HyperTransport" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

HyperTransport (HT), formerly known as Lightning Data Transport (LDT), is a technology for interconnection of computer processors. It is a bidirectional serial/parallel high-bandwidth, low-latency point-to-point link that was introduced on April 2, 2001. The HyperTransport Consortium is in charge of promoting and developing HyperTransport technology.

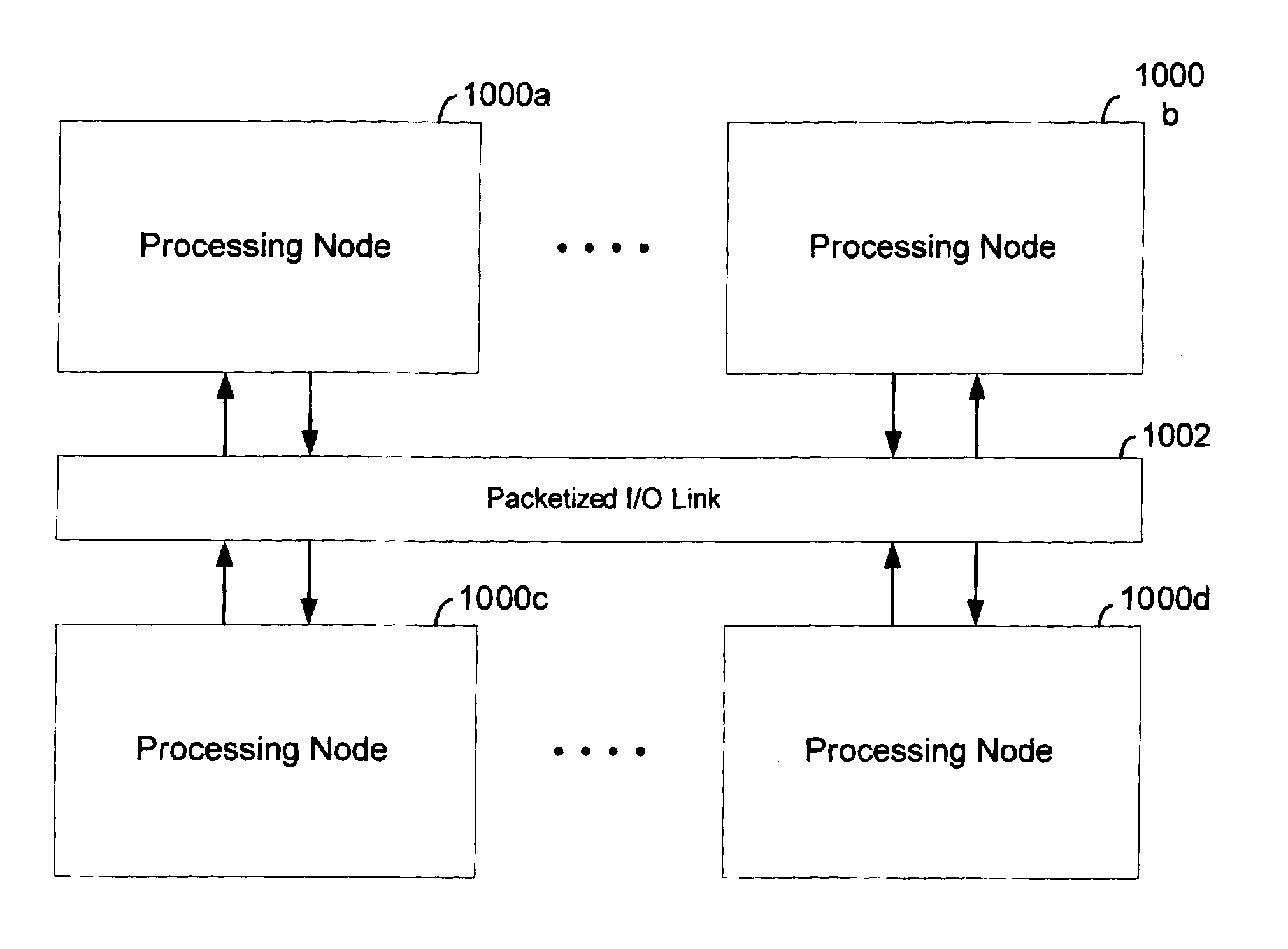

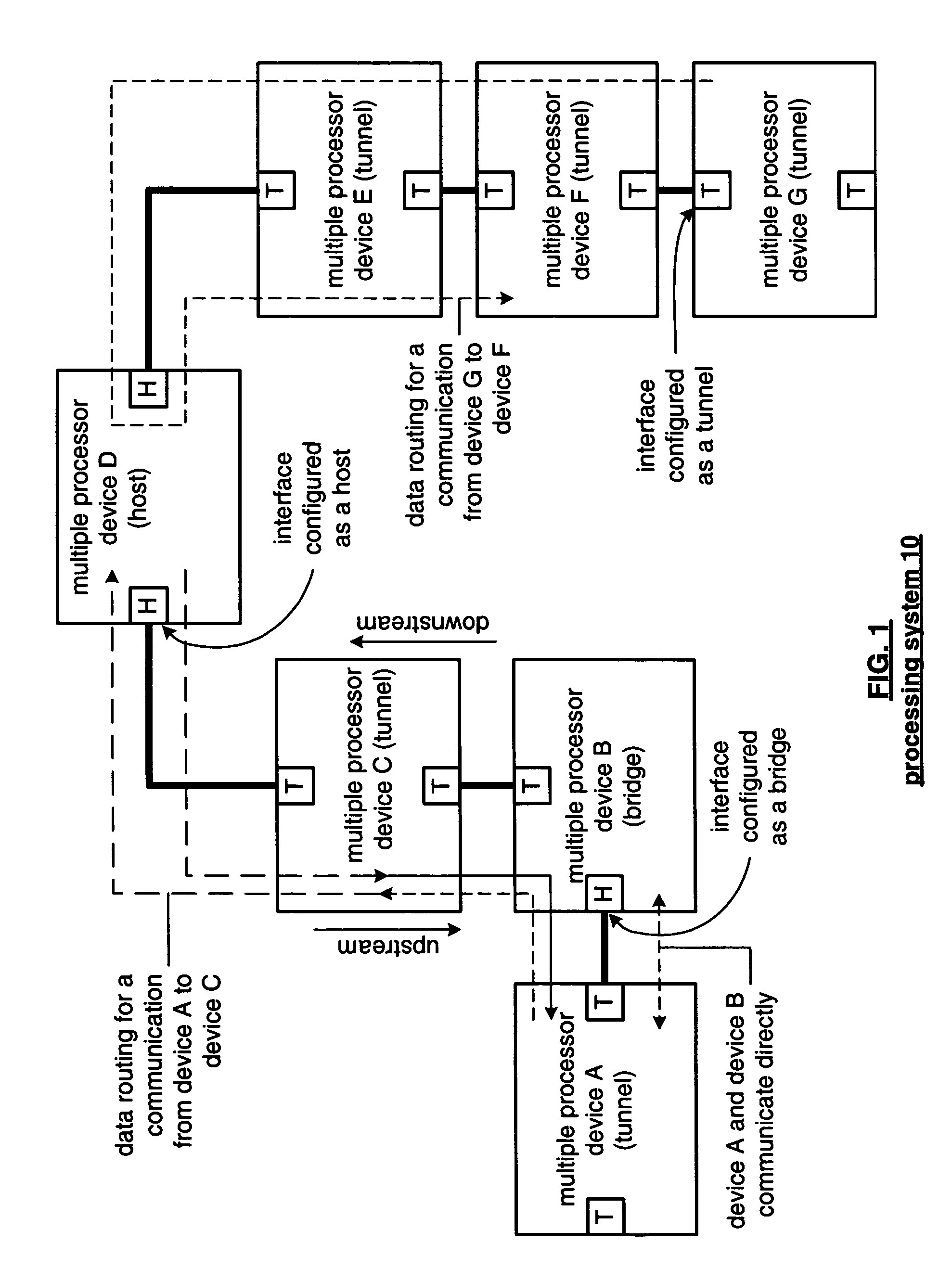

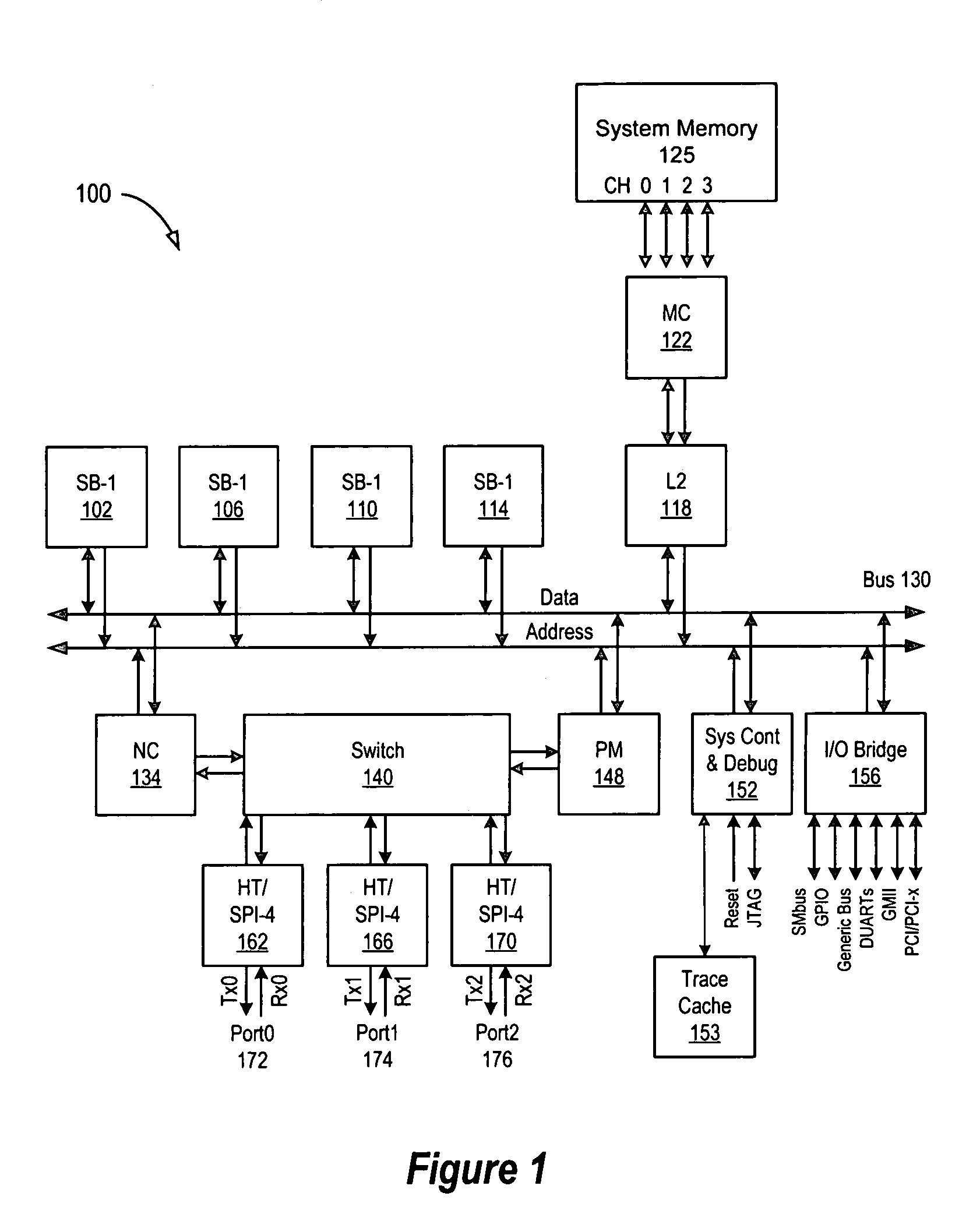

Scalable cache coherent distributed shared memory processing system

A packetized I / O link such as the HyperTransport protocol is adapted to transport memory coherency transactions over the link to support cache coherency in distributed shared memory systems. The I / O link protocol is adapted to include additional virtual channels that can carry command packets for coherency transactions over the link in a format that is acceptable to the I / O protocol. The coherency transactions support cache coherency between processing nodes interconnected by the link. Each processing node may include processing resources that themselves share memory, such as symmetrical multiprocessor configuration. In this case, coherency will have to be maintained both at the intranode level as well as the internode level. A remote line directory is maintained by each processing node so that it can track the state and location of all of the lines from its local memory that have been provided to other remote nodes. A node controller initiates transactions over the link in response to local transactions initiated within itself, and initiates transactions over the link based on local transactions initiated within itself. Flow control is provided for each of the coherency virtual channels either by software through credits or through a buffer free command packet that is sent to a source node by a target node indicating the availability of virtual channel buffering for that channel.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

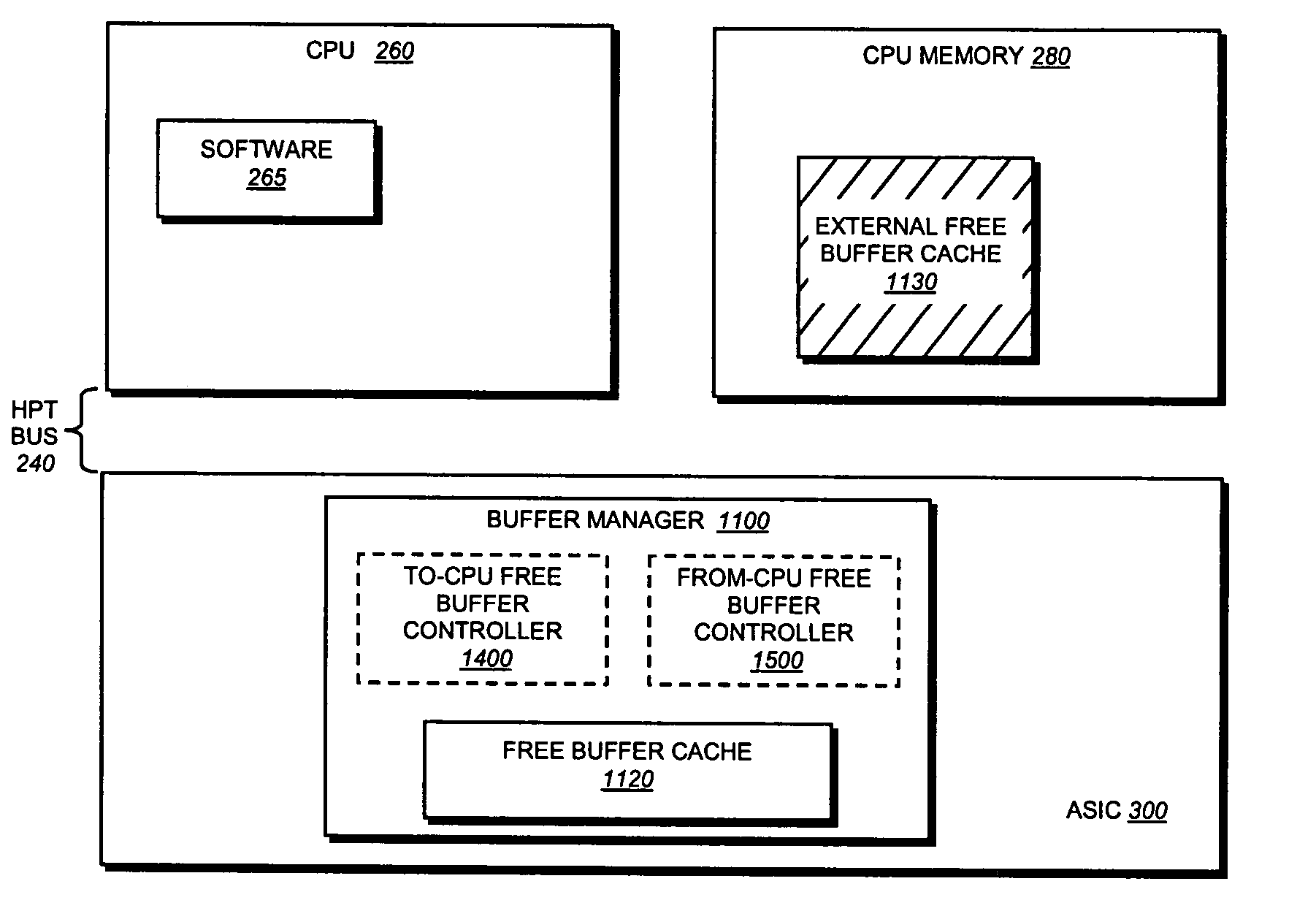

Buffer management technique for a hypertransport data path protocol

ActiveUS7111092B1Efficient managementReduce the amount of processingData switching by path configurationStore-and-forward switching systemsFile descriptorHyperTransport

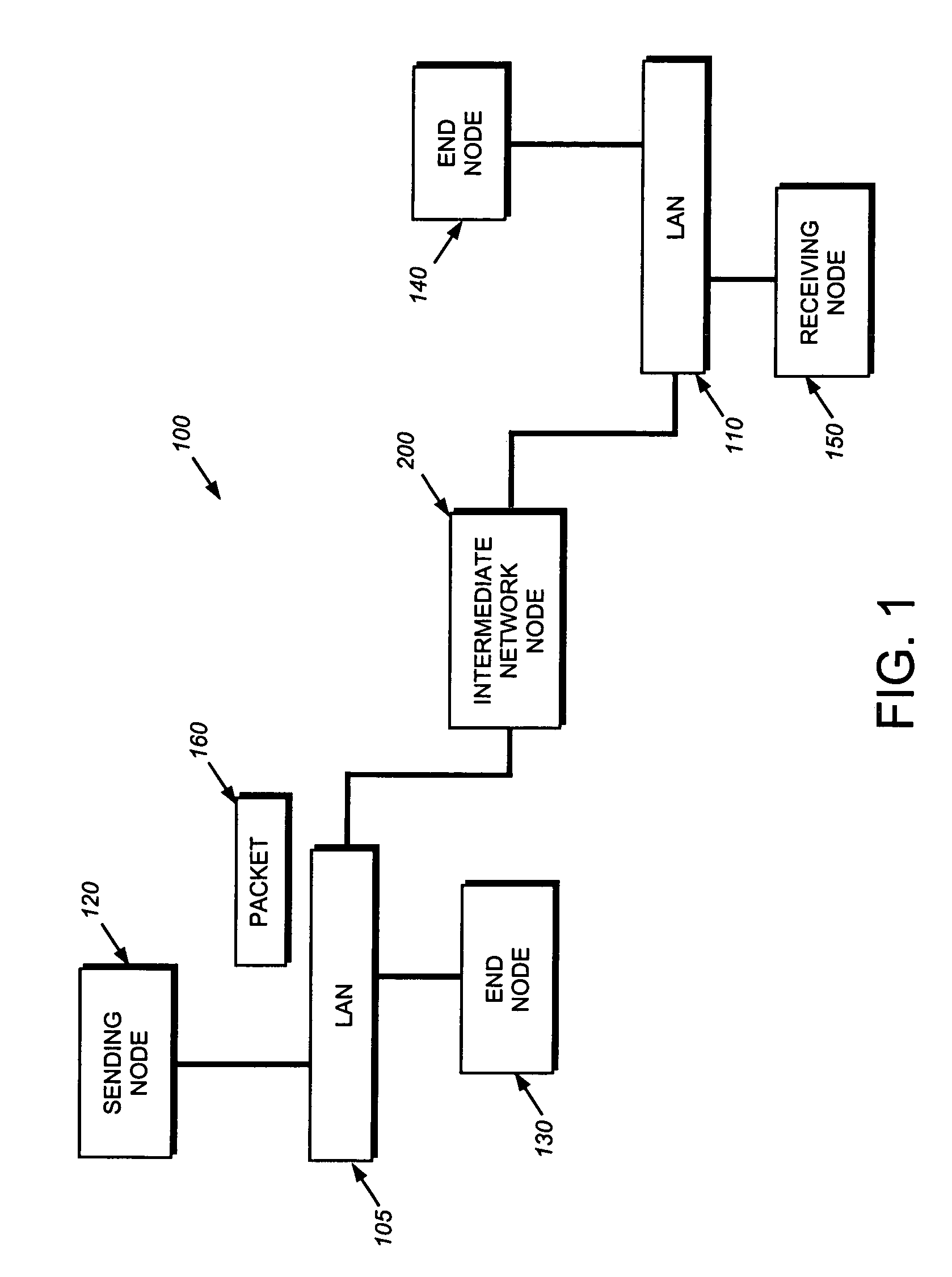

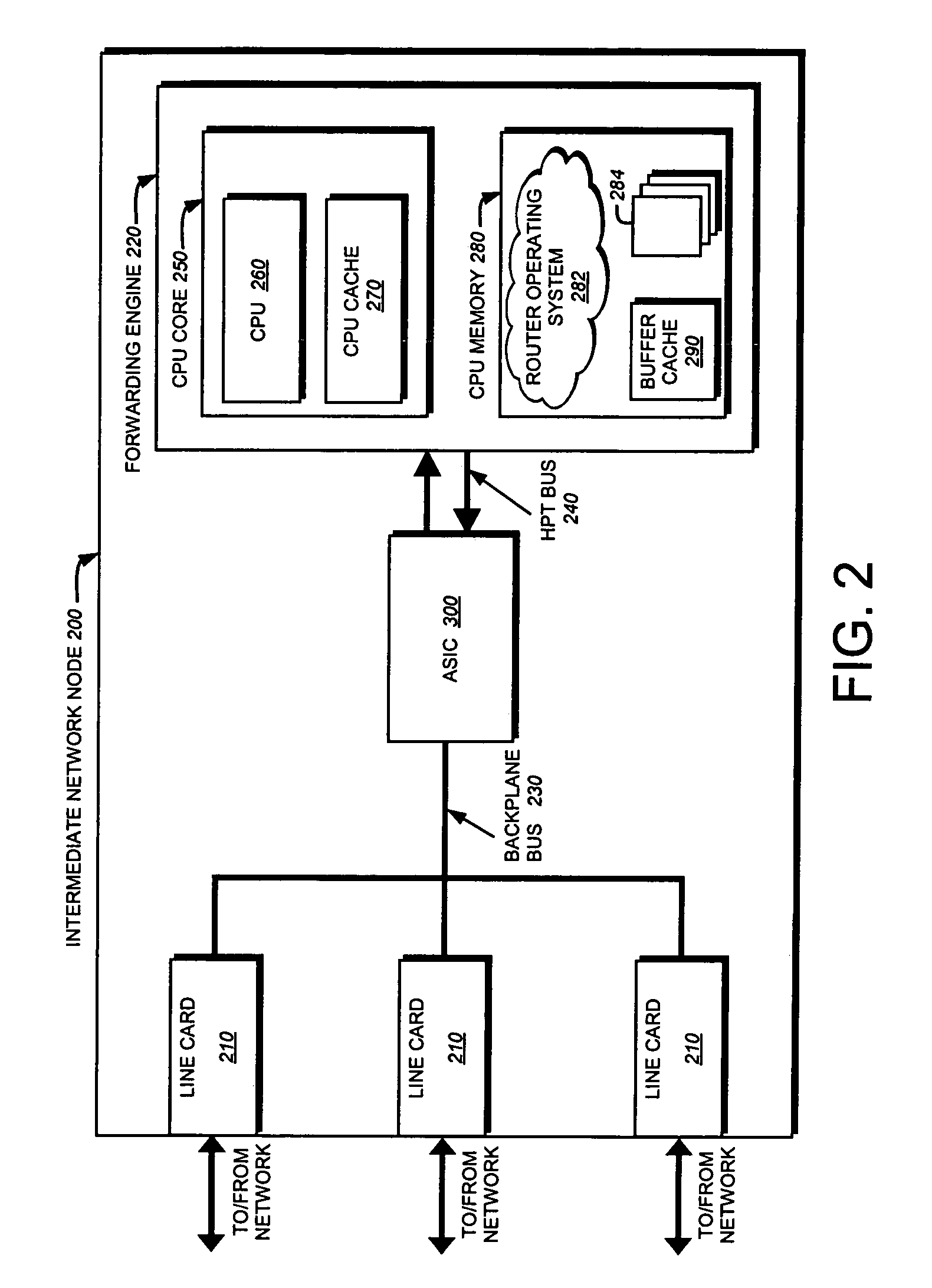

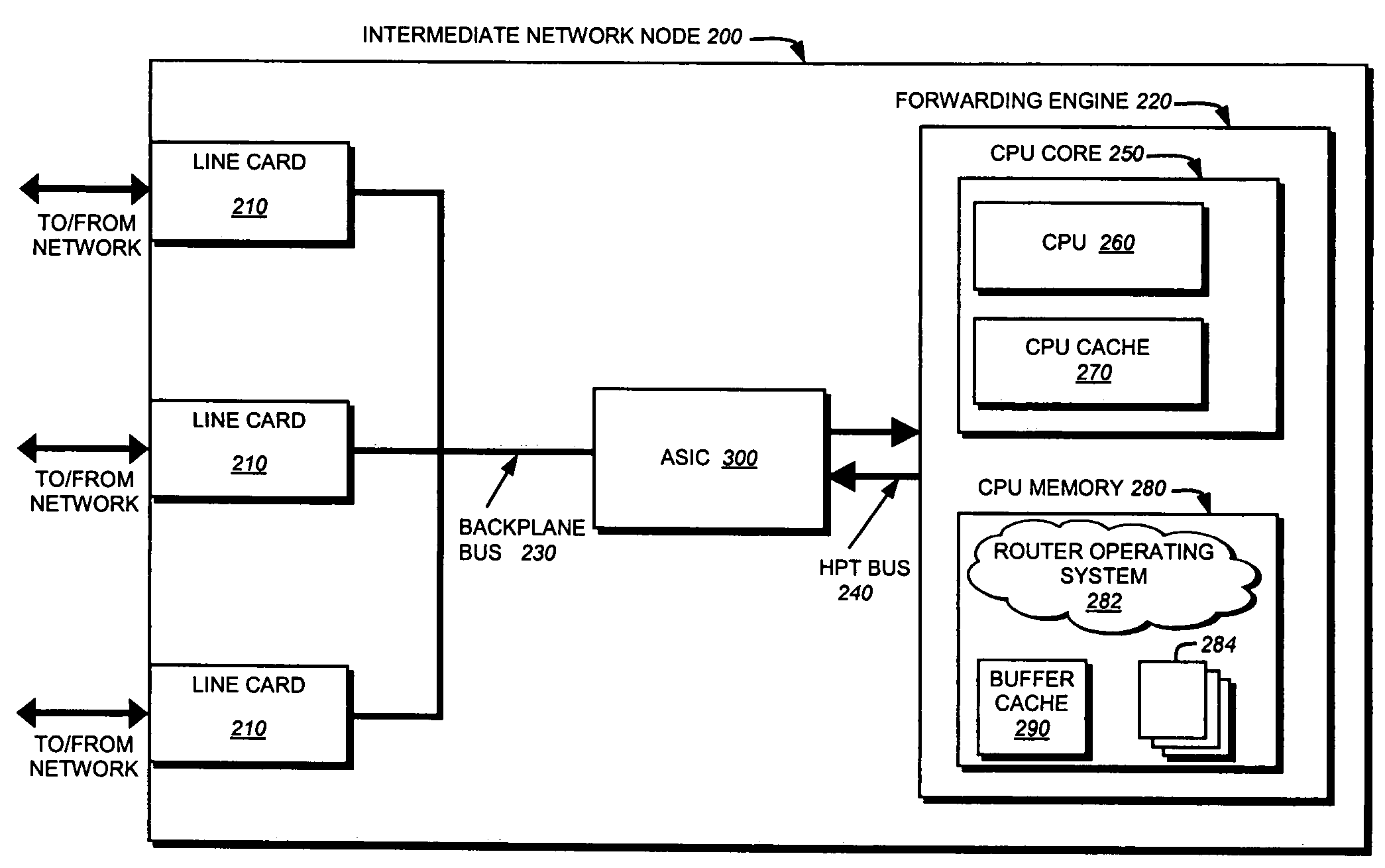

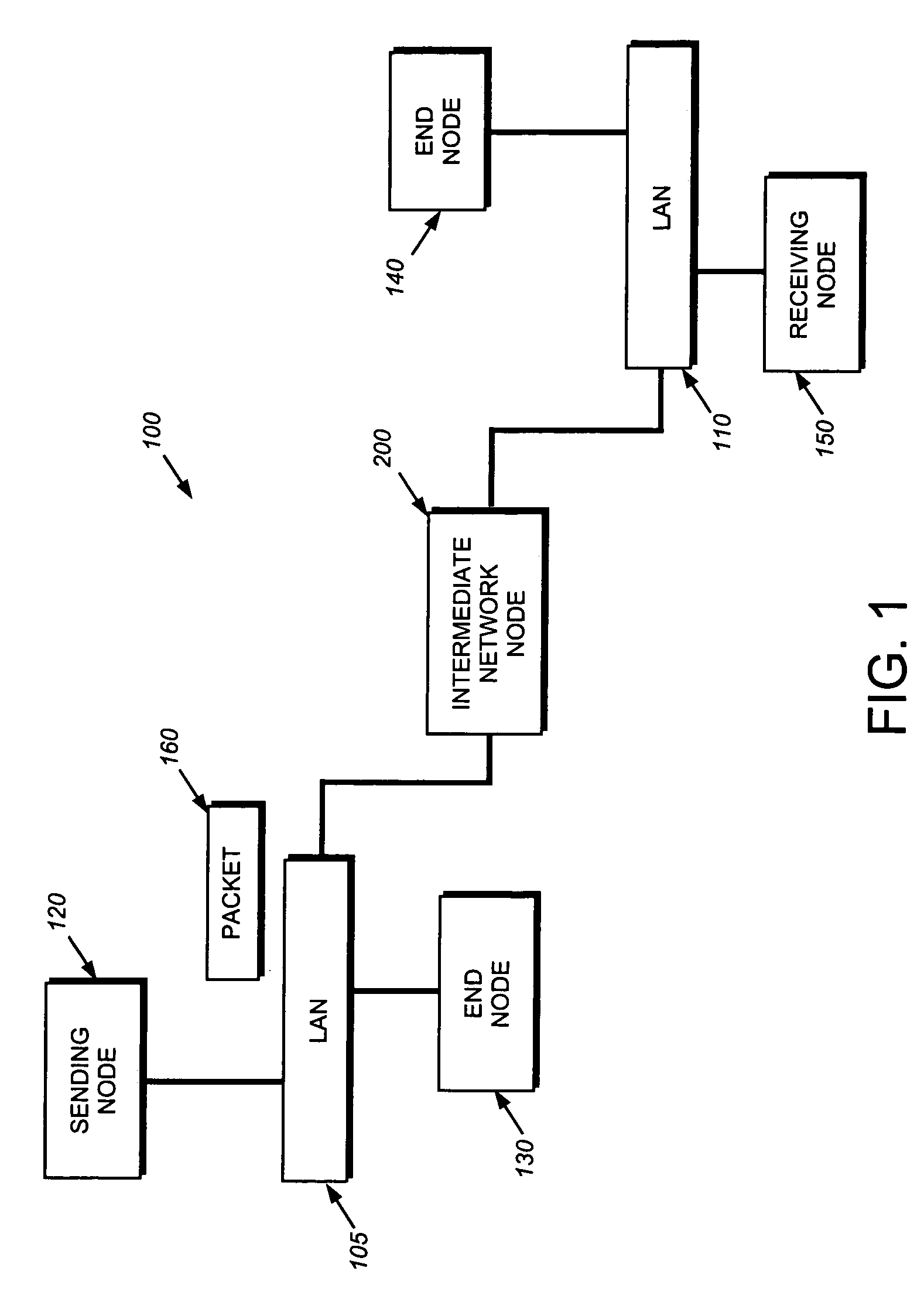

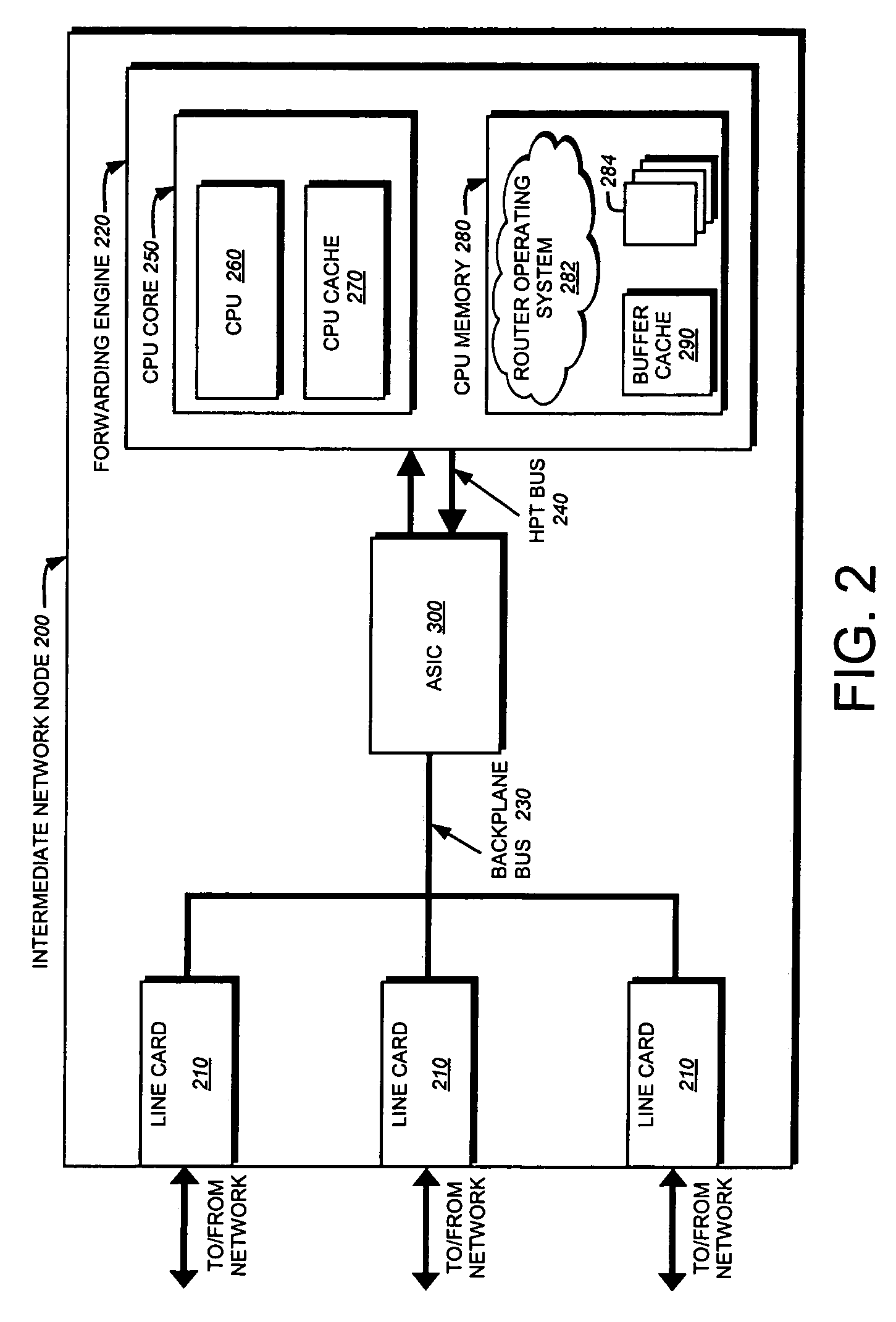

A buffer-management technique efficiently manages a set of data buffers accessible to first and second devices interconnected by a split transaction bus, such as a Hyper-Transport (HPT) bus. To that end, a buffer manager controls access to a set of “free” buffer descriptors, each free buffer descriptor referencing a corresponding buffer in the set of data buffers. Advantageously, the buffer manager ensures that the first and second devices are allocated a sufficient number of free buffer descriptors for use in a HPT data path protocol in which the first and second devices have access to respective sets of free buffer descriptors. Because buffer management over the HPT bus is optimized by the buffer manager, the amount of processing bandwidth traditionally consumed managing descriptors can be reduced.

Owner:CISCO TECH INC

Hypertransport data path protocol

A data path protocol eliminates most of the conventional read transactions required to transfer data between devices interconnected by a split transaction bus, such as a HyperTransport (HPT) bus. To that end, each device is configured to manage its own set of buffer descriptors, unlike previous data path protocols in which only one device managed all the buffer descriptors. As such, neither device has to perform a read transaction to retrieve a “free” buffer descriptor from the other device. As a result, only write transactions are performed for transferring descriptors across the HPT bus, thereby decreasing the amount of traffic over the bus and eliminating conventional latencies associated with read transactions. In addition, because descriptors are separately managed in each device, the data path protocol also conserves processing bandwidth that is traditionally consumed by managing ownership of the buffer descriptors within a single device.

Owner:CISCO TECH INC

Pass through circuit for reduced memory latency in a multiprocessor system

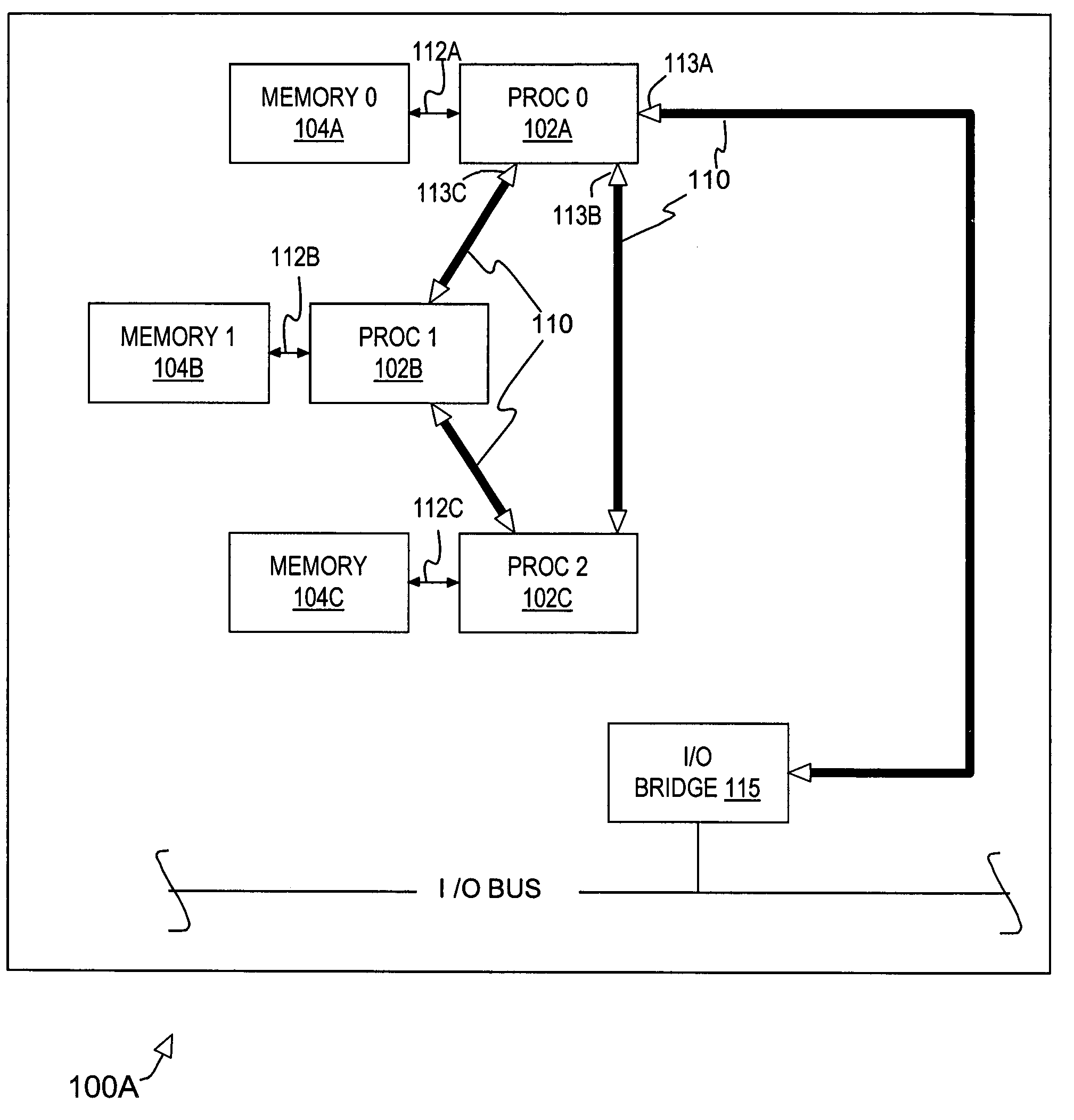

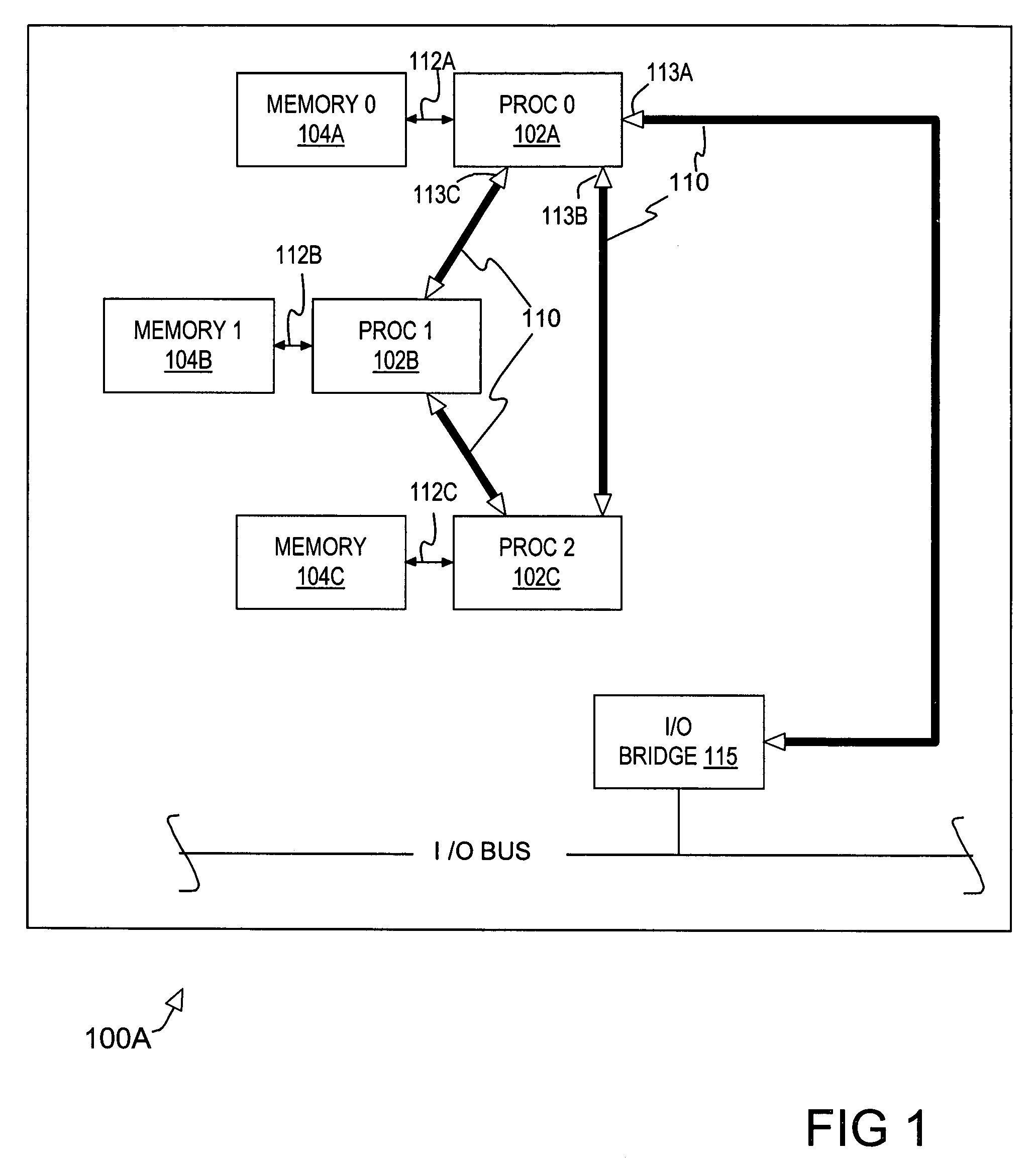

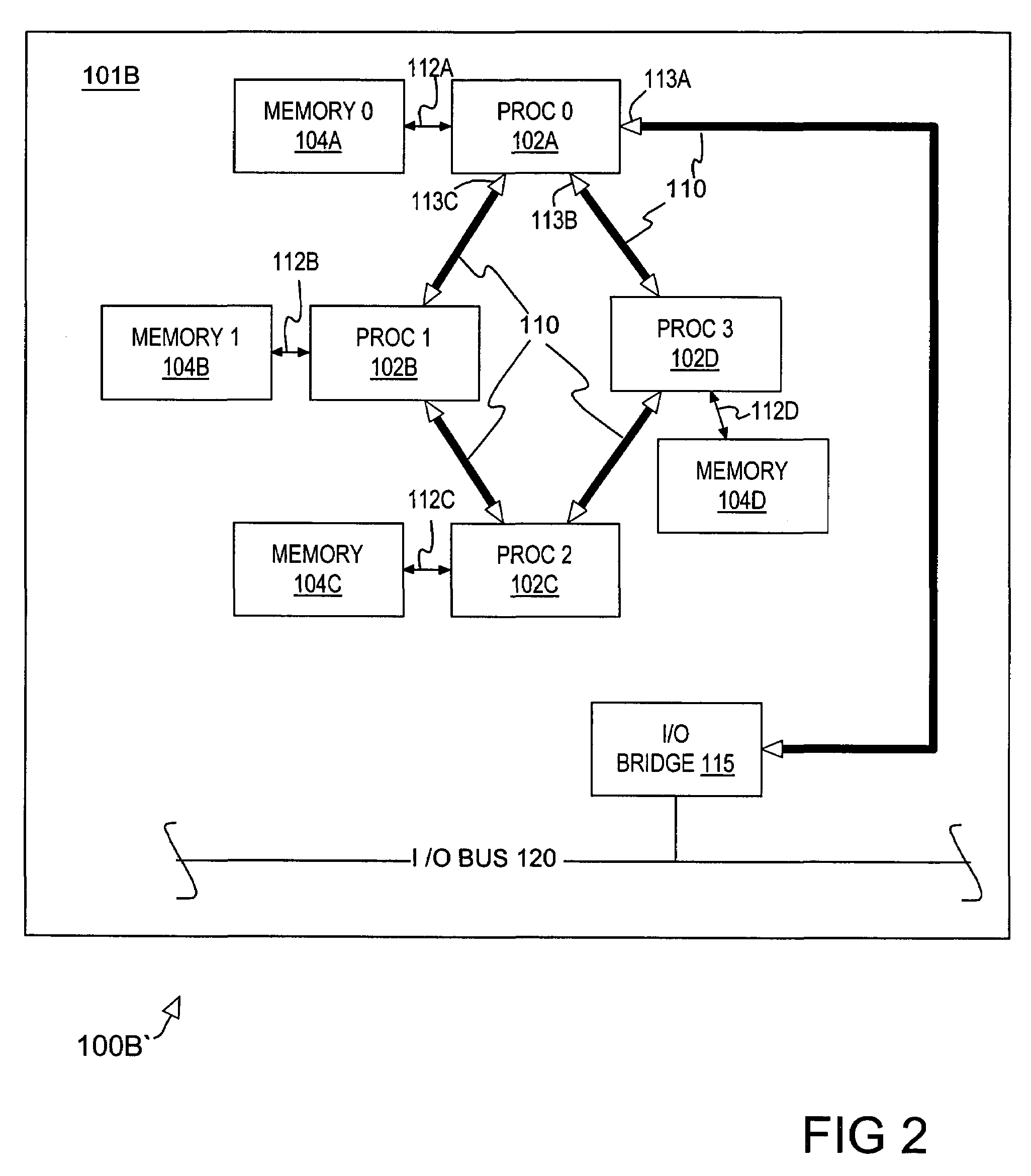

InactiveUS7007125B2Reducing memory latency asymmetryShorten the counting processPrinted circuit aspectsComponent plug-in assemblagesMulti processorParallel computing

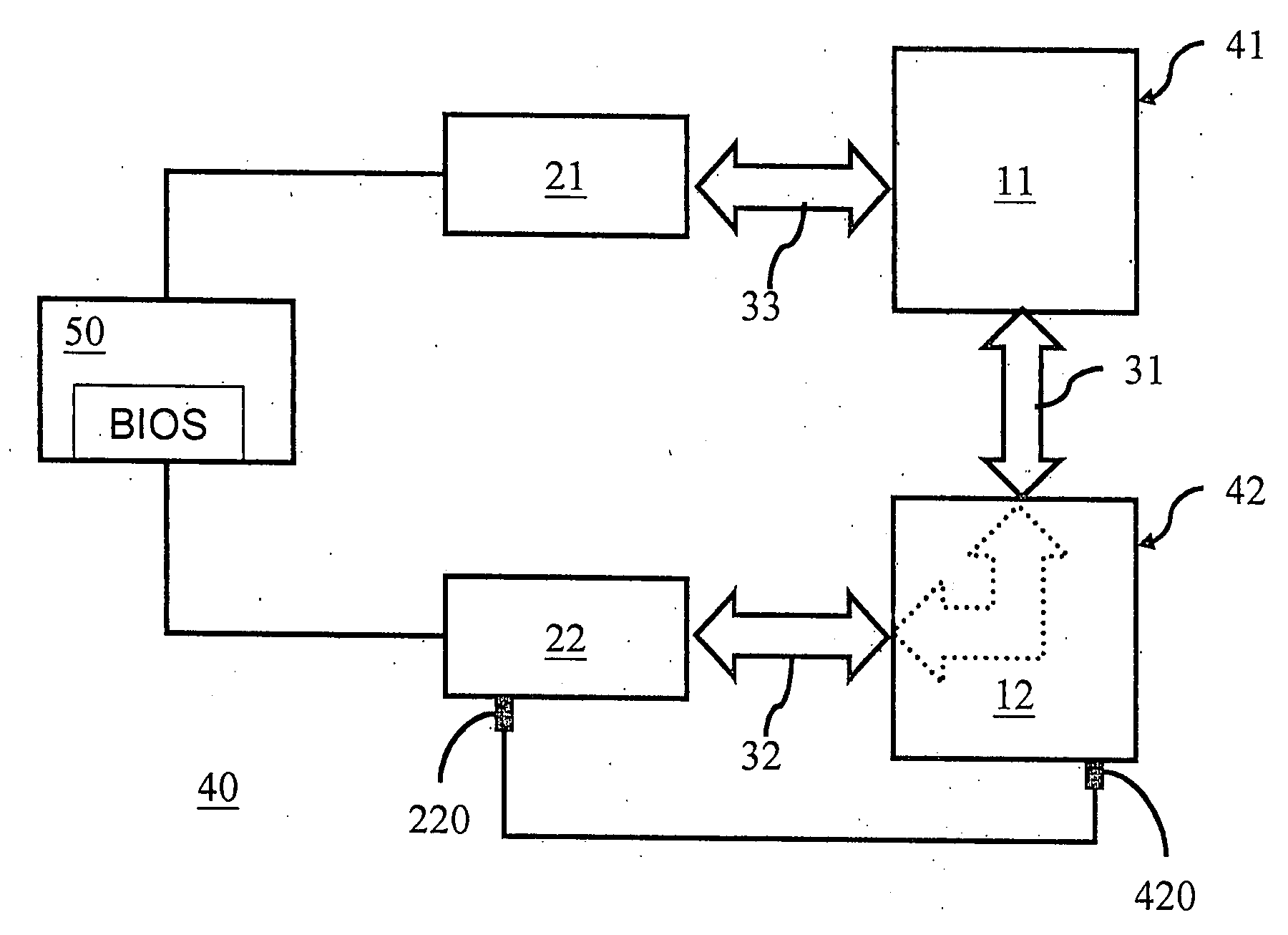

A technique and mechanism for reducing memory latency asymmetry in a multiprocessor system by replacing one (or more) processors with a bypass or pass-through device. Using the pass-through mechanism, the reduced number of processors in the system enables all of the remaining processors to connect to each other directly using the interconnect links. The reduction in processor count improves symmetry and reduces overall latency thereby potentially improving performance of certain applications despite having fewer processors. In one specific implementation, the pass through device is used to connect two HyperTransport links together where each of the links is connected to a processor at the other end.

Owner:LENOVO GLOBAL TECH INT LTD

Motherboard capable of selectively supporting dual graphic engine

InactiveUS20070067535A1Low costImprove the display effectElectric digital data processingGraphicsEngineering

A motherboard includes a north bridge circuit, a central processing unit (CPU) socket coupled to the north bridge circuit through a hypertransport bus; a first slot coupled to the north bridge circuit; and an upgrade slot, coupled to the second slot and the hypertransport bus, for installing a removable tunnel module. When the removable tunnel module is installed inside the upgrade slot, the motherboard is capable of supporting a computer component installed inside the second slot.

Owner:ELITEGROUP COMPUTER SYSTEMS

Split transaction reordering circuit

The present invention provides a technique for ordering responses received over a split transaction bus, such as a HyperTransport bus (HPT). When multiple non-posted requests are sequentially issued over the split transaction bus, control logic is used to assign each request an identifying (ID) number, e.g. up to a maximum number of outstanding requests. Similarly, each response received over the split transaction bus is assigned the same ID number as its corresponding request. Accordingly, a “response memory” comprises a unique memory block for every possible ID number, and the control logic directs a received response to its corresponding memory block. The responses are extracted from blocks of response memory in accordance with a predetermined set of ordering rules. For example, the responses may be accessed in the same order the corresponding non-posted requests were issued.

Owner:CISCO TECH INC

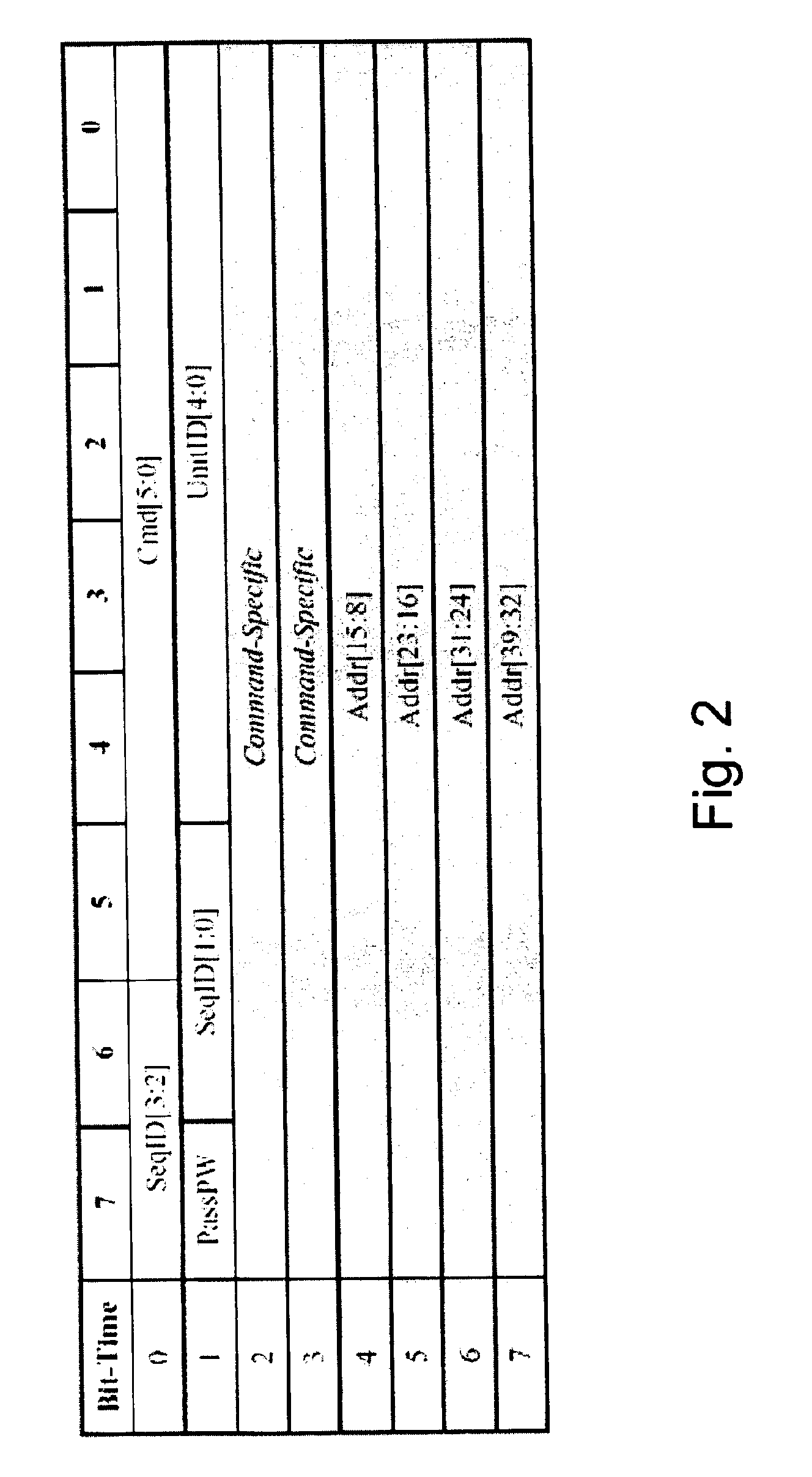

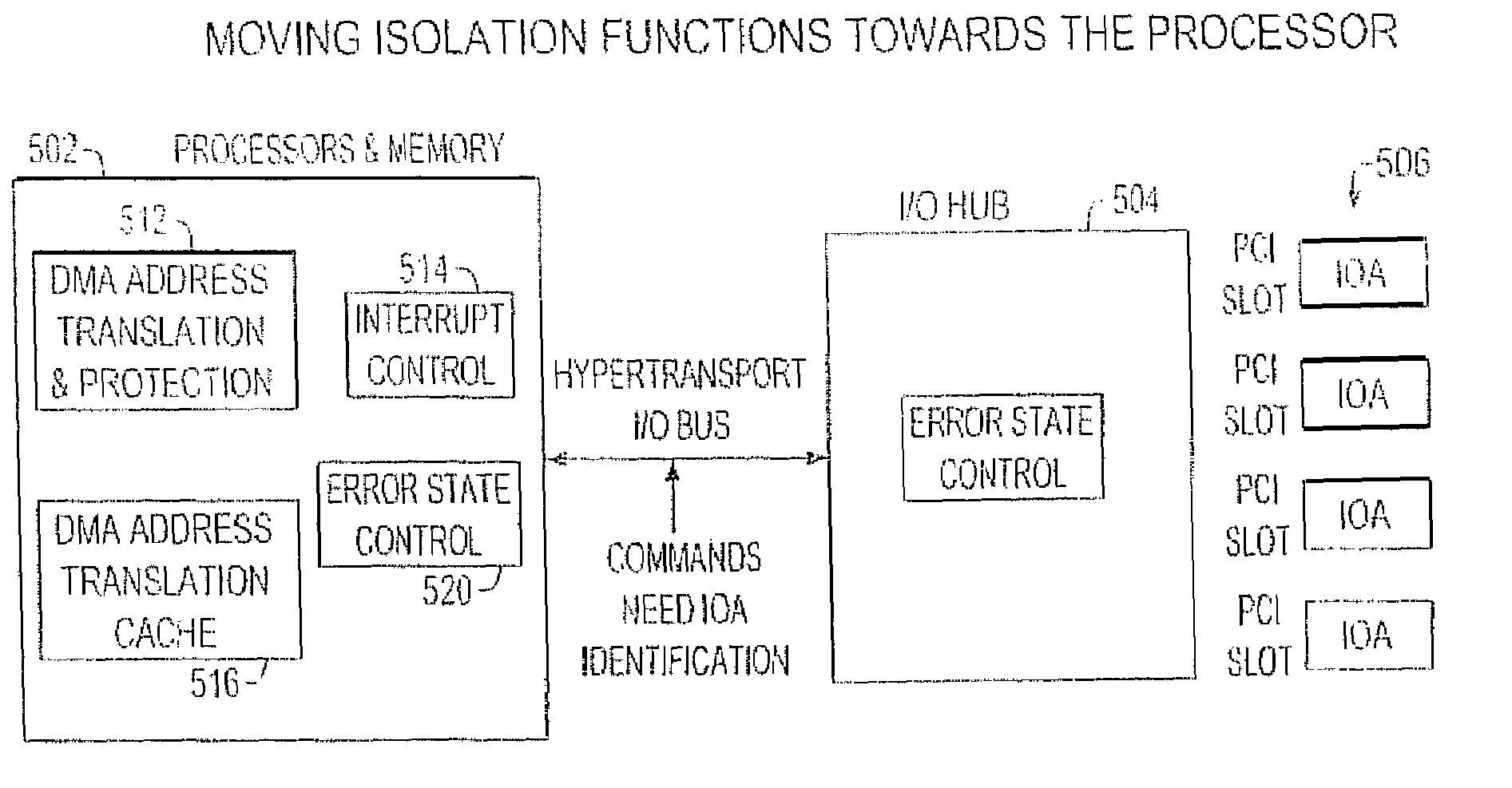

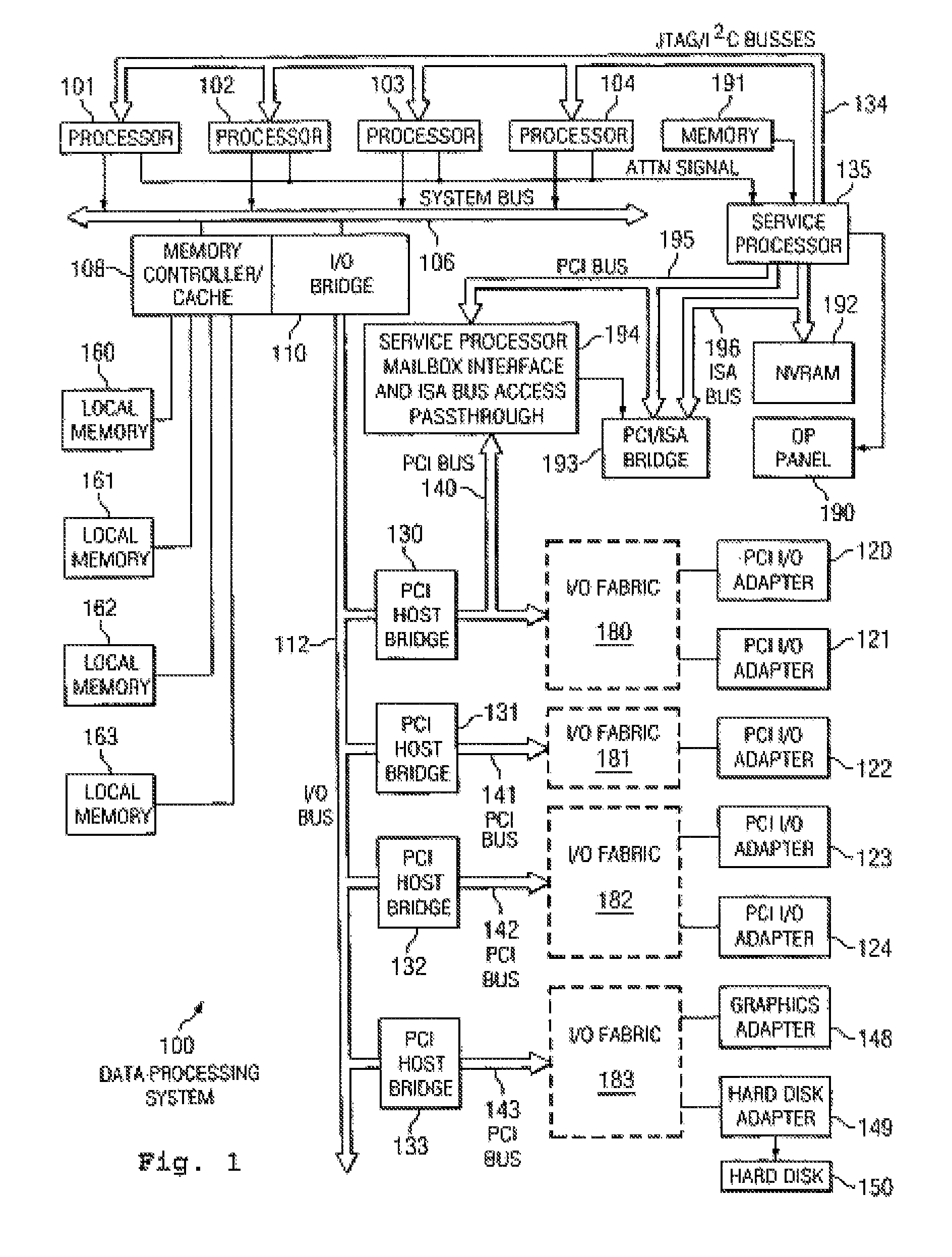

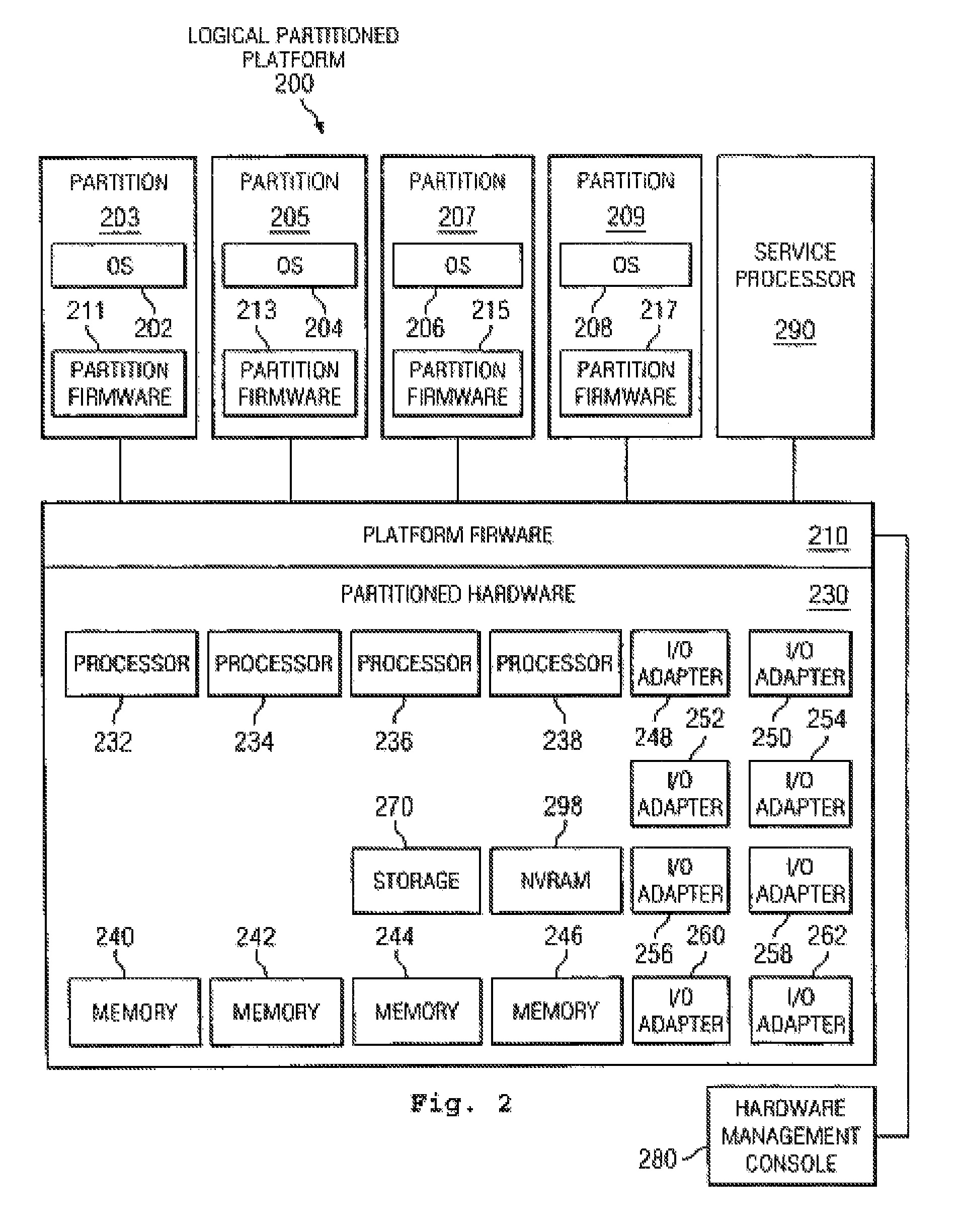

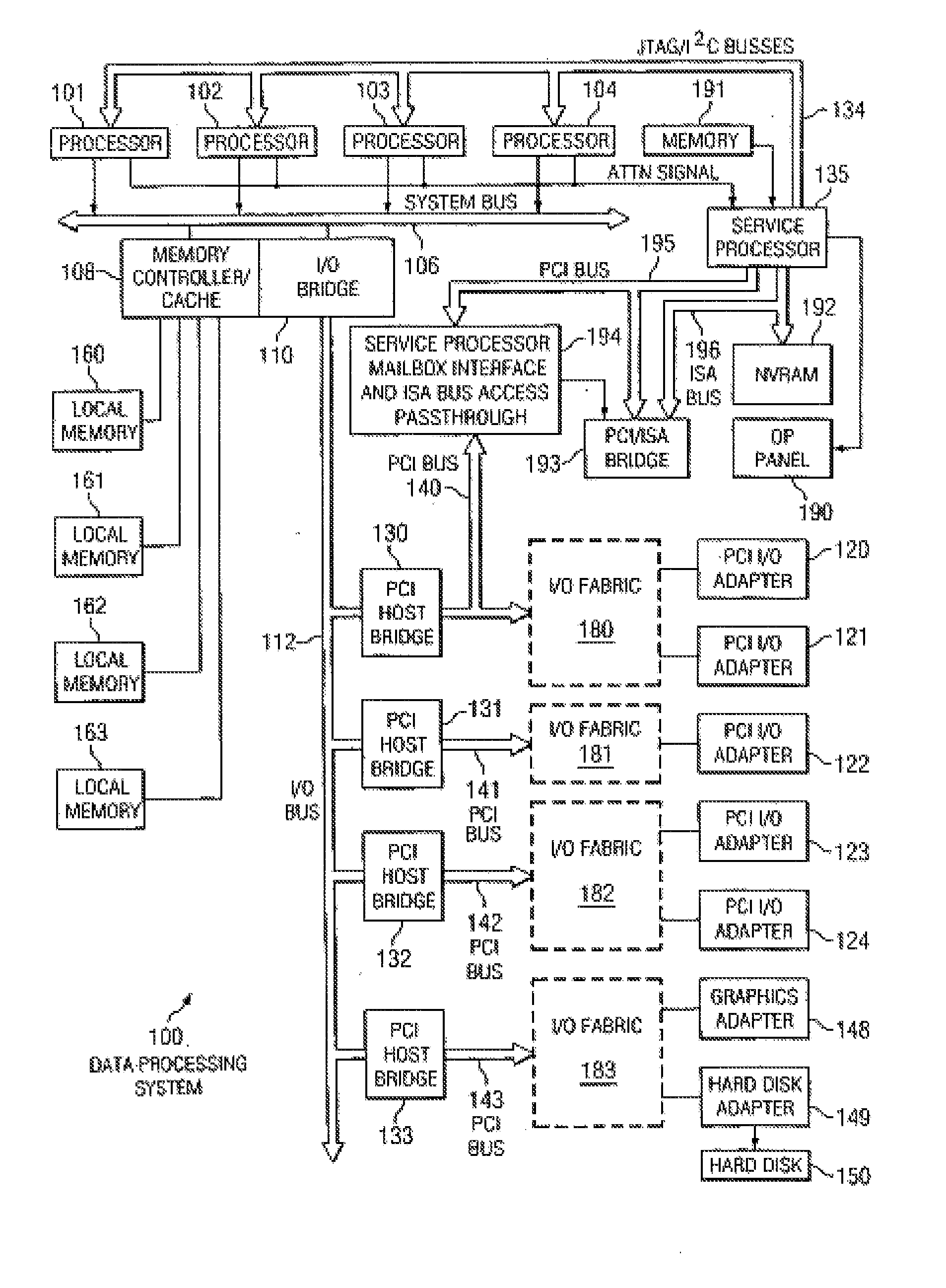

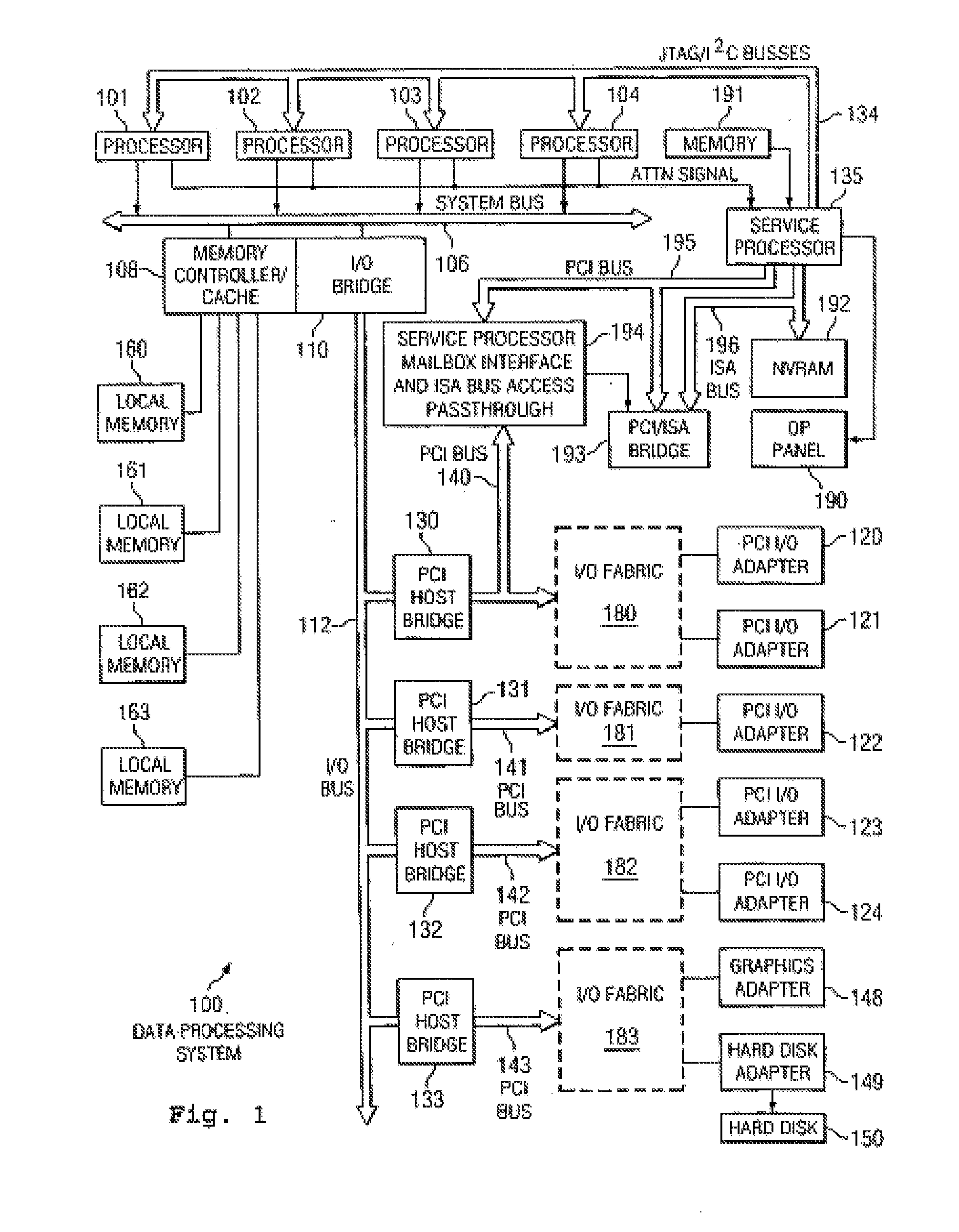

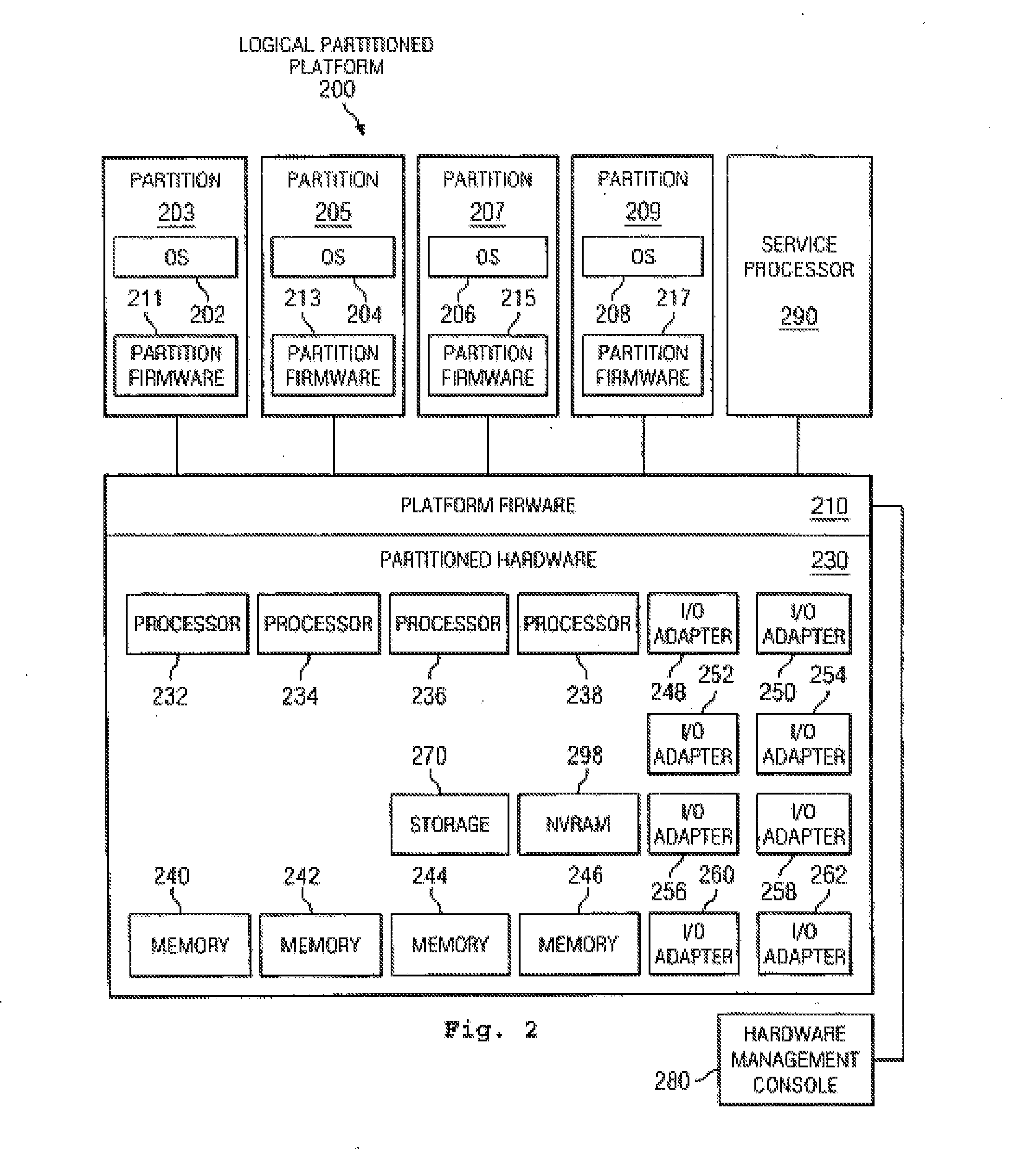

I/O adapter LPAR isolation in a hypertransport environment

Disclosed are a data processing system and a method of isolating a plurality of input / output adapter units of that system. The data processing system comprises, in addition to the input / output adapter units, a set of processors, a host bridge, and a system bus connecting the set of processors and the host bridge. Each of the input / output adapter units has a respective identifier; and the set of processors send commands to the host bridge, said commands including one or more of the identifiers of the input / output adapter units. In the preferred embodiment, these identifiers are HyperTransport defined Unit IDs, and the commands issued by the set of processors include a Unit ID field including one or more of the Unit IDs of input / output adapters.

Owner:INT BUSINESS MASCH CORP

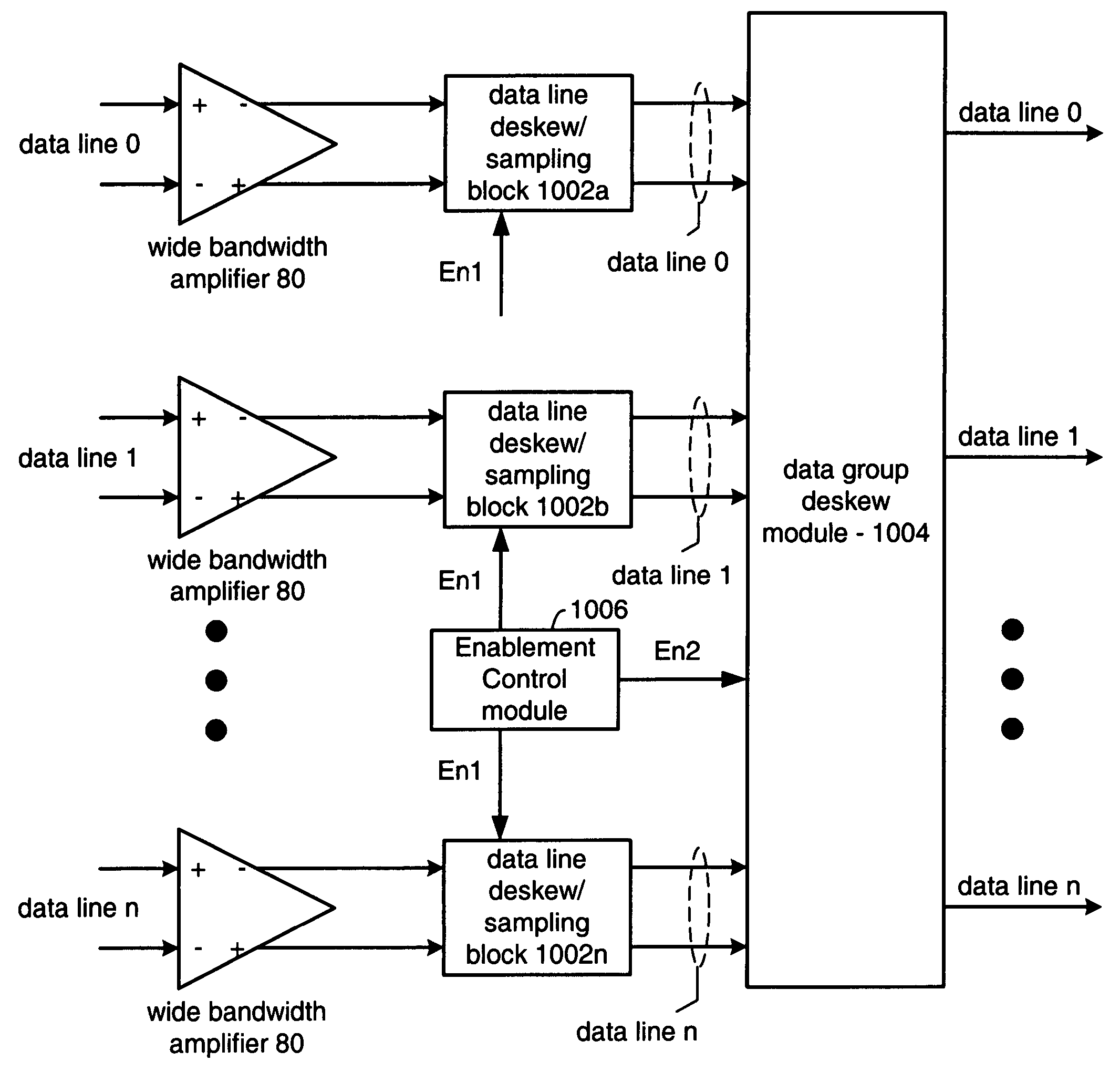

Hypertransport/SPI-4 interface supporting configurable deskewing

InactiveUS7490187B2Optimal data rateError detection/correctionGeneral purpose stored program computerAudio power amplifierDigital interface

Owner:AVAGO TECH INT SALES PTE LTD

I/O adapter lpar isolation in a hypertransport environment

ActiveUS20080147891A1Input/output processes for data processingData processing systemParallel computing

Disclosed are a data processing system and a method of isolating a plurality of input / output adapter units of that system. The data processing system comprises, in addition to the input / output adapter units, a set of processors, a host bridge, and a system bus connecting the set of processors and the host bridge. Each of the input / output adapter units has a respective identifier; and the set of processors send commands to the host bridge, said commands including one or more of the identifiers of the input / output adapter units. In the preferred embodiment, these identifiers are HyperTransport defined Unit IDs, and the commands issued by the set of processors include a Unit ID field including one or more of the Unit IDs of input / output adapters.

Owner:IBM CORP

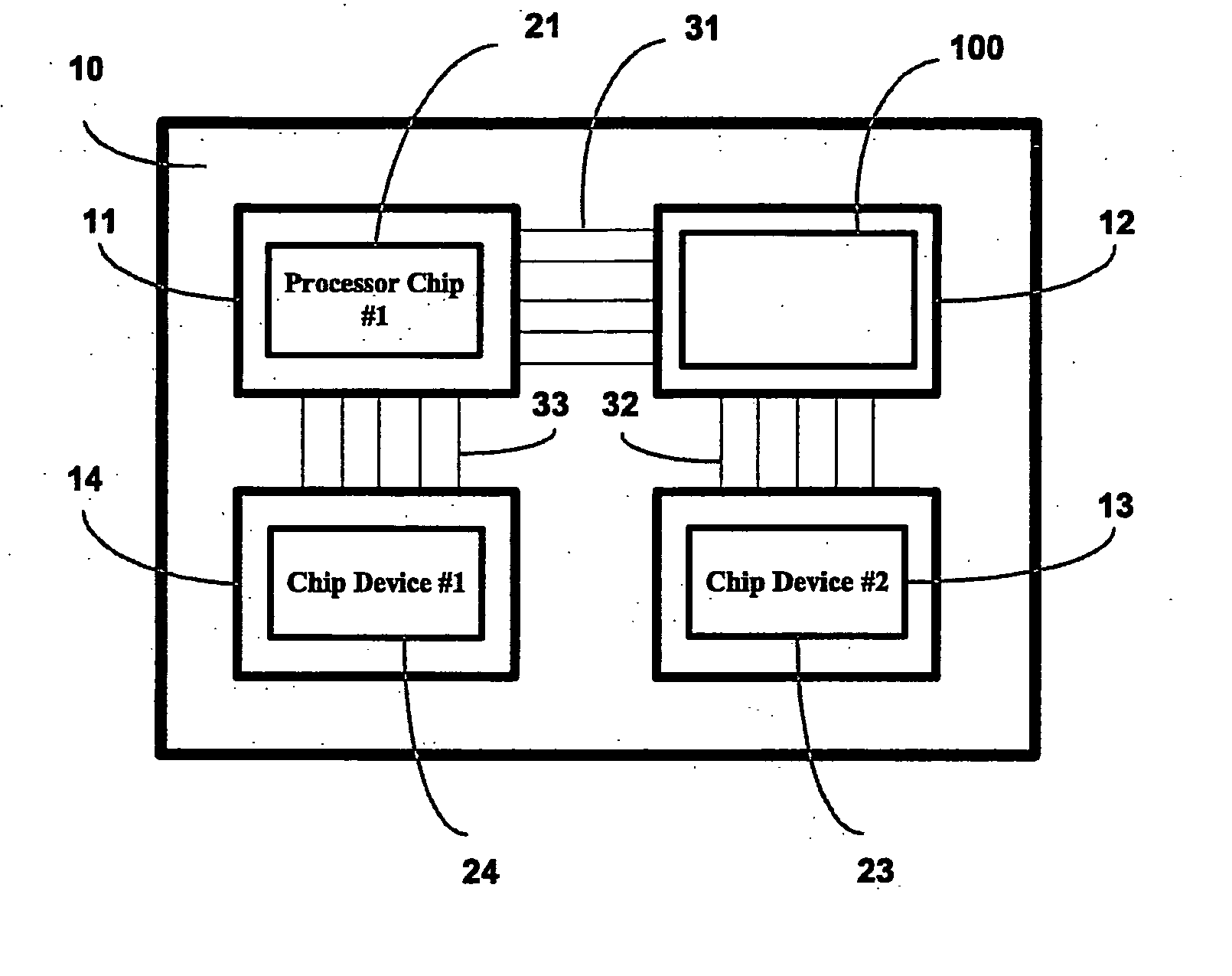

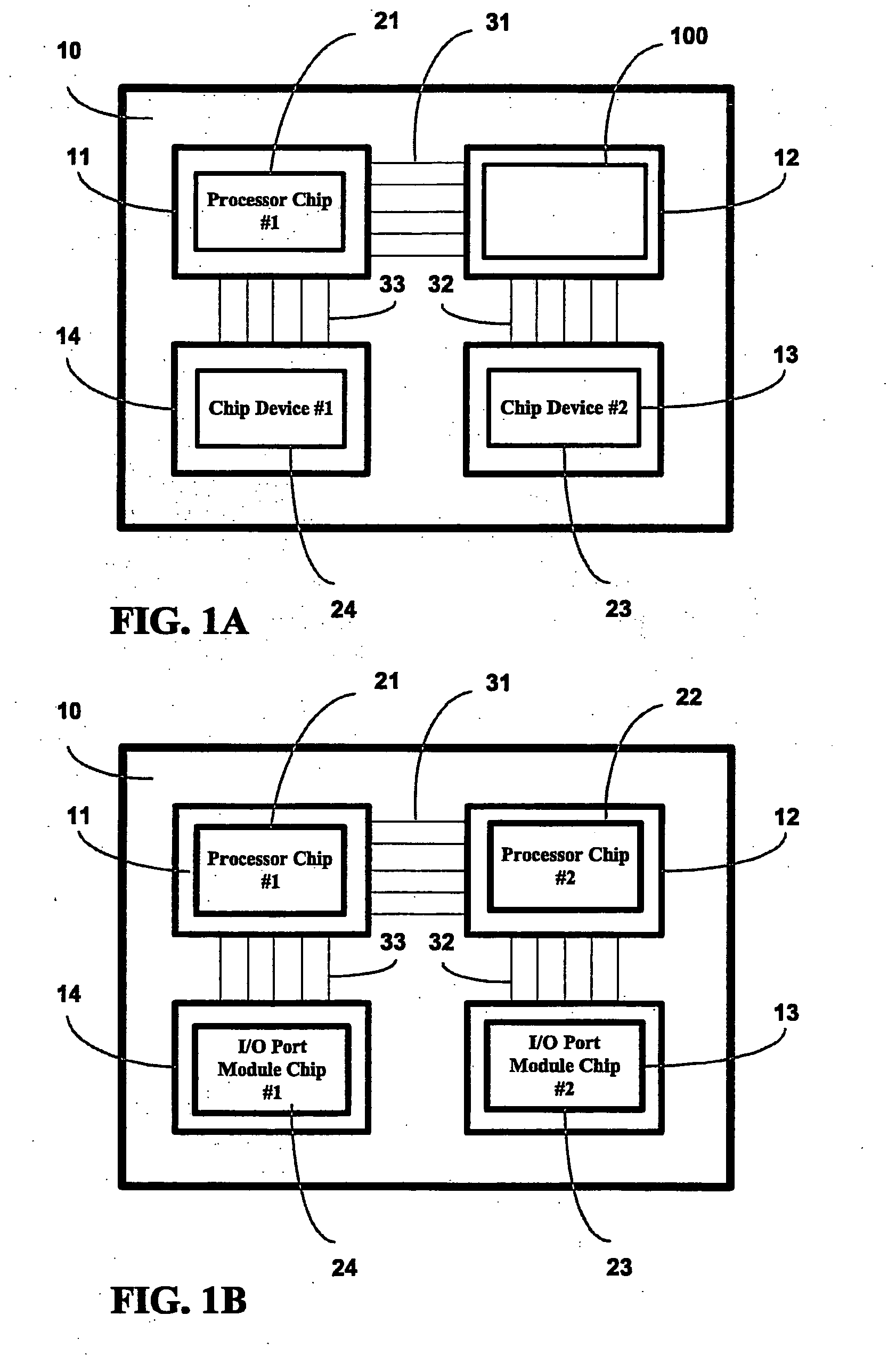

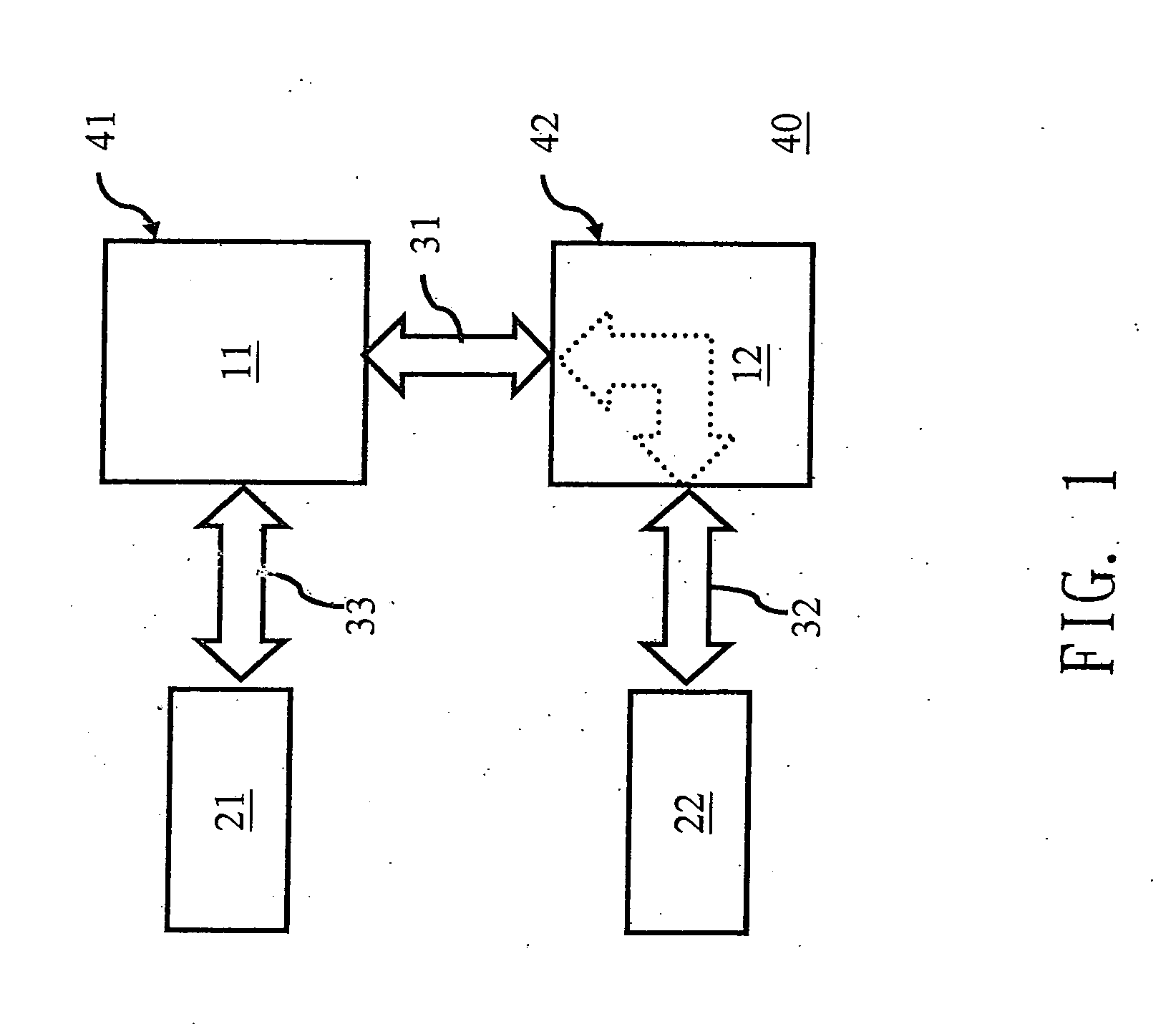

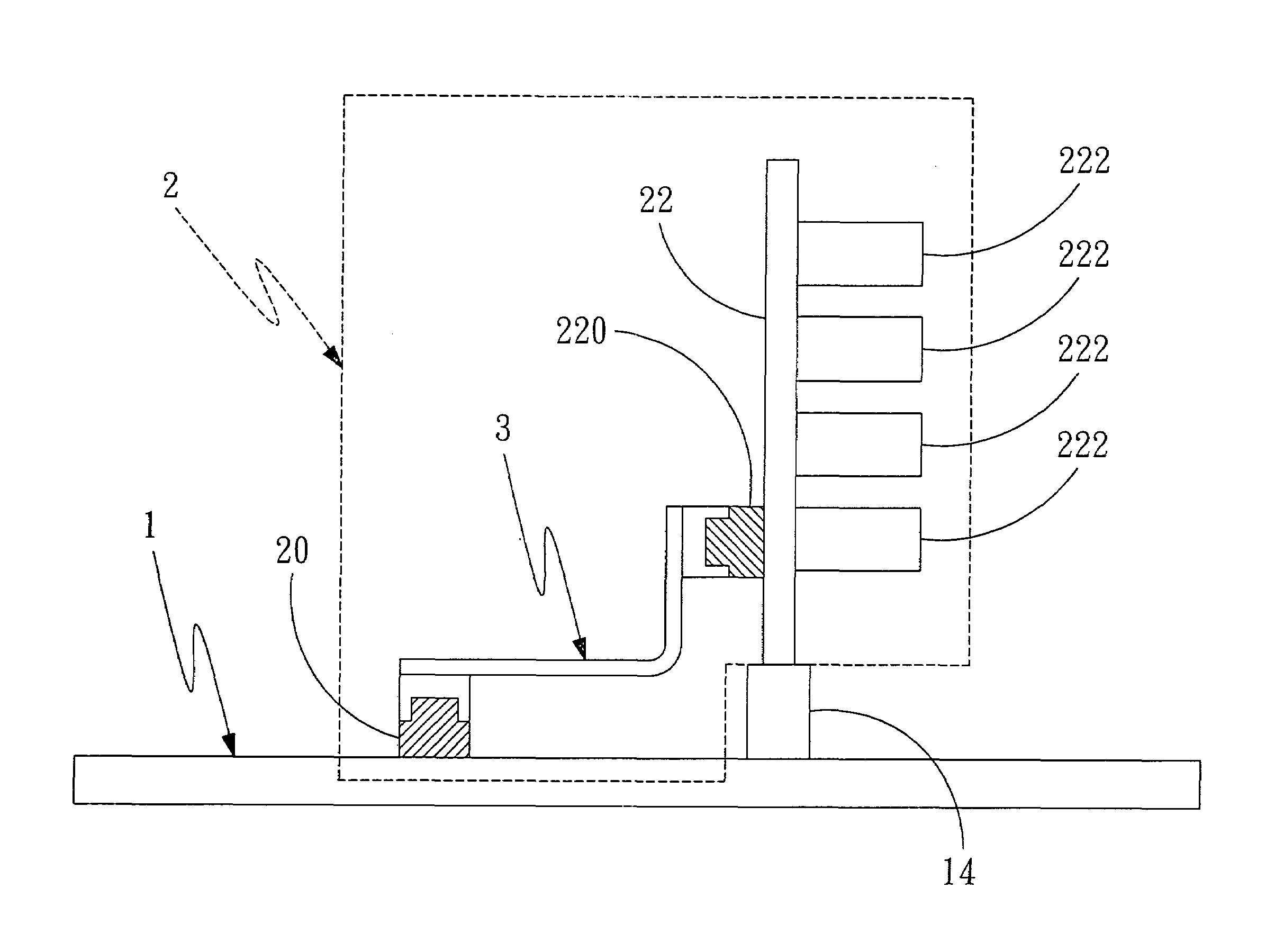

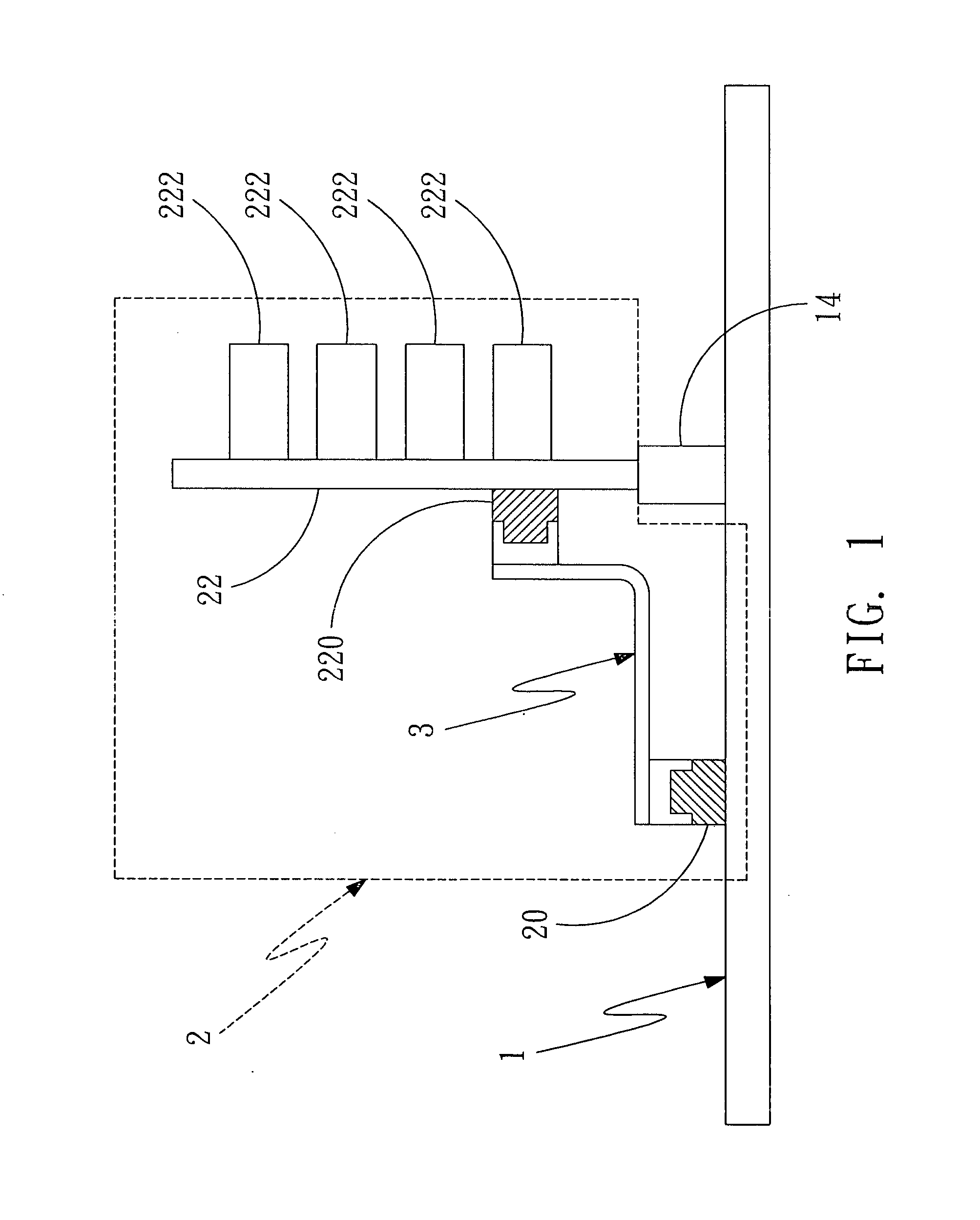

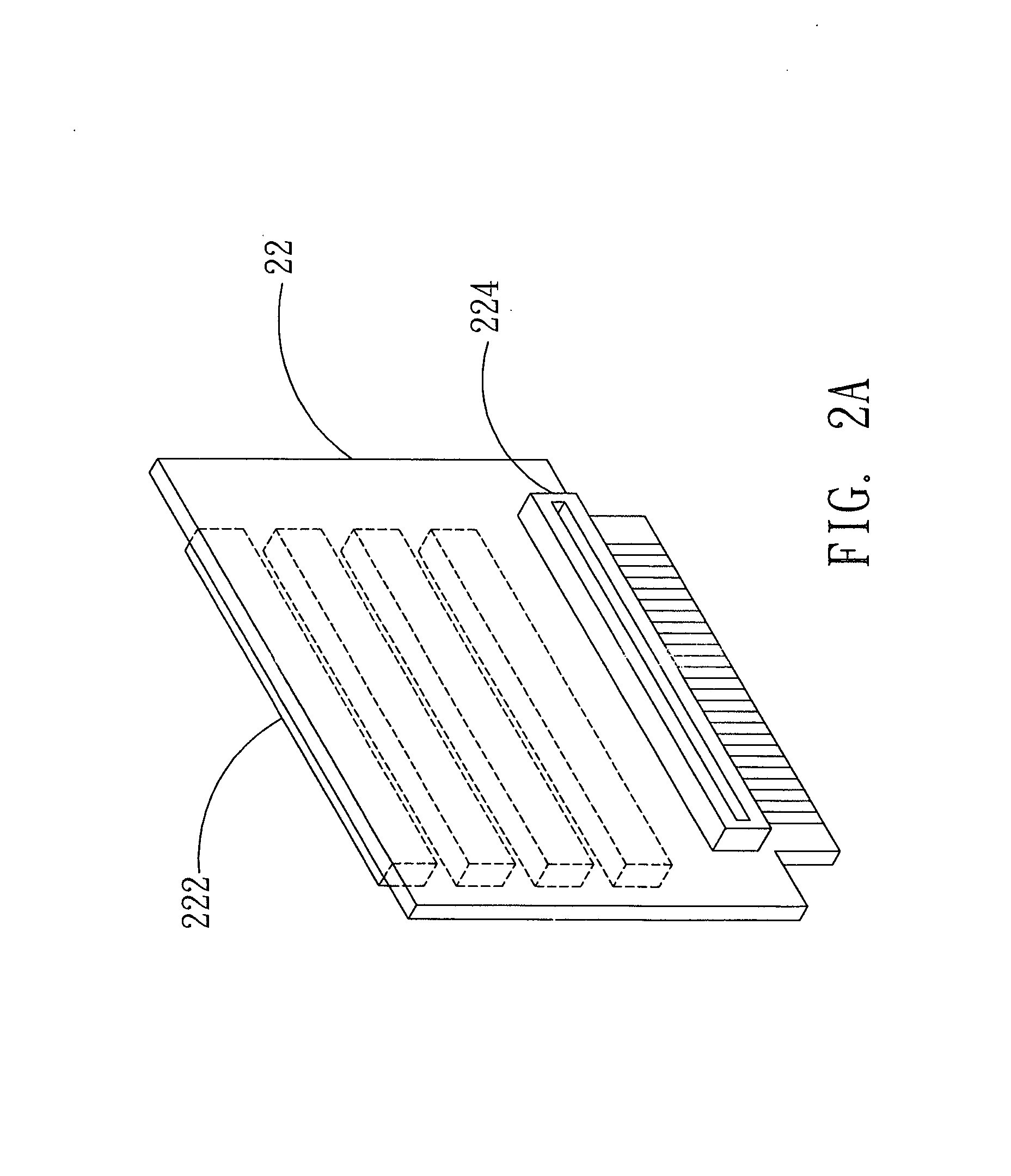

Multi-socket circuit board chip bridging device

InactiveUS20060129732A1Cost-effective manufacturingCost-effectiveElectric digital data processingEffective solutionMulti processor

A multi-socket circuit board chip bridging device is proposed, which is designed for use in conjunction with a multi-socket circuit board having multiple sockets and utilizing a special type of bus architecture, such as the HT (HyperTransport) bus architecture, for use to be mounted on a selected one of the sockets for the purpose of connecting one chip mounted on a first socket to another chip mounted on a second socket on the multi-socket circuit board. This feature allows manufacturer to utilize just one kind of circuit board for the implementation of a variety of multi-processor computer motherboards or hardware platforms having different number of processors, without having to design different types of multi-processor computer motherboards, thus representing a more cost-effective solution to the manufacture of multi-processor computer motherboards than prior art.

Owner:INVENTEC CORP

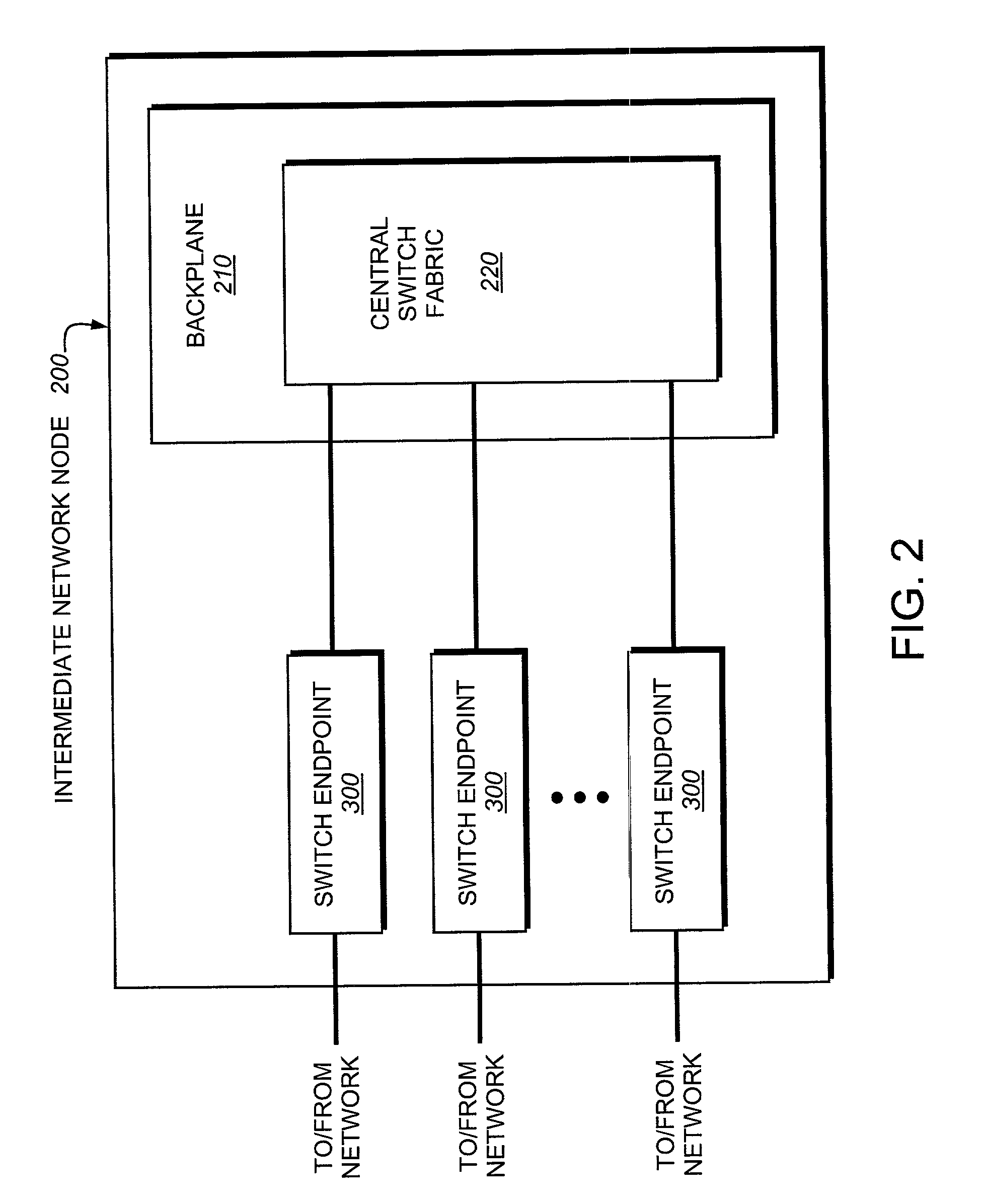

Method and apparatus for a federation control plane in an orthogonal system

A method of and architecture for controlling board elements in an orthogonal system architecture is provided. The method and architecture preferably utilize an internal bus architecture between control boards, such that a first control board can access board elements in its stack via I / O on a second control board and the second control board can access board elements in its stack via I / O on the first control board. Most preferably the internal bus architecture is a HyperTransport bus architecture.

Owner:GENERAL DYNAMICS ADVANCED INFORMATION SYST INC

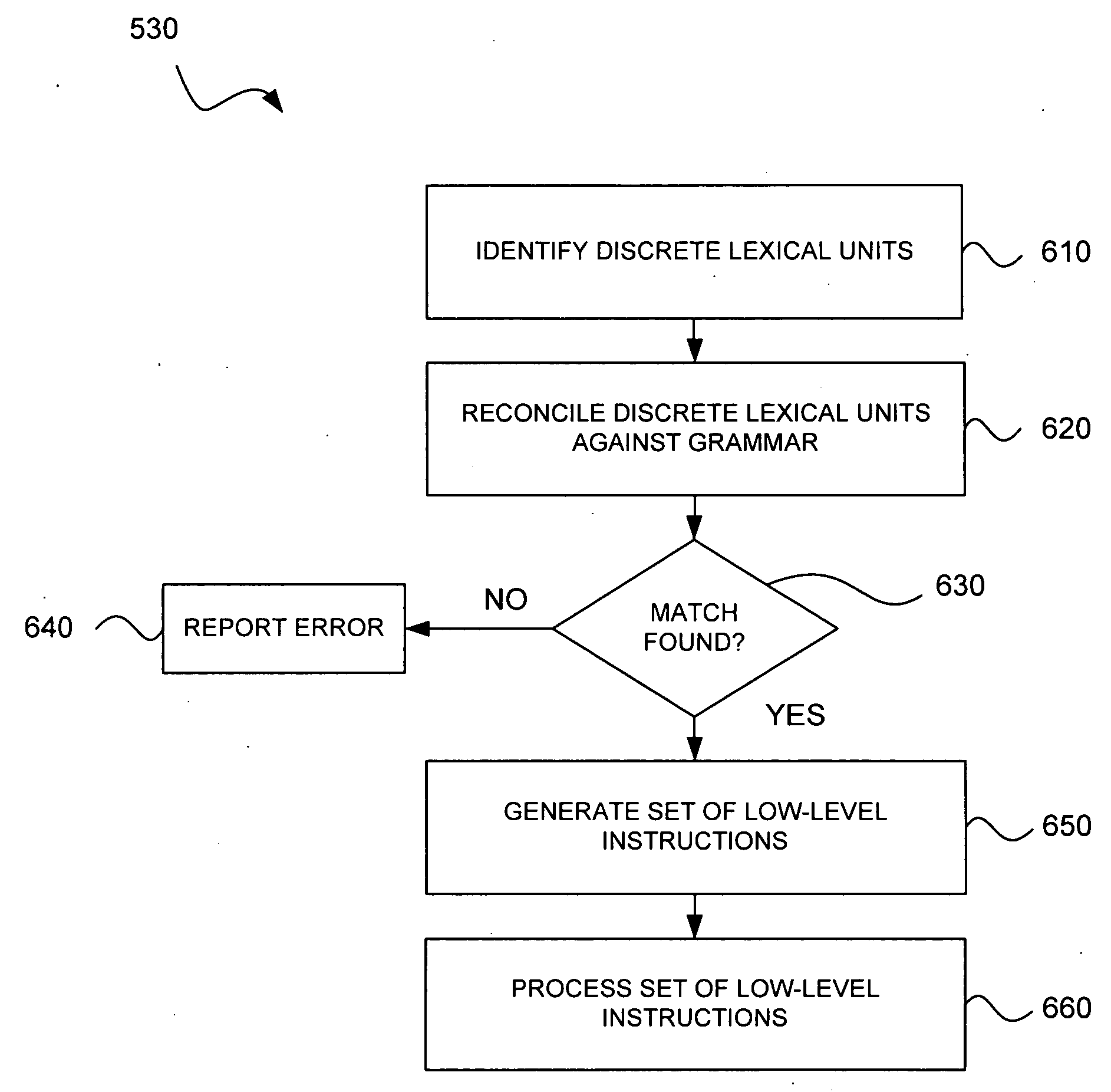

Message passing interface framework for supporting bus communication

InactiveCN101866326AMeet application needsElectric digital data processingOperational systemMessage Passing Interface

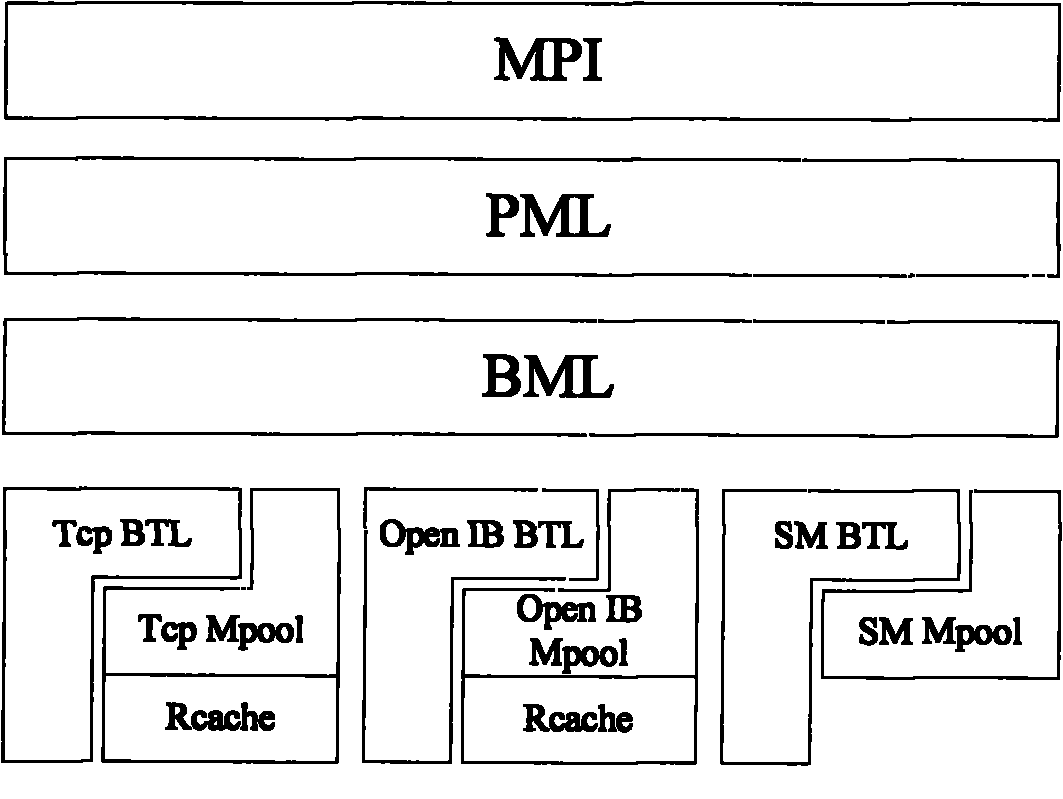

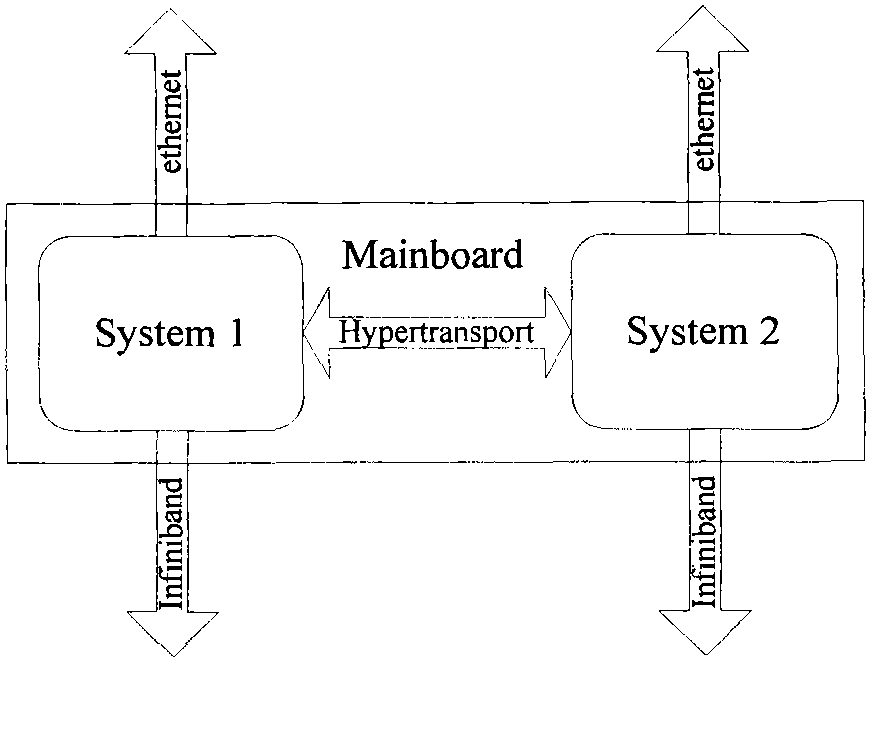

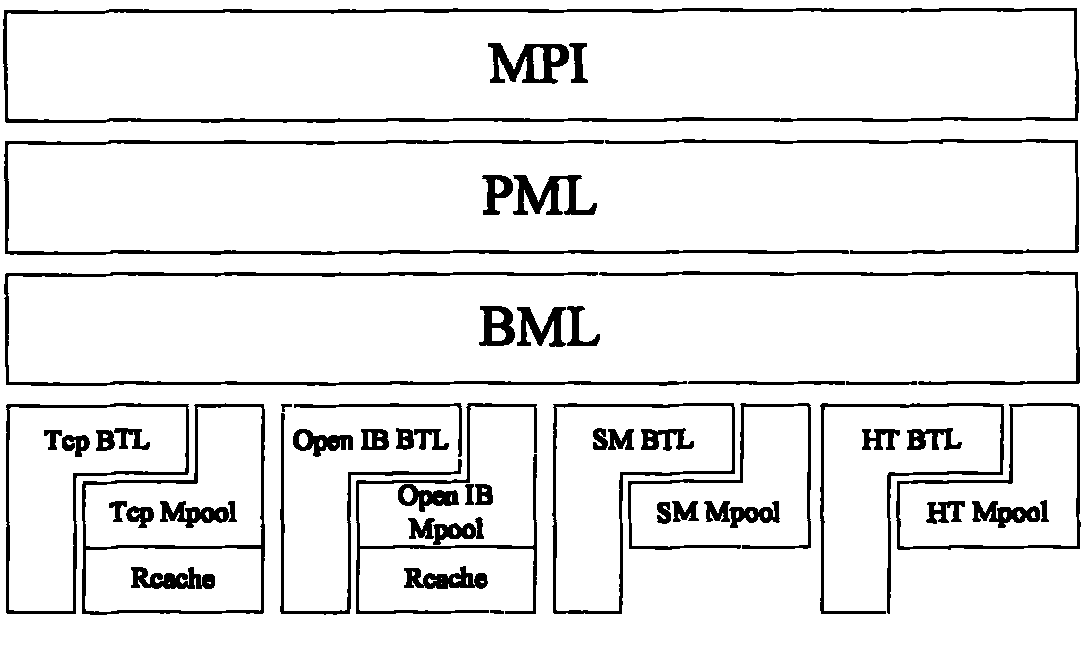

The invention discloses a message passing interface framework for supporting bus communication, which comprises a byte transfer layer (BTL) in a basic framework of Open MPI open source software, a byte management layer (BML), a point-to-point messaging layer (PML), an MPI application program interface (MPI API), a memory pool (Mpool) and a registration cache (Rcache). The framework also comprises an HT bus communication module (HT BTL) added based on the framework and a called corresponding memory pool (Mpool) in an Open MPI architecture; and communication can be performed in the same or different operating systems of a main board and between different main boards by collocating the priority of an HT BTL module. A Hypertransport bus communication protocol is integrated into the Open MPI architecture by combining a system calling interface provided by the Hypertransport bus communication protocol according to a standard interface provided by the Open MPI open source software. Meanwhile, during MPI process communication, a network using the Hypertransport bus communication protocol has higher priority than other networks. The message passing interface framework for supporting bus communication is innovated based on the conventional mature technology, is simple and convenient to implement, and has good use and development prospect.

Owner:BEIHANG UNIV

Bridge, computer system and method for initialization

An indicator pin of an input / output controller is used to identifying whether a processor or a bridge is configured in a processor. When a predetermined voltage level of the indicator pin is confirmed, a base input / output system of the computer system renews a coherent / non-coherent HyperTransport link table. Then an initialization procedure is performed in accordance with the renewed coherent / non-coherent HyperTransport link table.

Owner:MITAC INT CORP

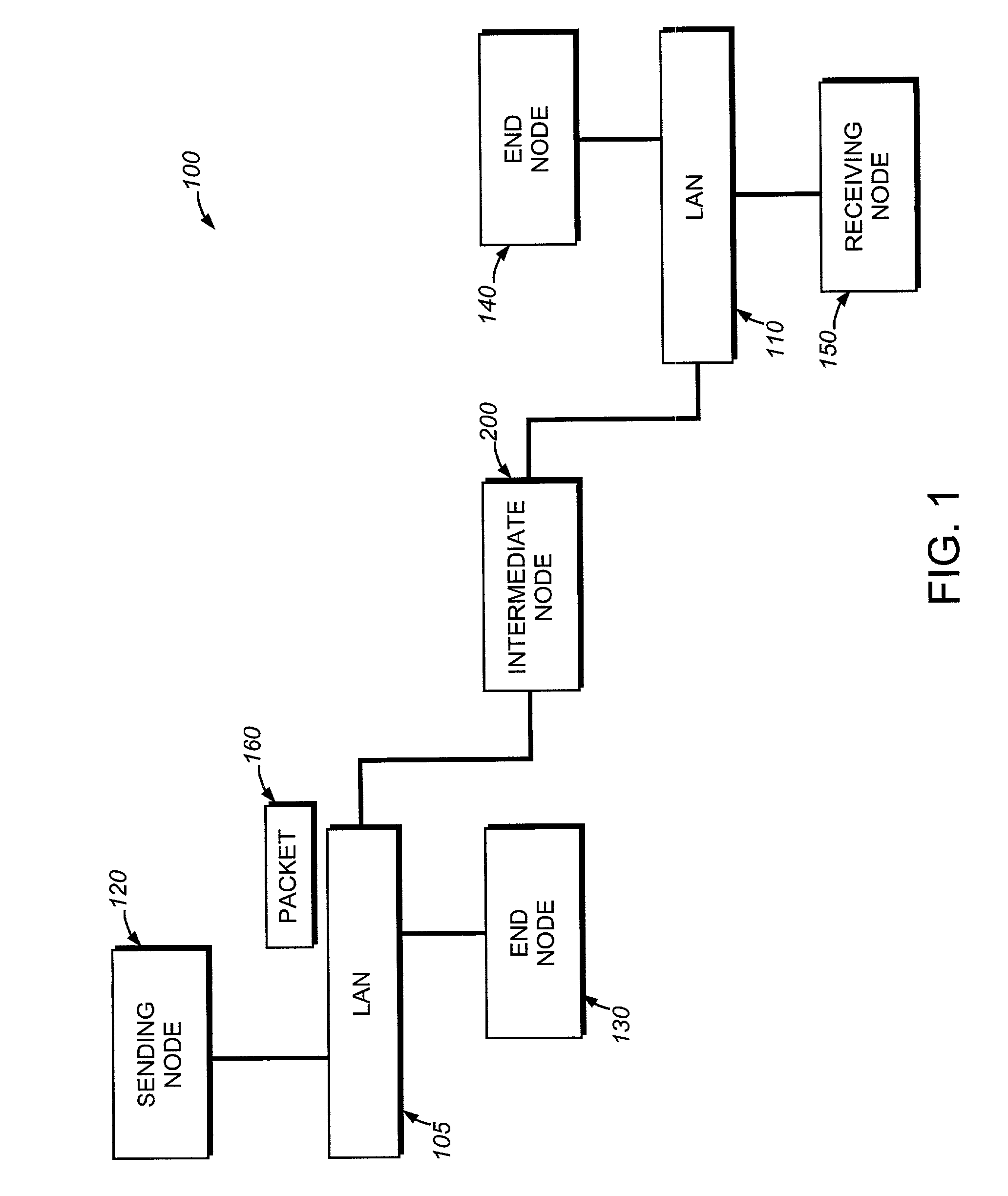

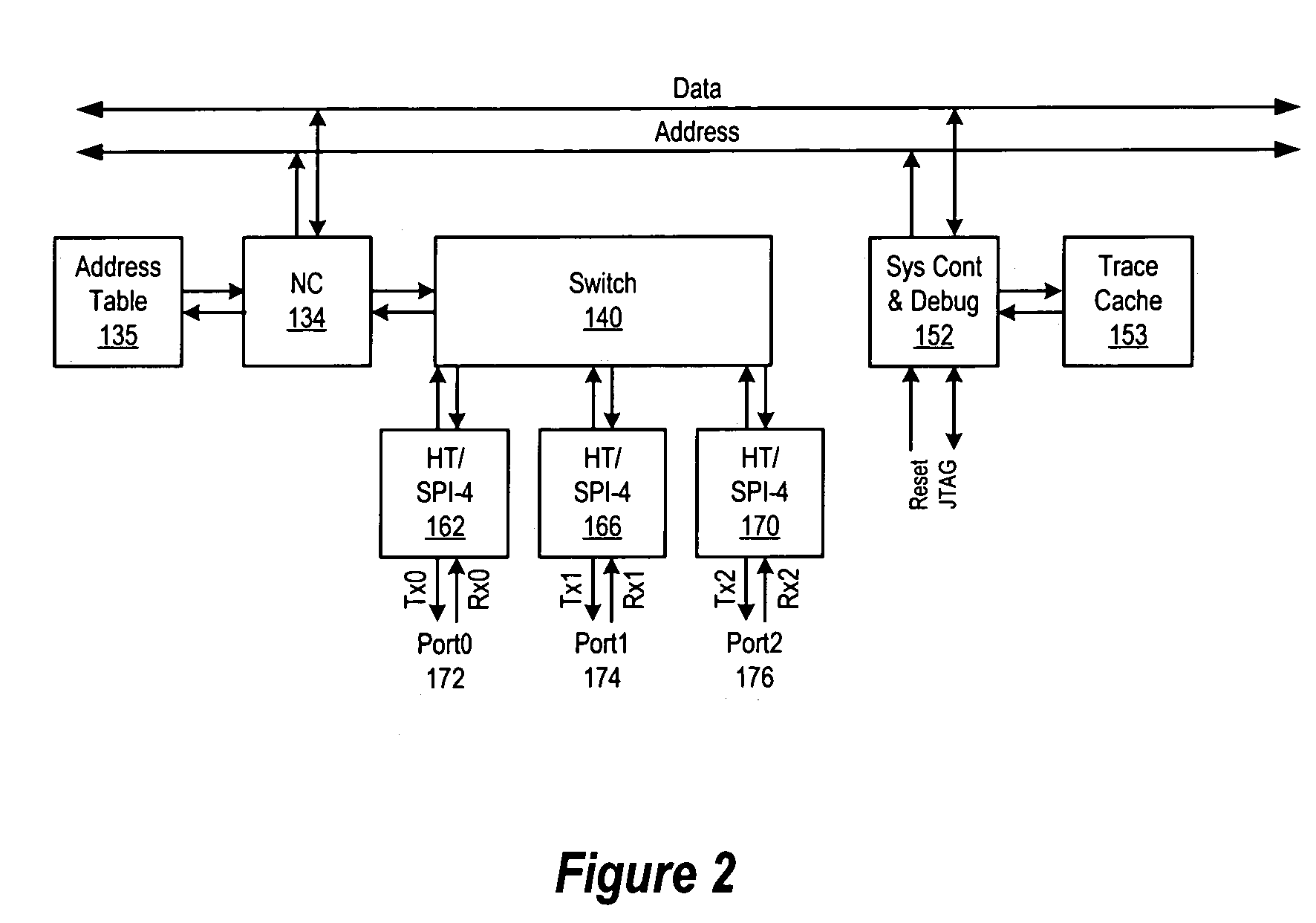

Distributed copies of configuration information using token ring

InactiveUS20050080941A1Multiple digital computer combinationsGenerating/distributing signalsData processing systemTransmission protocol

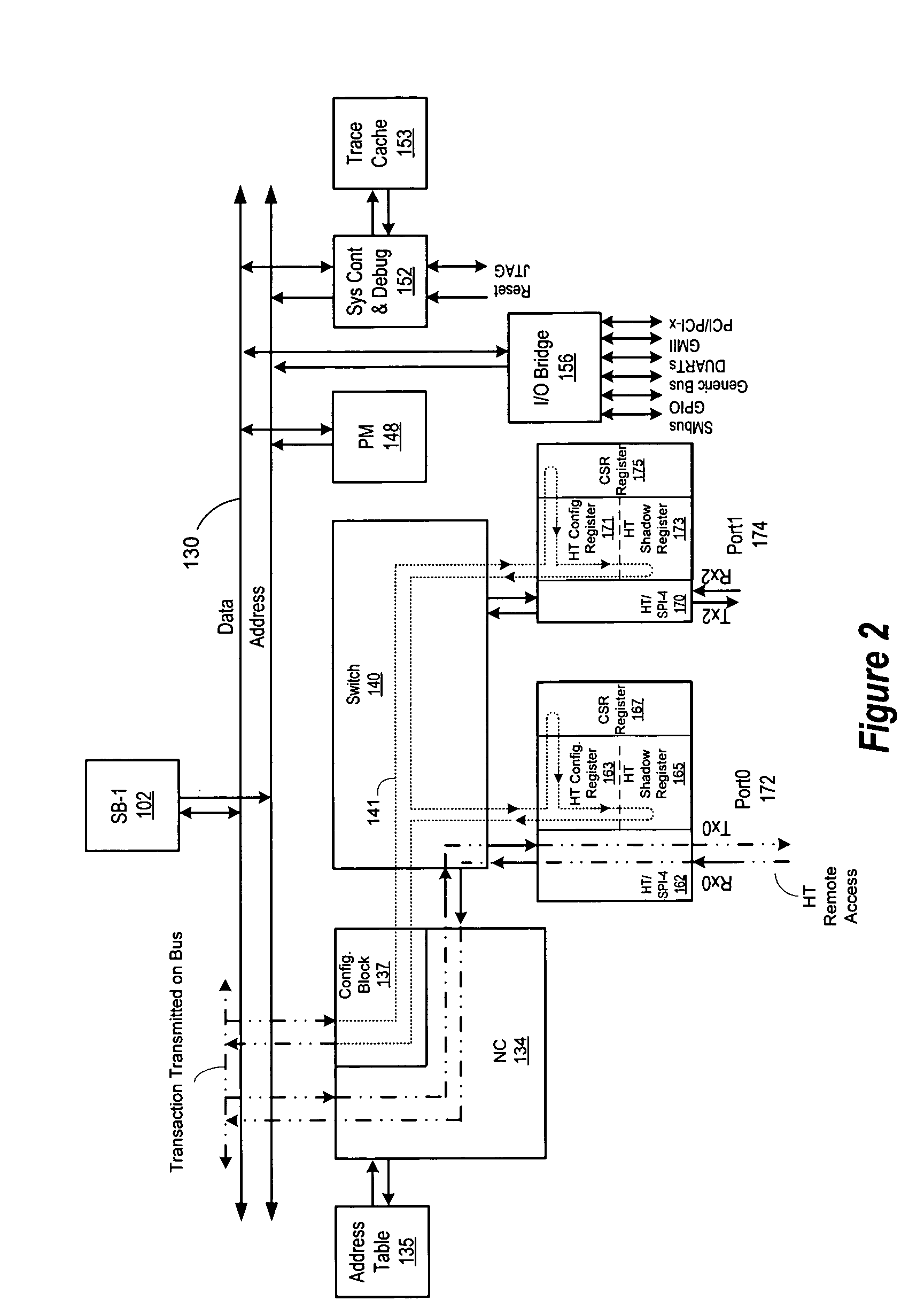

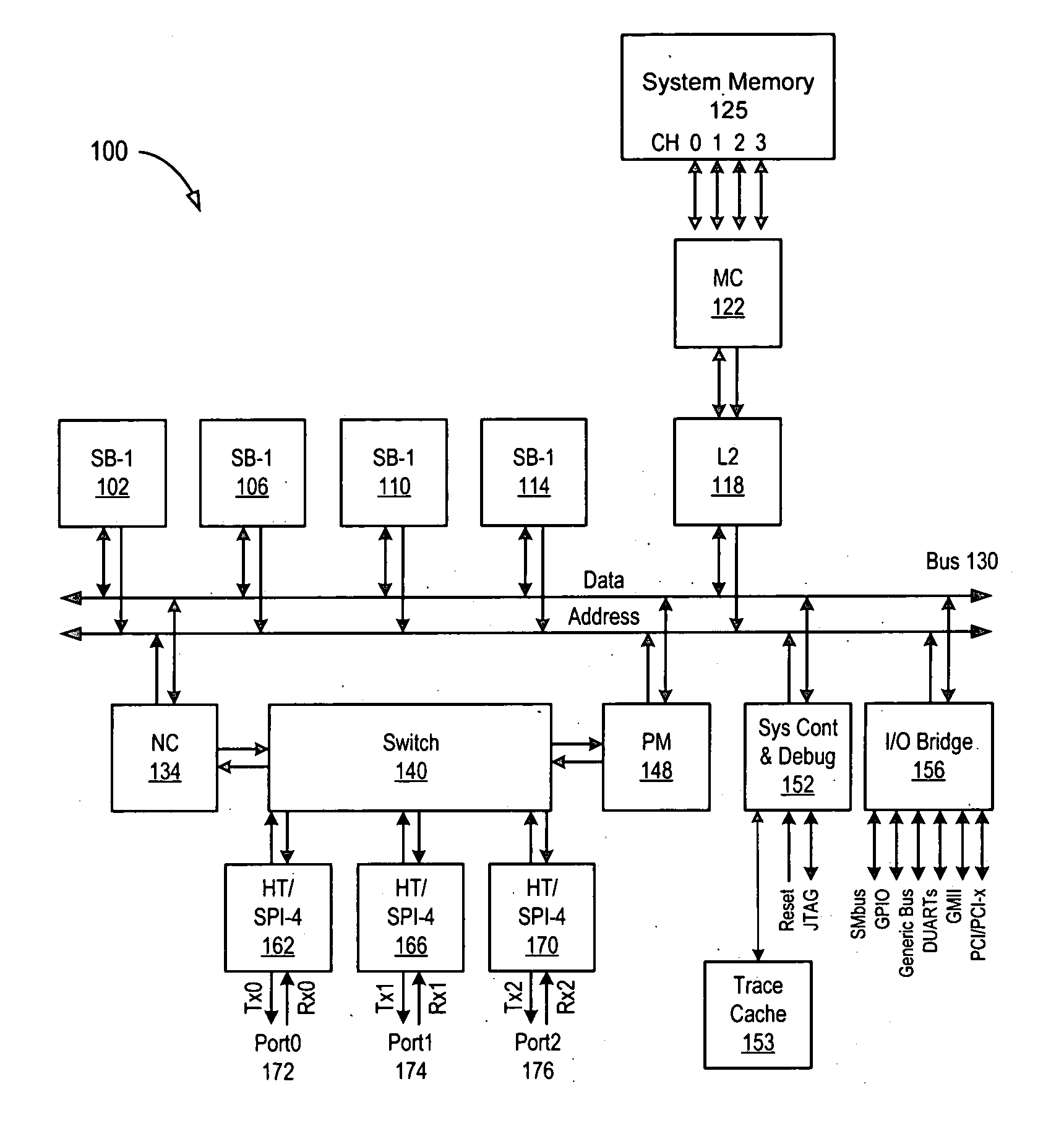

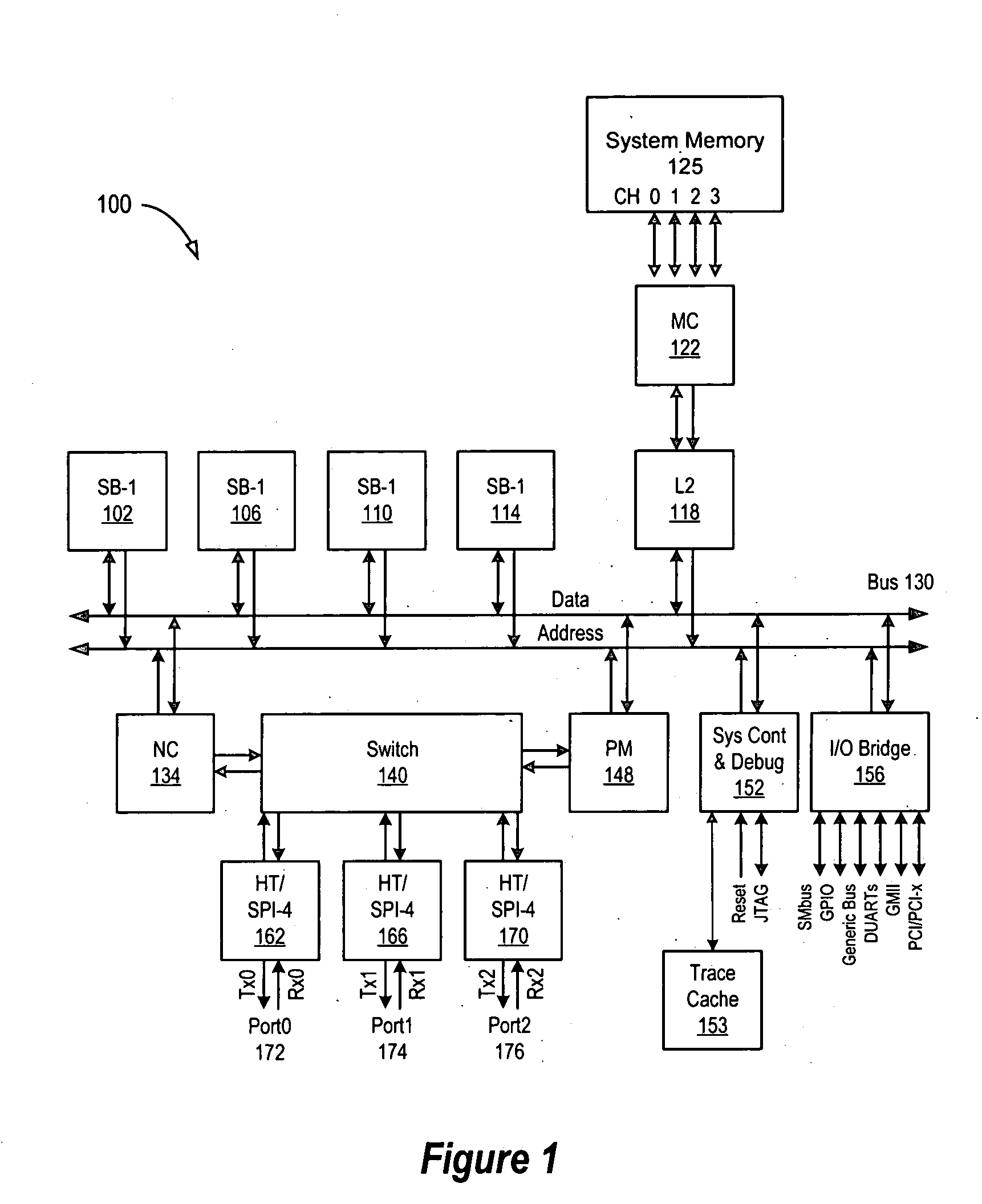

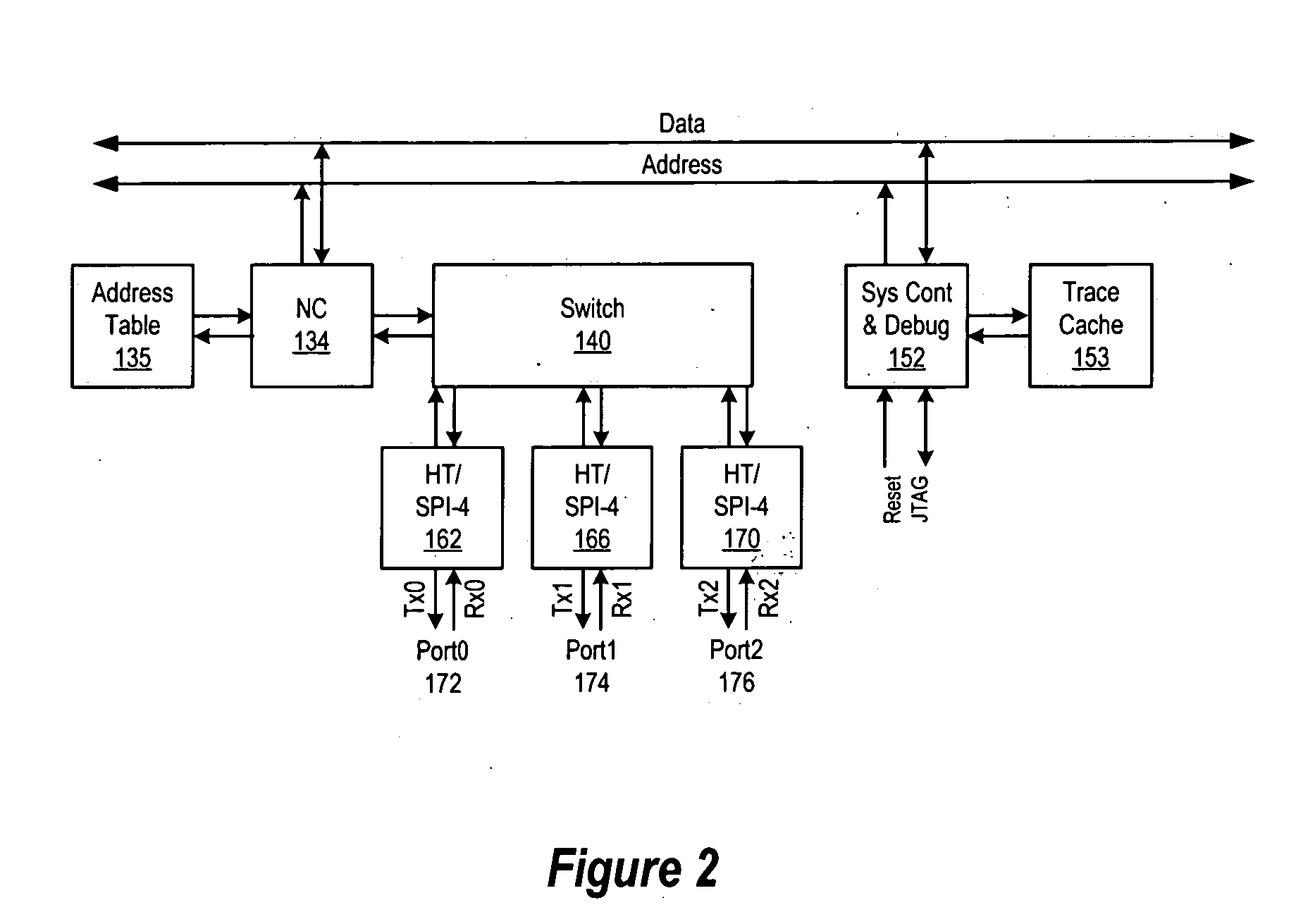

A system for synchronizing configuration information in a plurality of data processing devices using a common system interconnect bus. The present invention provides a method and apparatus for enforcing automatic updates to the configuration registers in various agents in the data processing system. The interface agent are not required to have target / response logic to respond to internal and external configuration accesses. In and embodiment of the present invention, a node controller, which may comprise a configuration block, is operably connected to a system interconnect bus and a switch. A plurality of interface agents are connected to the switch, with each of the interface agents comprising a configuration space register, a configuration space shadow register and a control and status register (CSR). A token ring connected to the node controller is operable to transmit data from the node controller to a plurality of interface agents connected to the token ring, thereby providing a system for updating the various configuration registers in each of the agents. A transaction from an interface agent is transferred to the node controller which transfers the transaction onto the system interconnect bus. The transaction on the system interconnected bus is detected by the configuration block of the node controller and is then transmitted on the token ring to each of the agents connected thereto. The information transmitted on the token ring is used to update the information in the configuration space registers and configuration space shadow registers of each of the agents connected to the token ring. In an embodiment of the invention the interface agents are configured in accordance with the Hypertransport protocol. In this embodiment, the configuration comprises a HT configuration space register and the configuration space shadow register comprise a HT configuration space shadow register.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

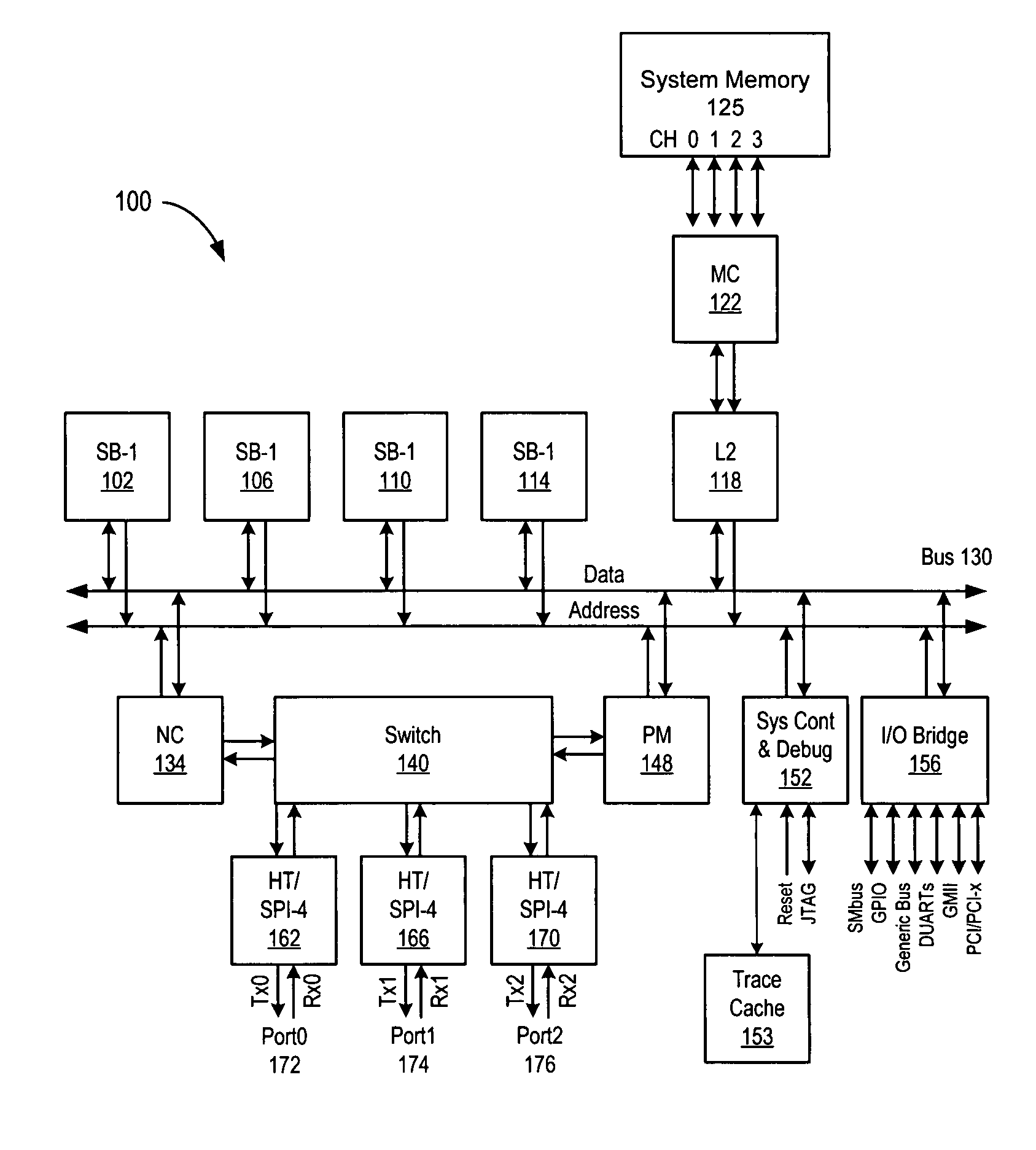

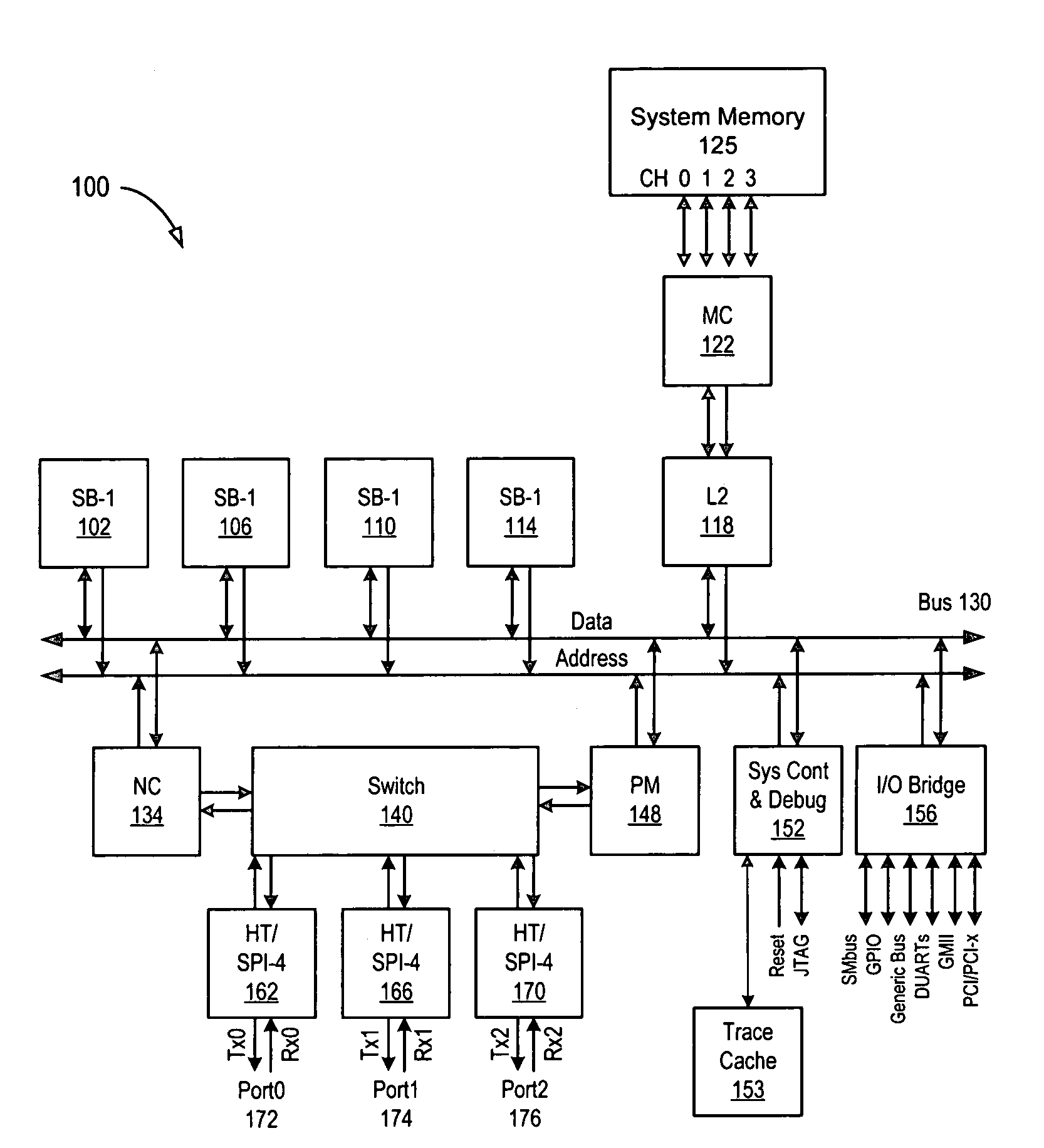

Hypertransport exception detection and processing

In accordance with the present invention a system for detecting transaction errors in a system comprising a plurality of data processing devices using a common system interconnect bus, comprises a node controller operably connected to said system interconnect bus and a plurality of interface agents communicatively coupled to said node controller. Error corresponding to transactions between said interface agents and other processing modules in said system are directed to said node controller; and wherein transaction errors that would not normally be communicated to said system interconnect bus are communicated by said node controller to said system interconnect bus to be available for detection. In an embodiment of the present invention, the interface agents operate in accordance with the hypertransport protocol. A system control and debug unit and a trace cache operably connected to the system bus can be used to diagnose and store errors conditions.

Owner:AVAGO TECH INT SALES PTE LTD

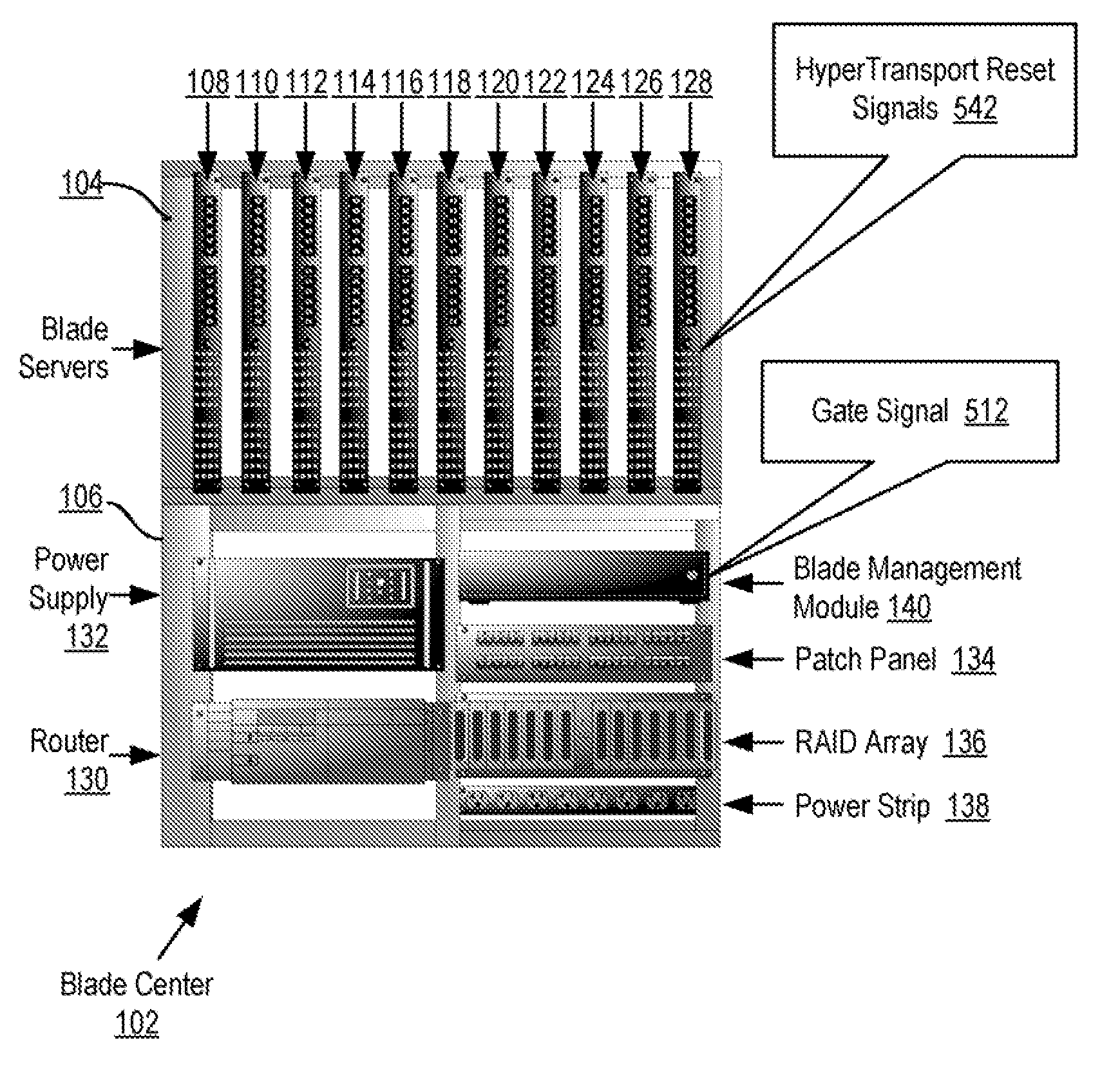

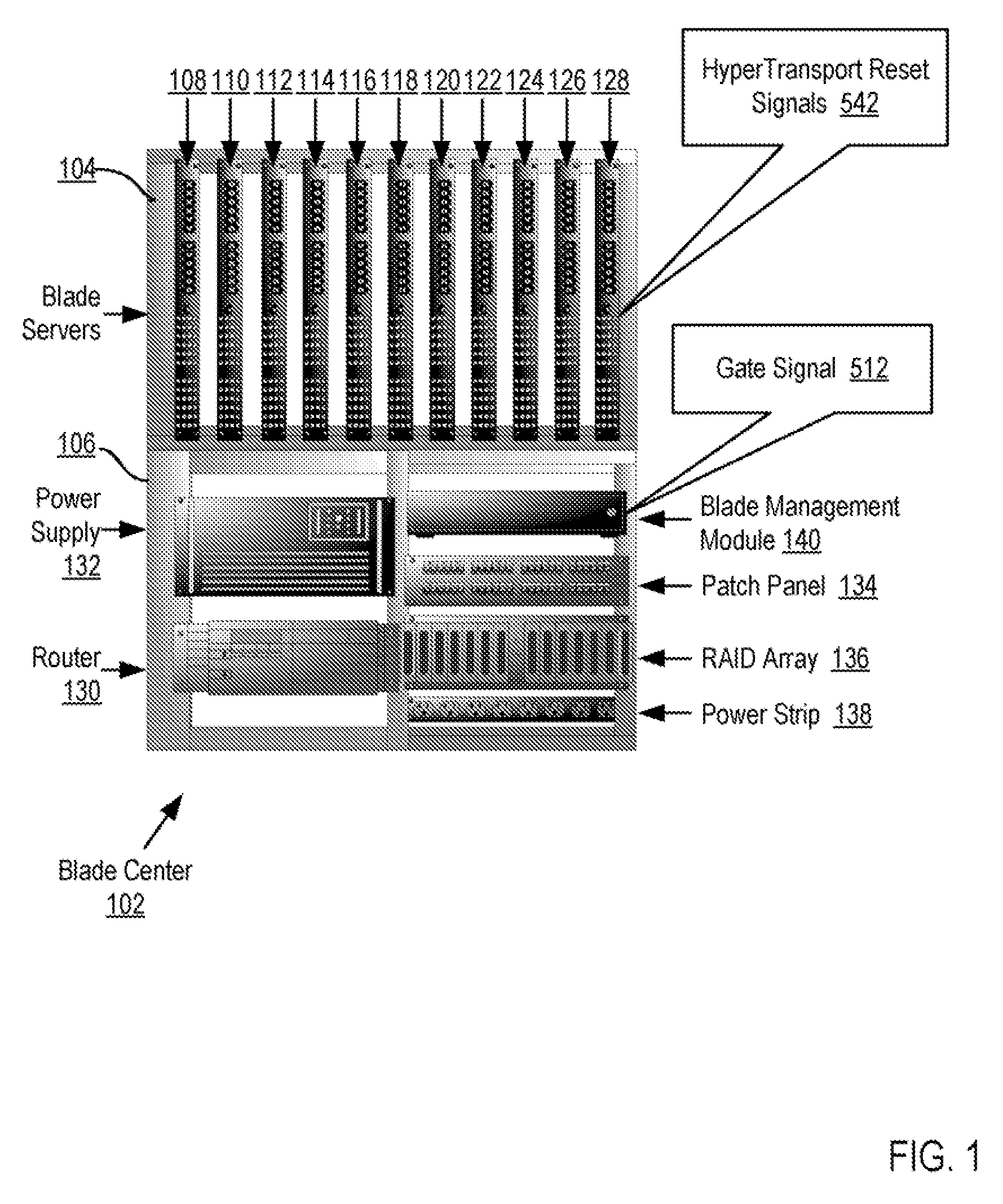

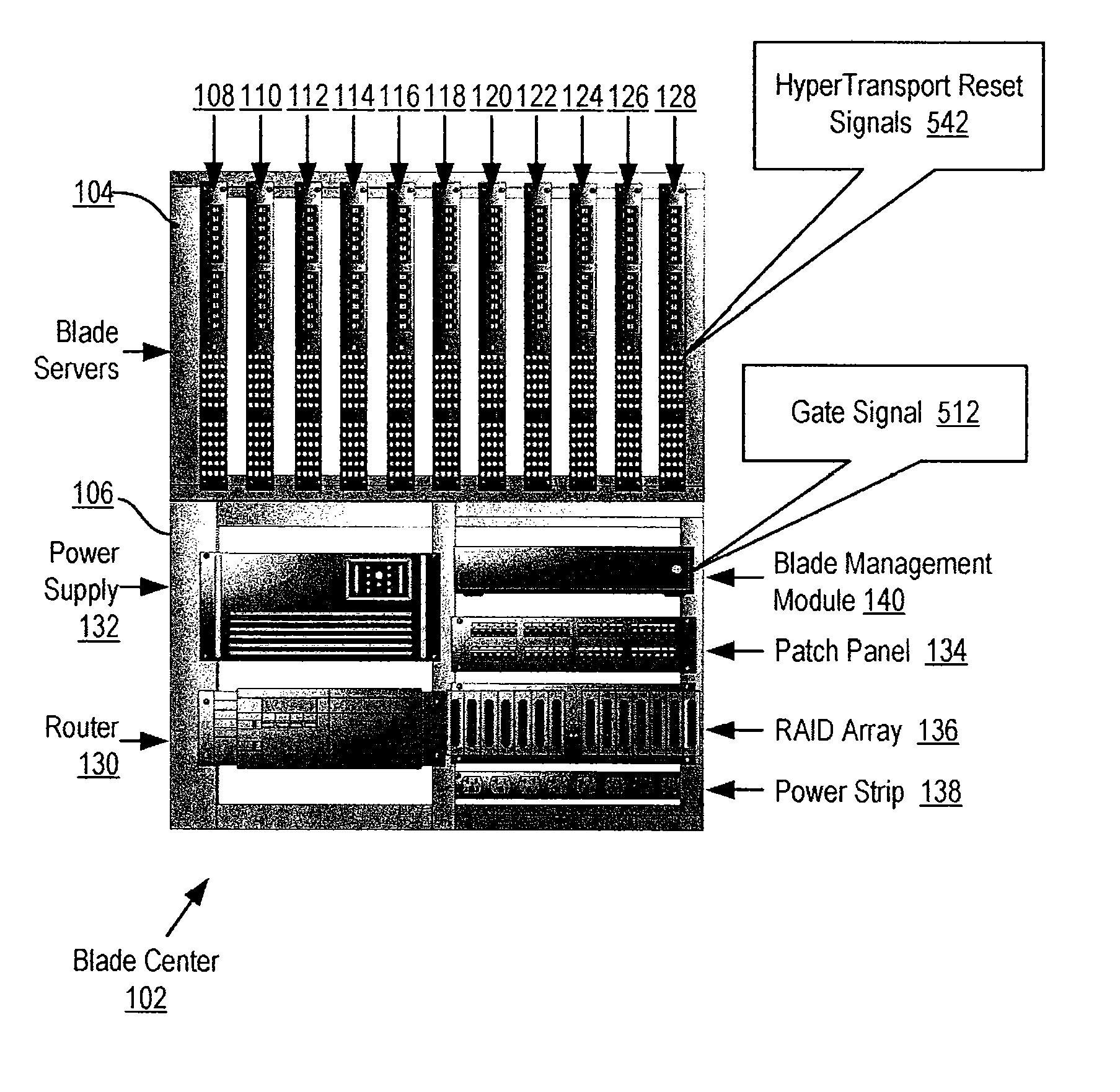

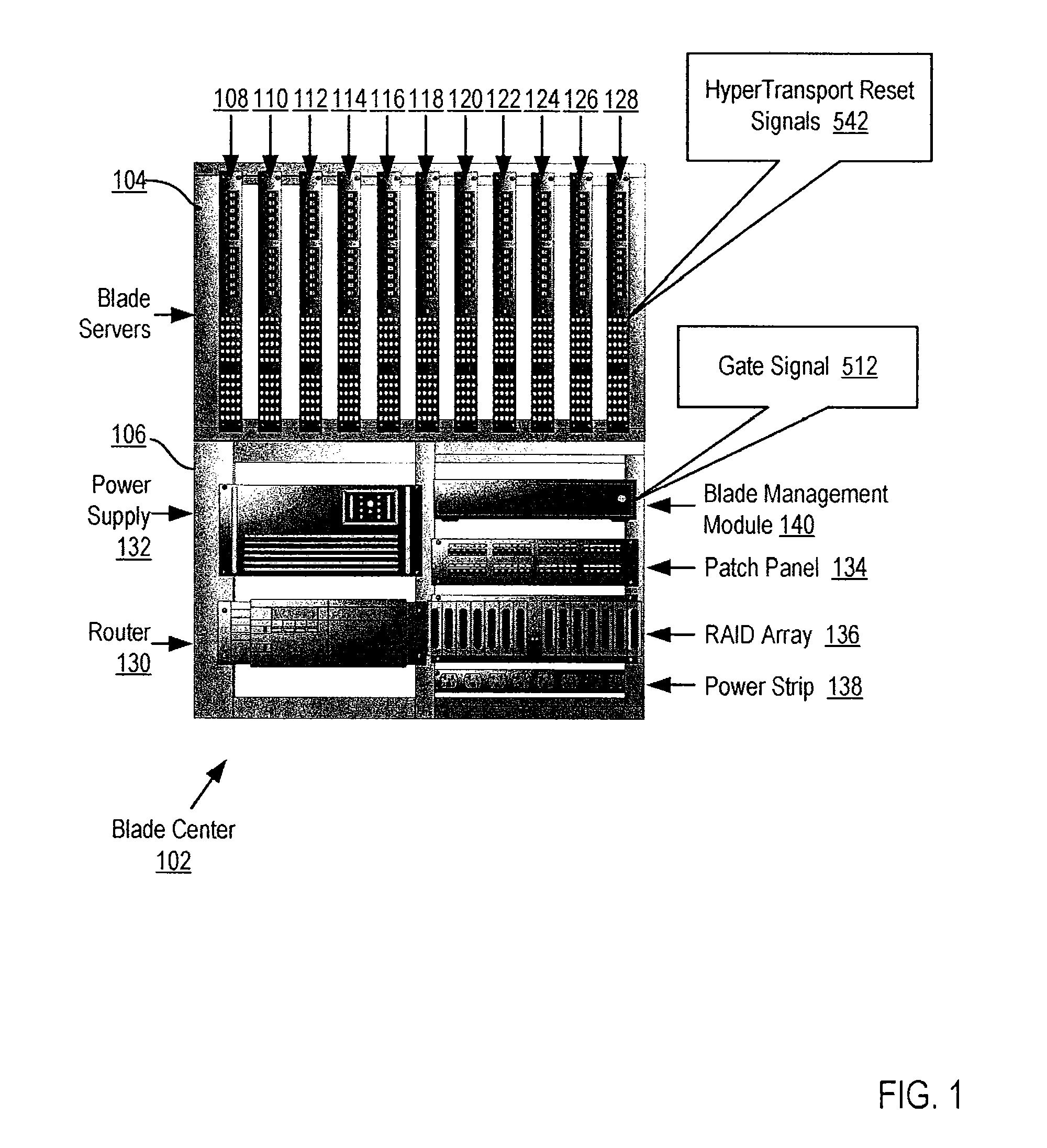

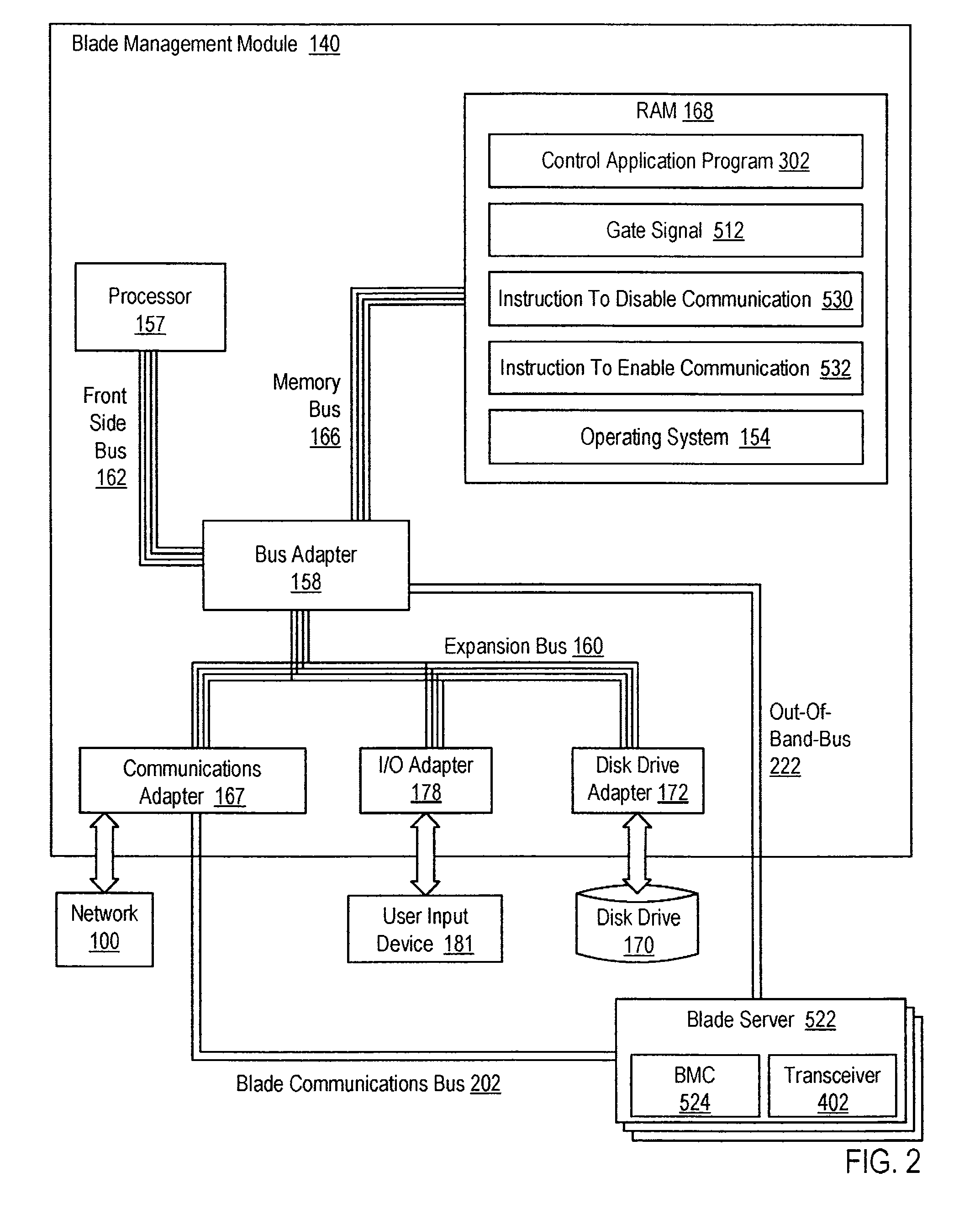

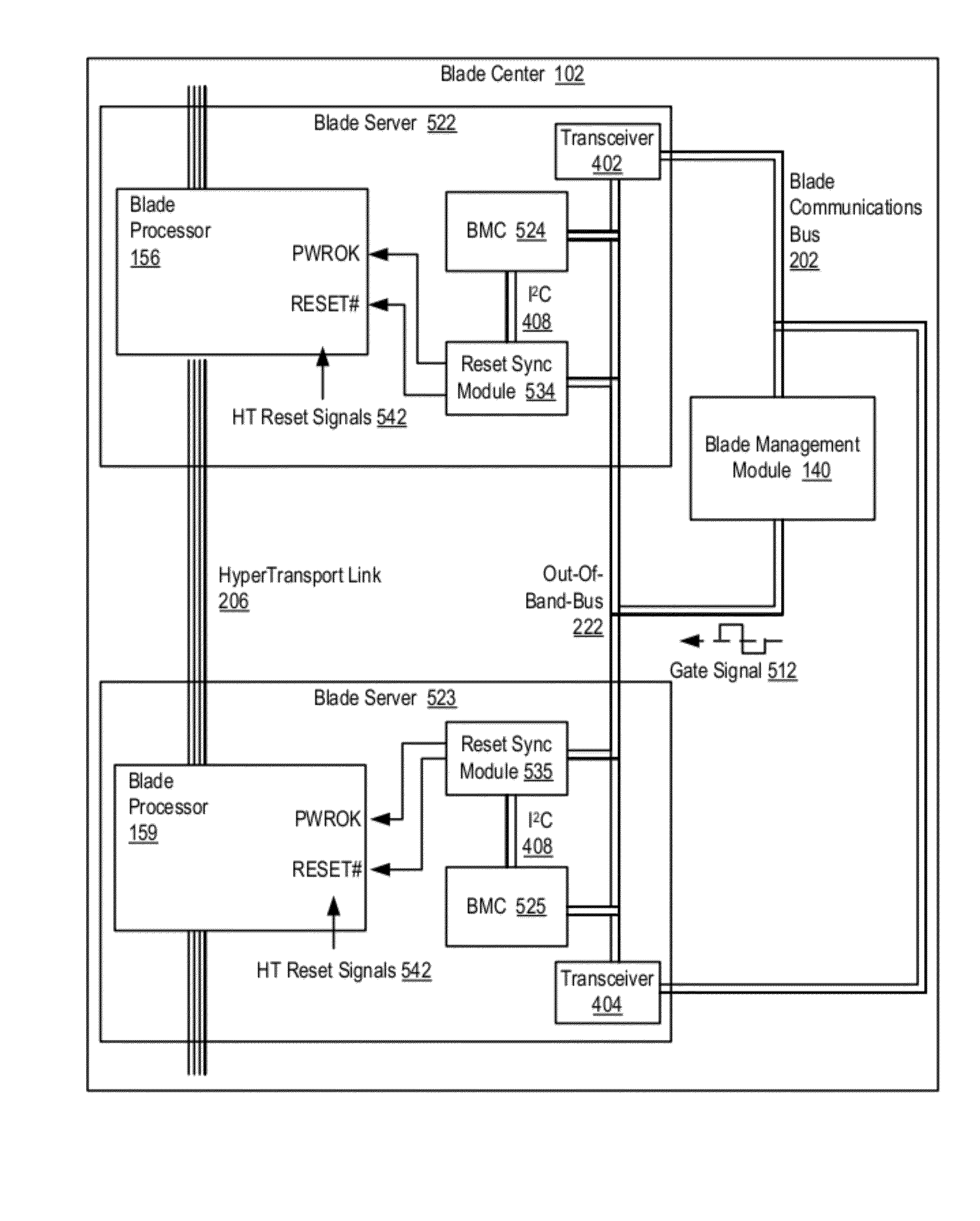

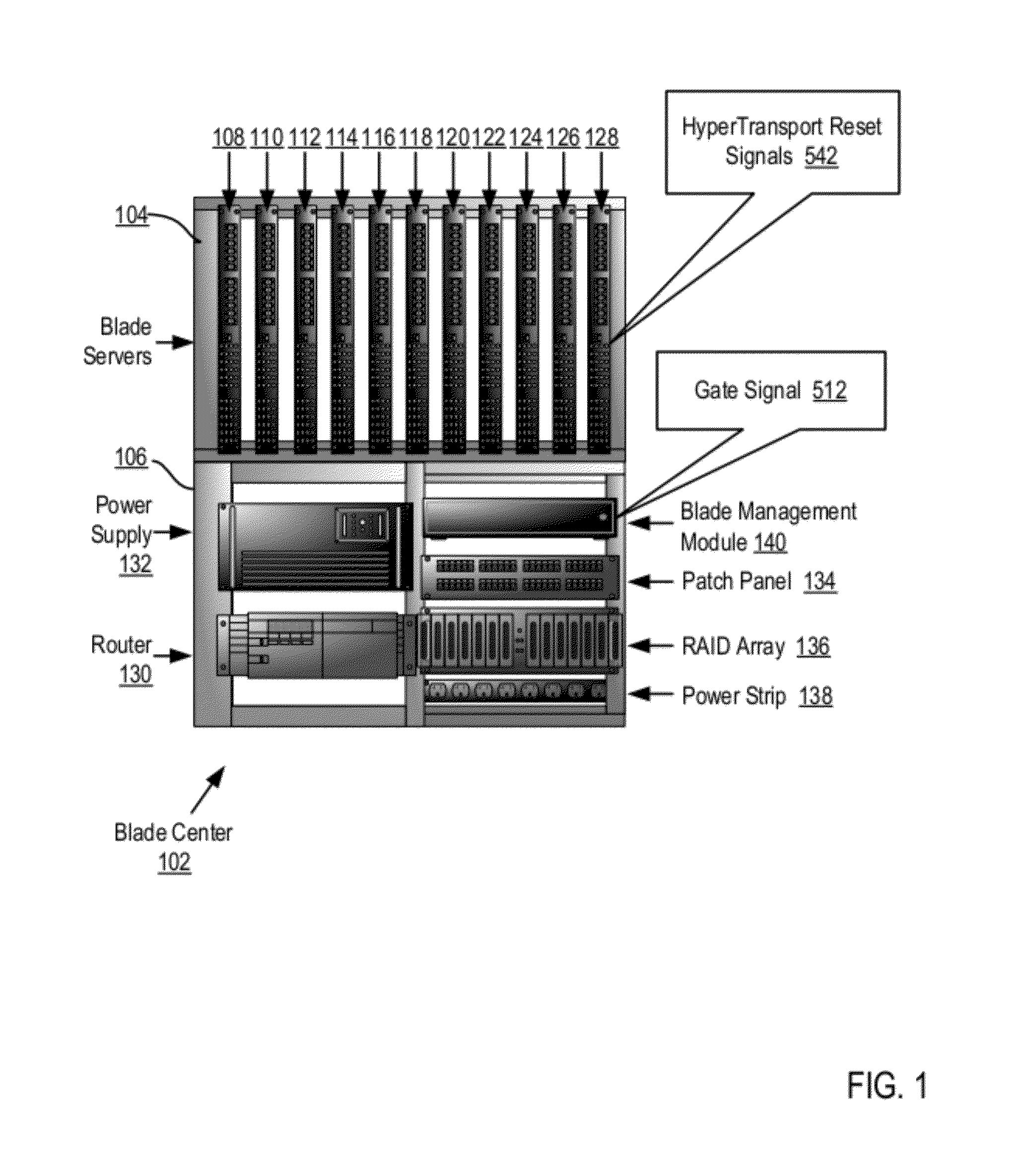

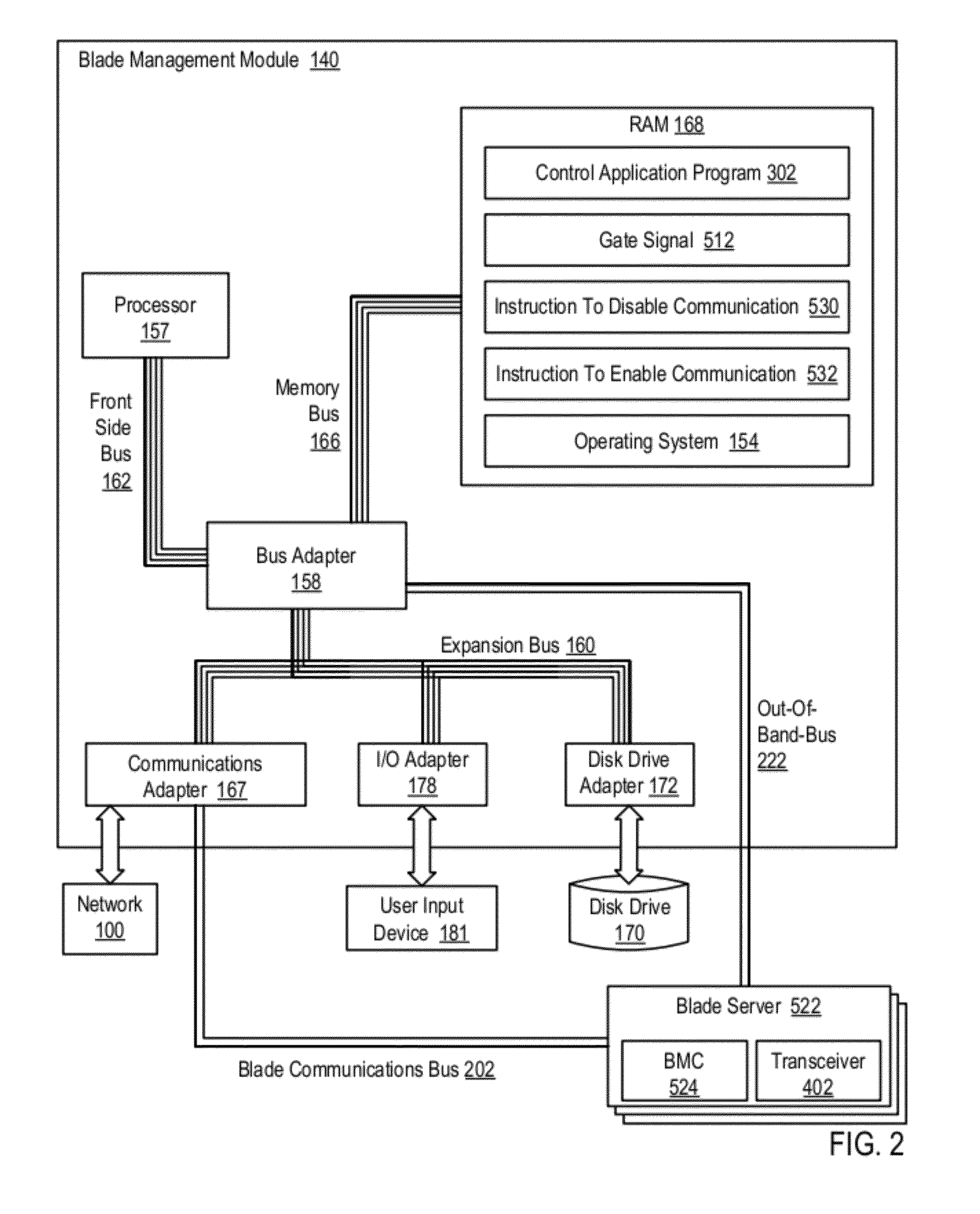

Resetting a Hypertransport Link in a Blade Server

Methods, apparatus, and computer program products are described for resetting a HyperTransport link in a blade server, including reassigning, by a blade management module, a gate signal from enabling a transceiver to signaling a HyperTransport link reset; sending, by the blade management module to a reset sync module on an out-of-band bus, the gate signal; and in response to the gate signal, sending, by the reset sync module to the blade processor, HyperTransport reset signals. The HyperTransport link includes a bidirectional, serial / parallel, high-bandwidth, low-latency, point to point data communications link. The blade server includes the blade processor, the reset sync module, and the baseboard management controller. The blade server is installed in the blade center. The blade center includes the blade management module. The blade management module is coupled to the baseboard management controller by the blade communication bus.

Owner:LENOVO GLOBAL TECH INT LTD

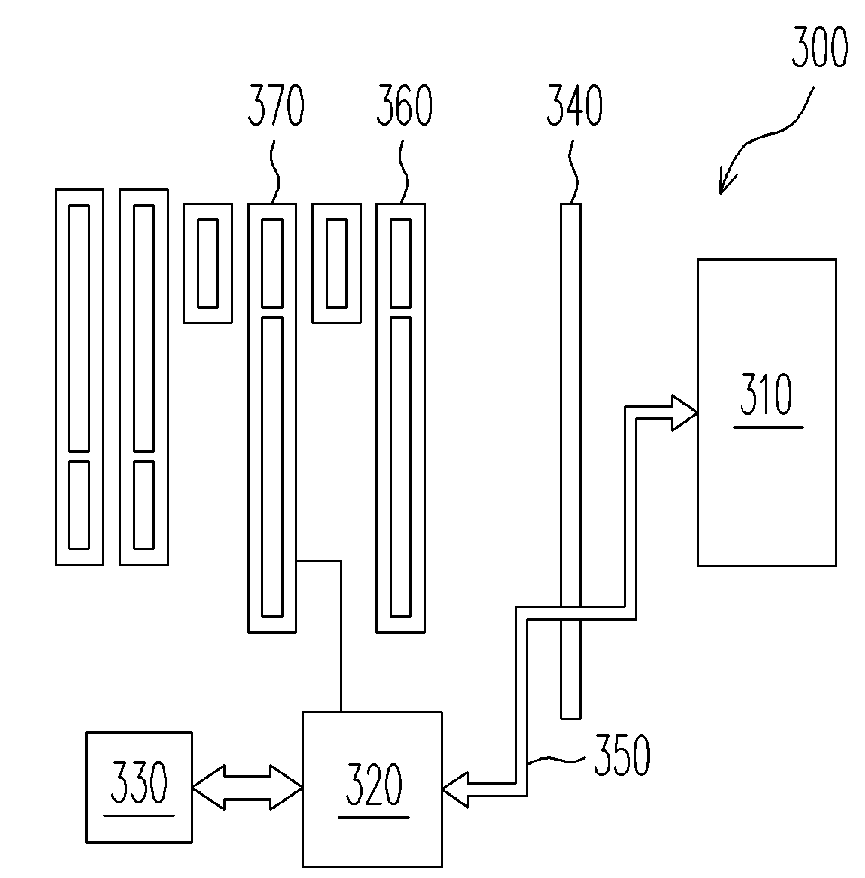

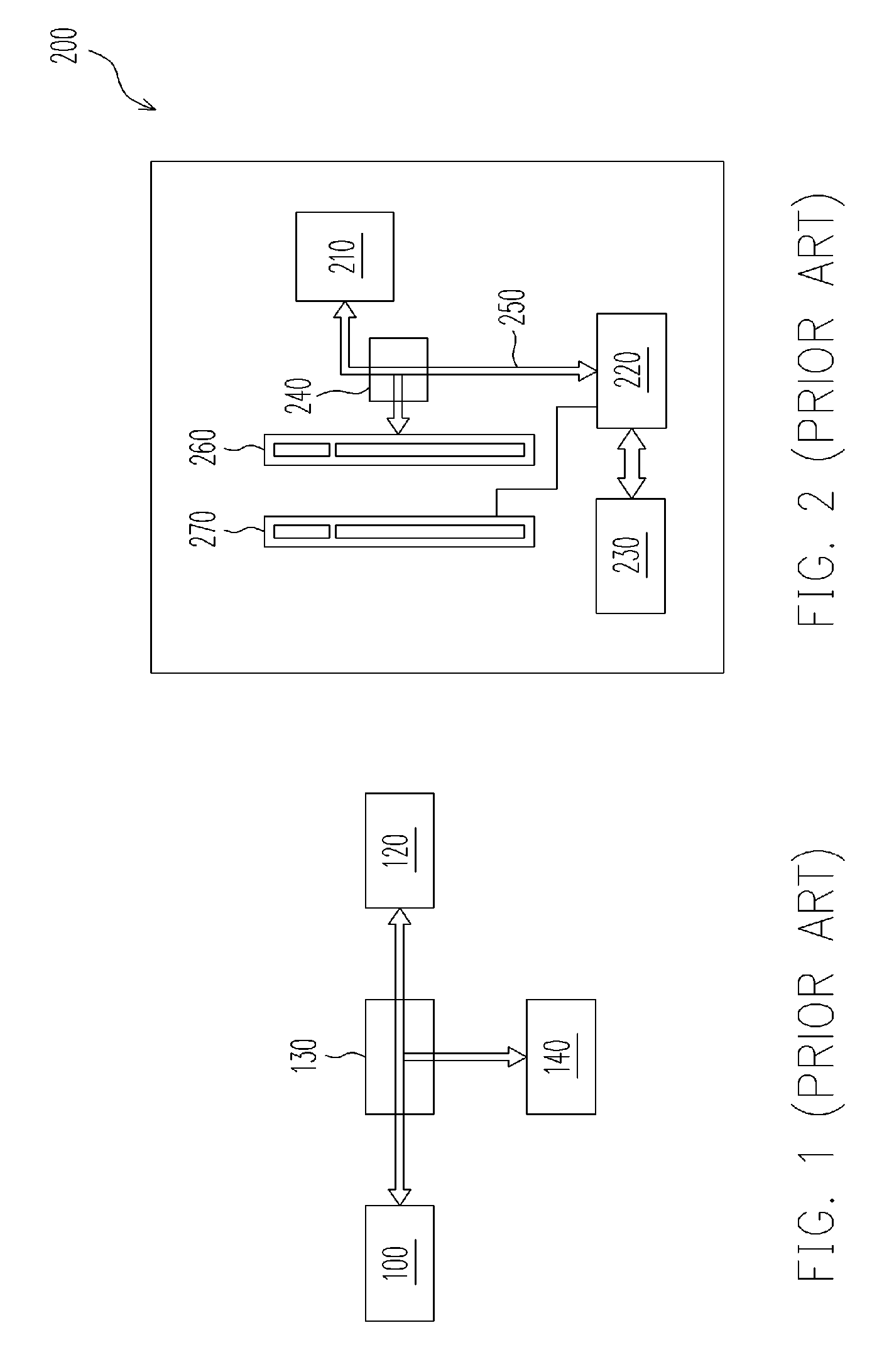

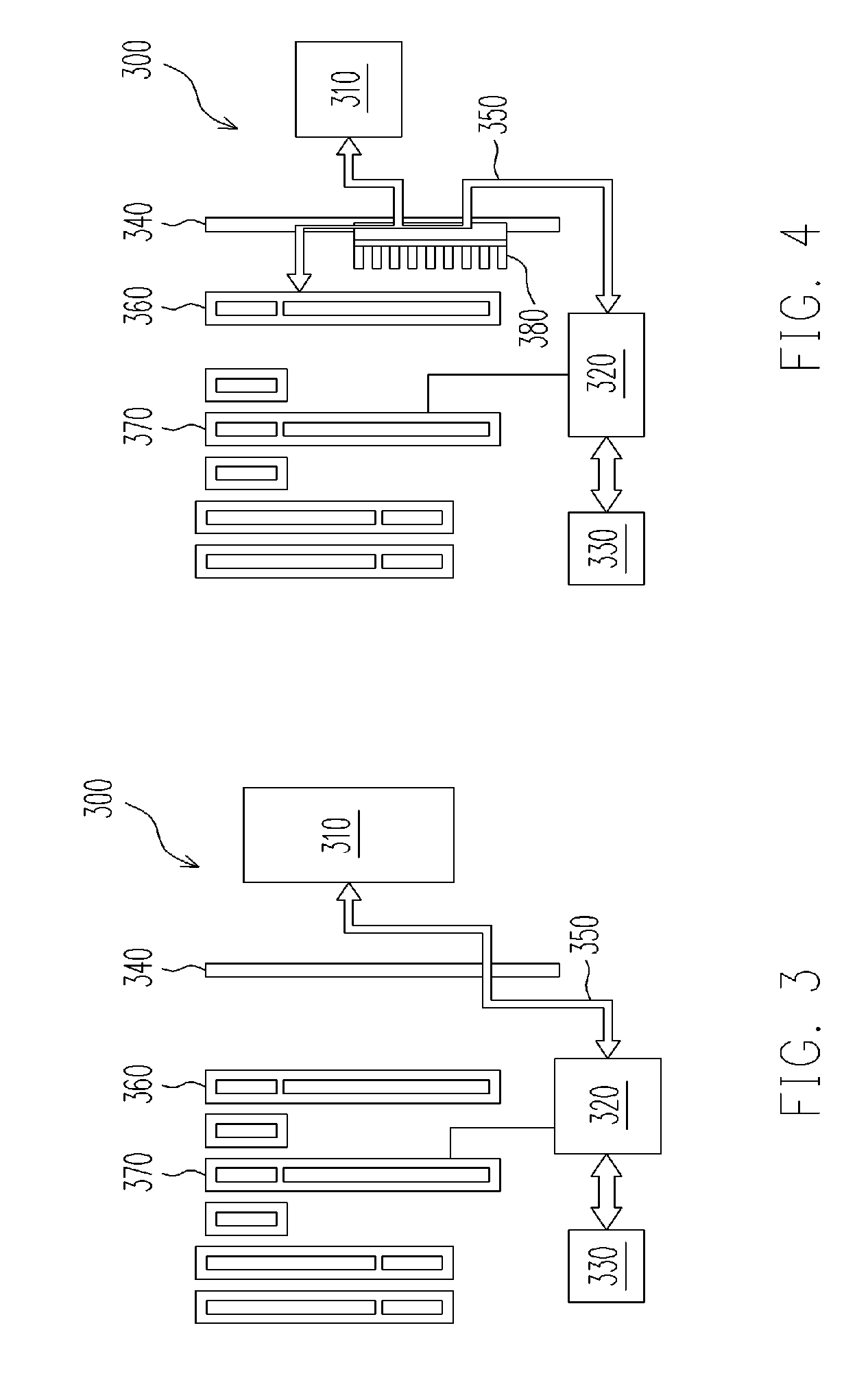

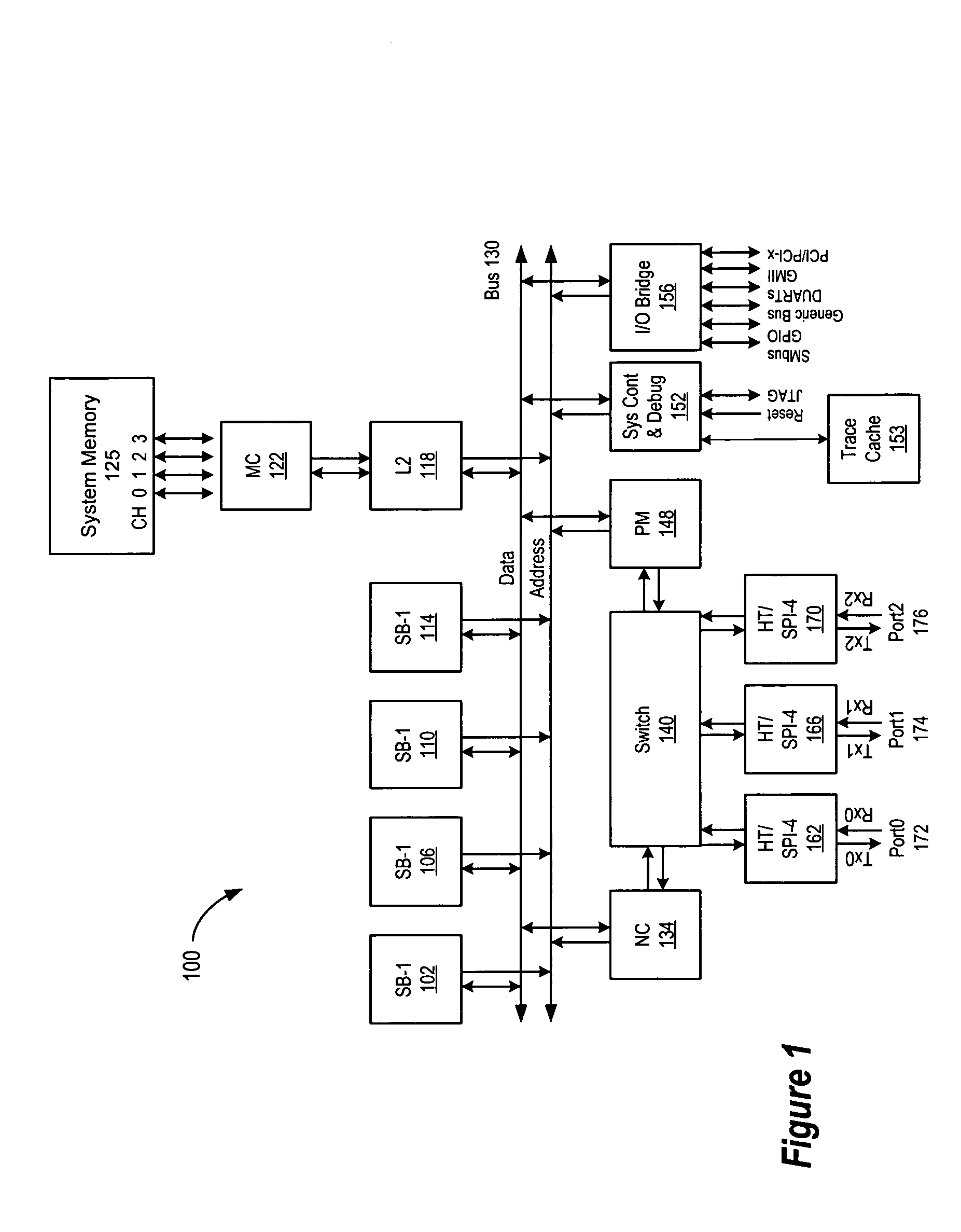

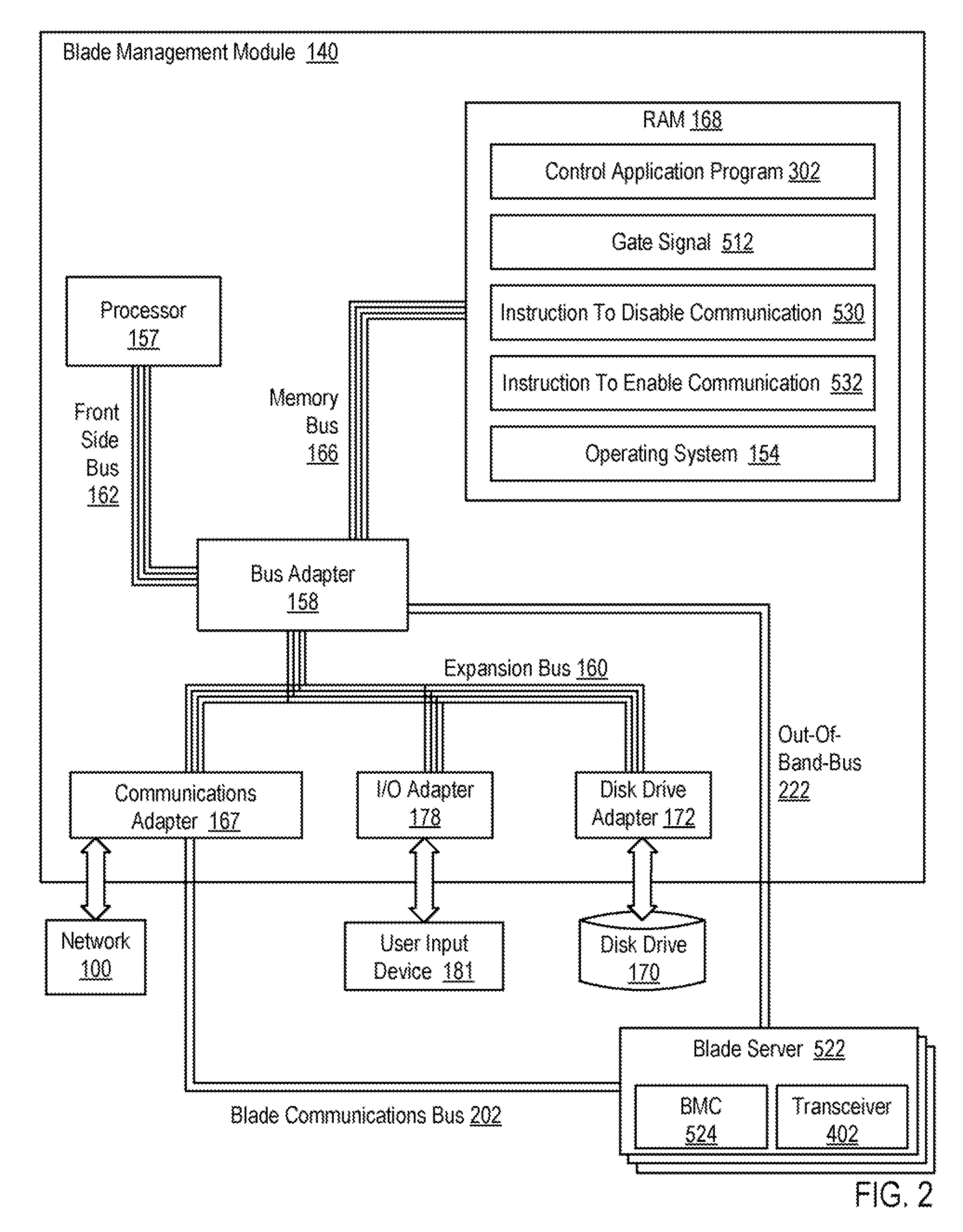

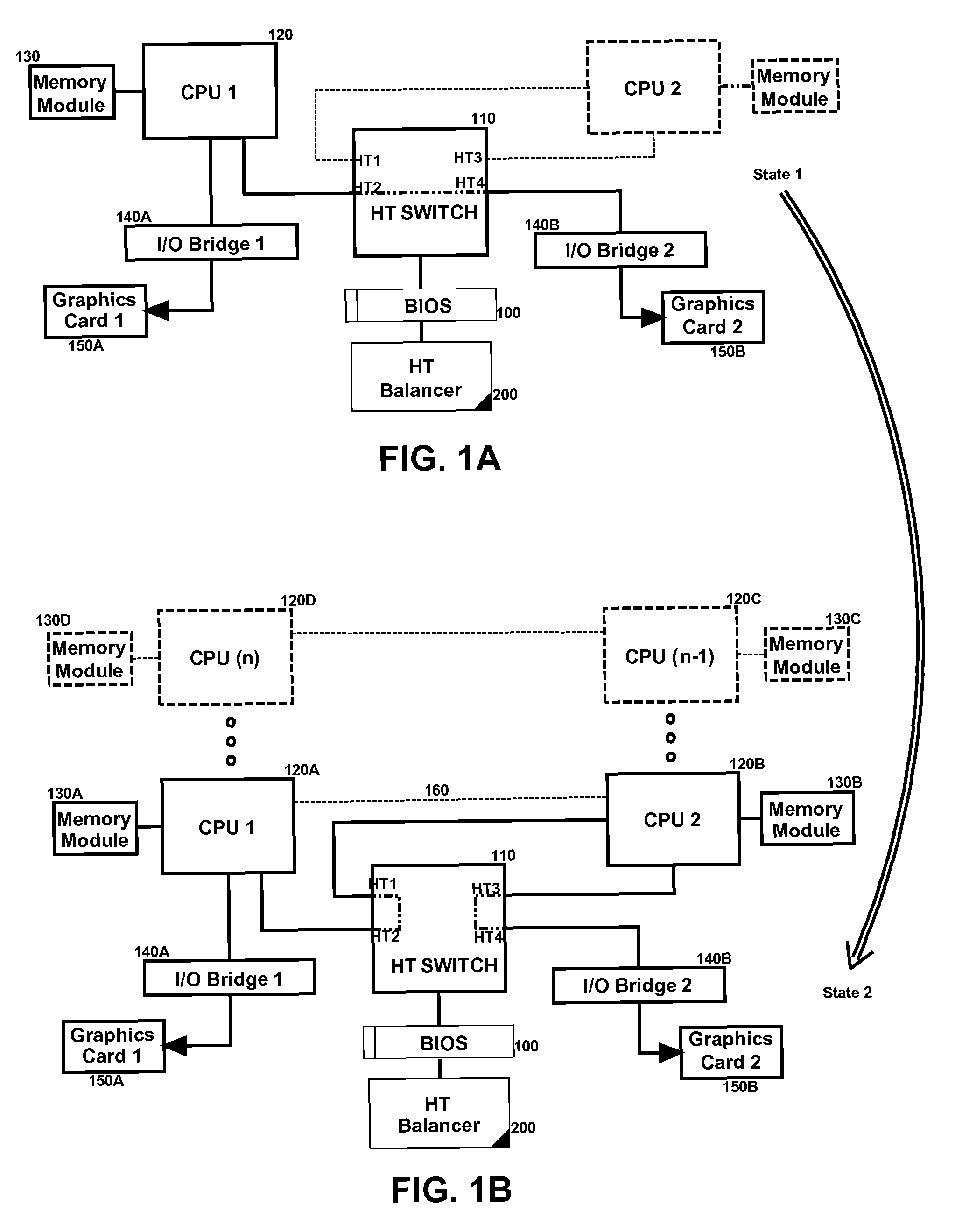

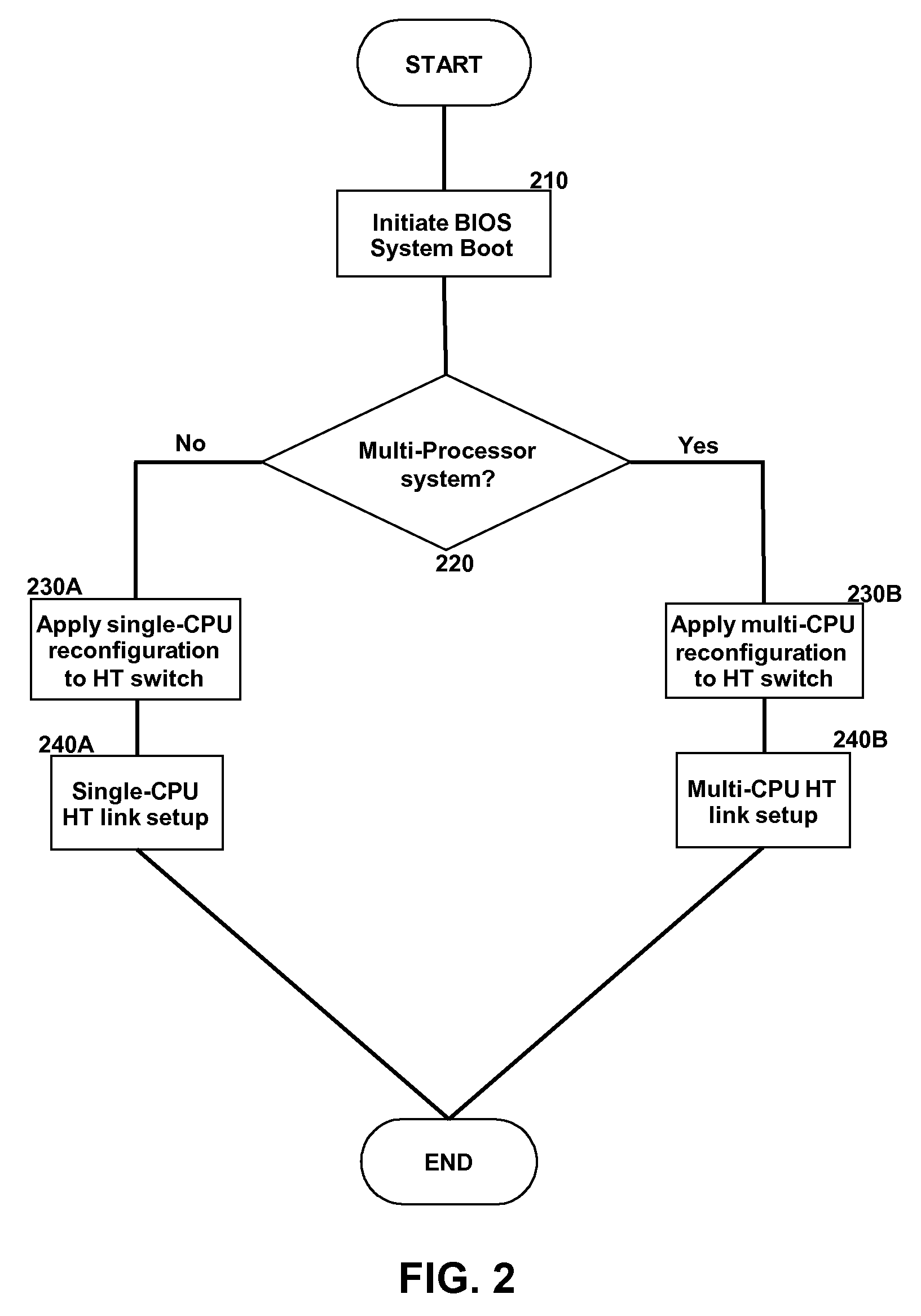

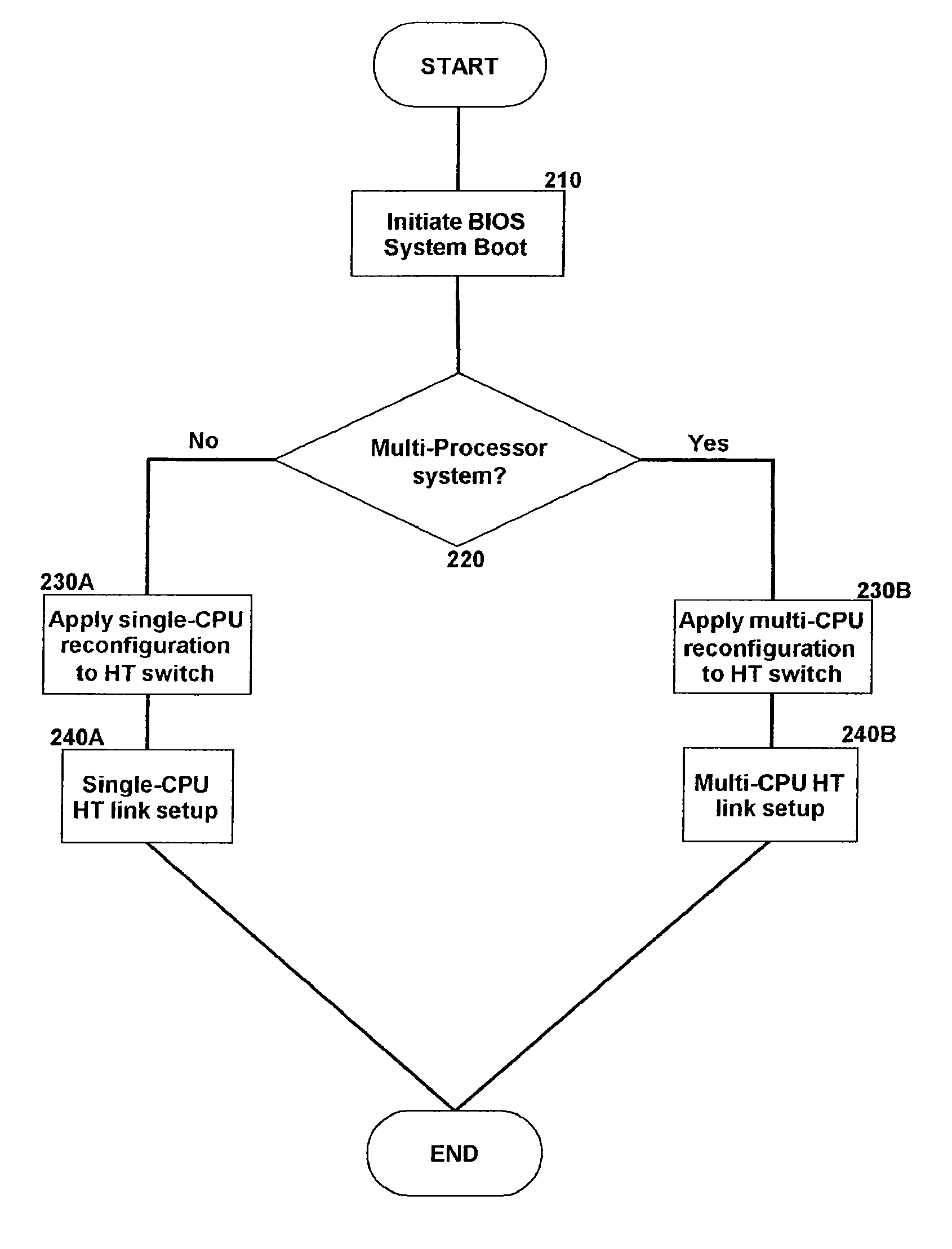

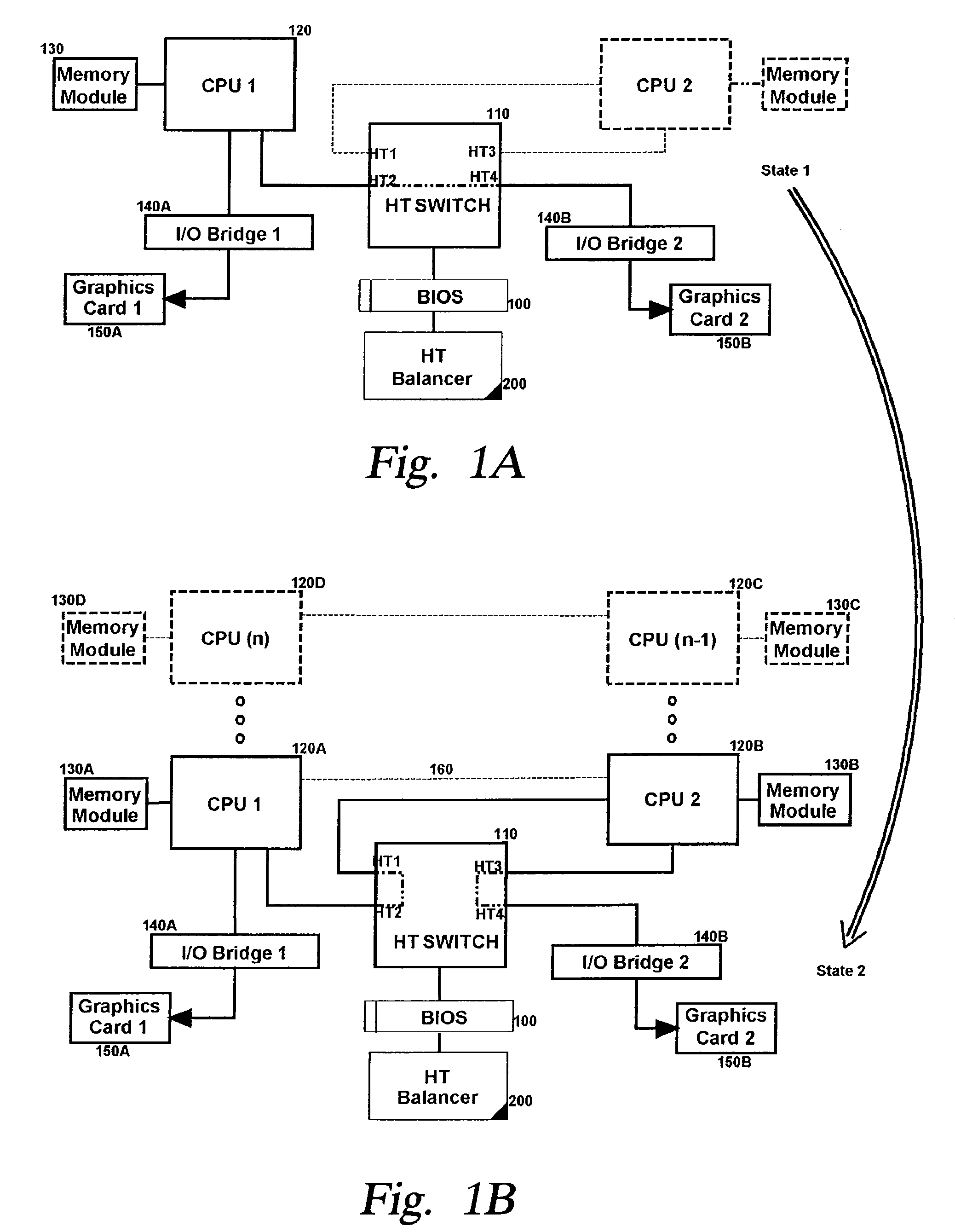

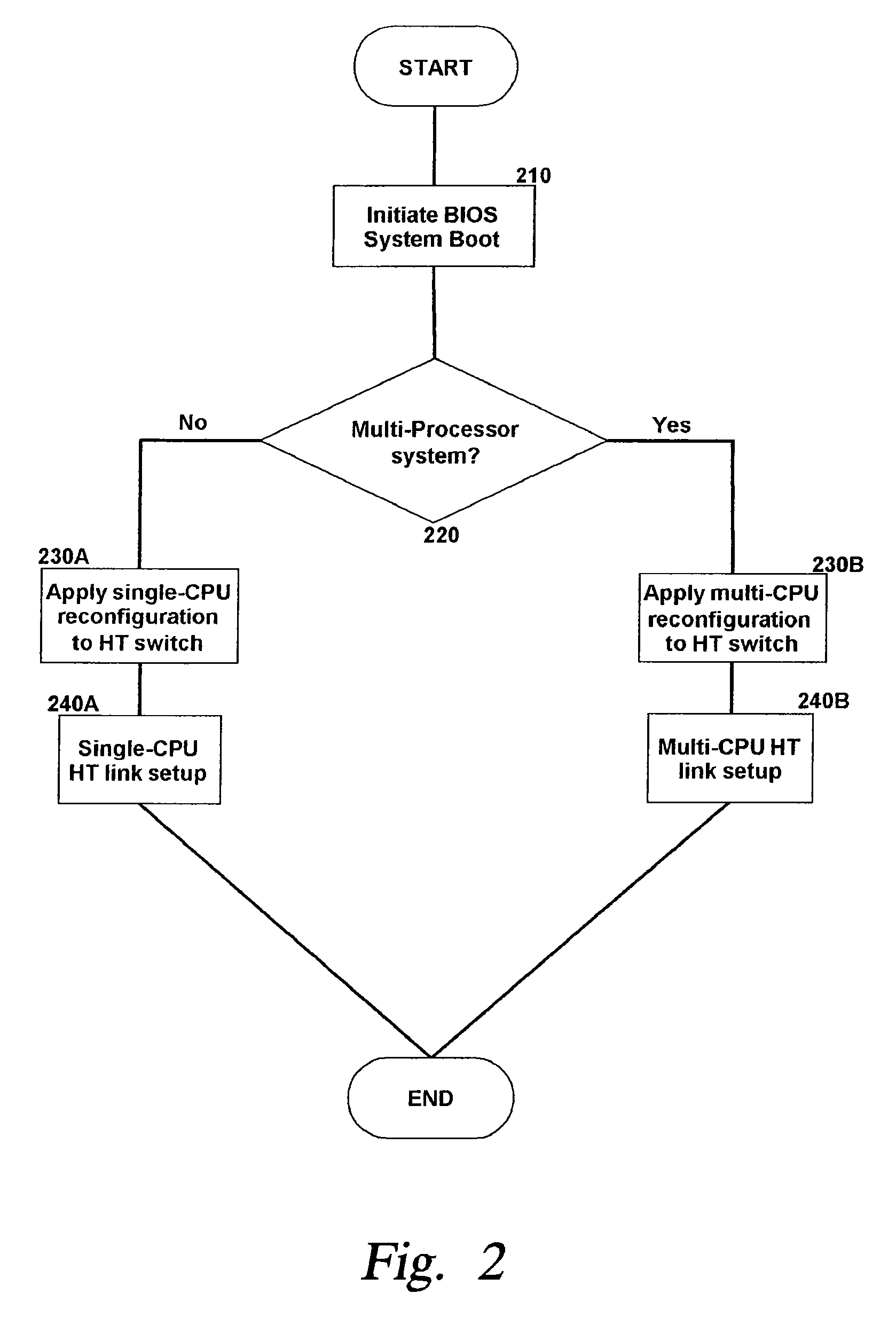

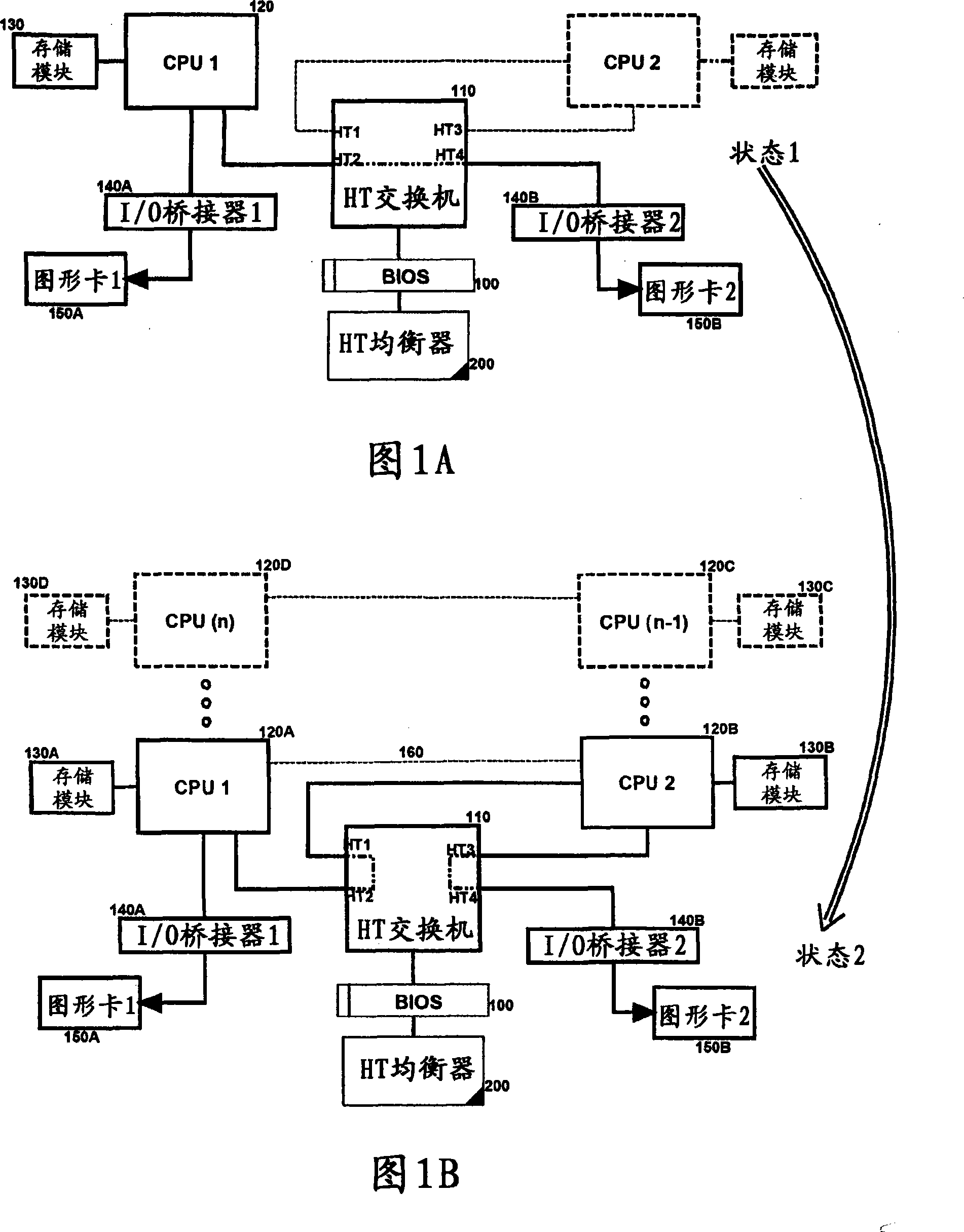

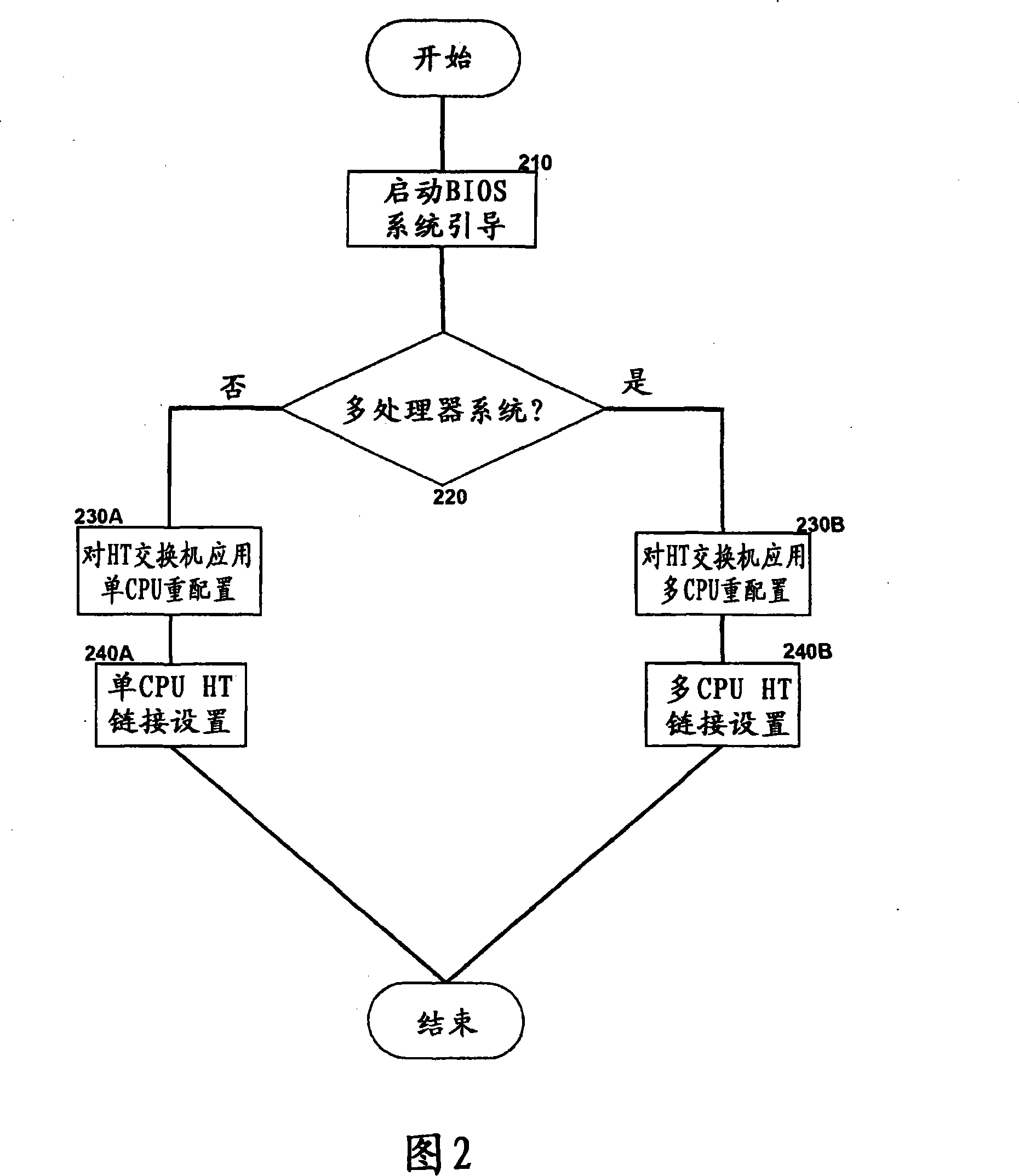

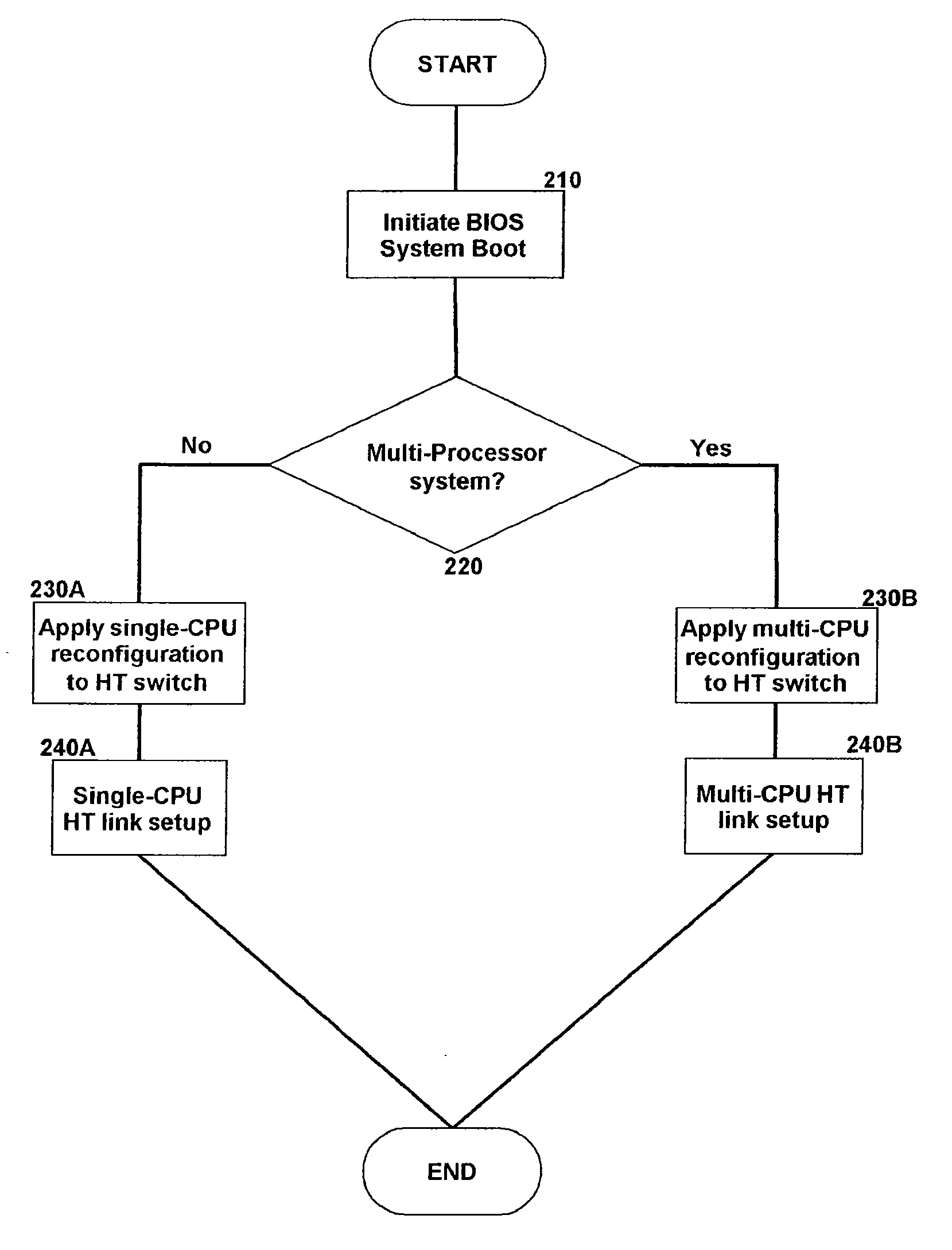

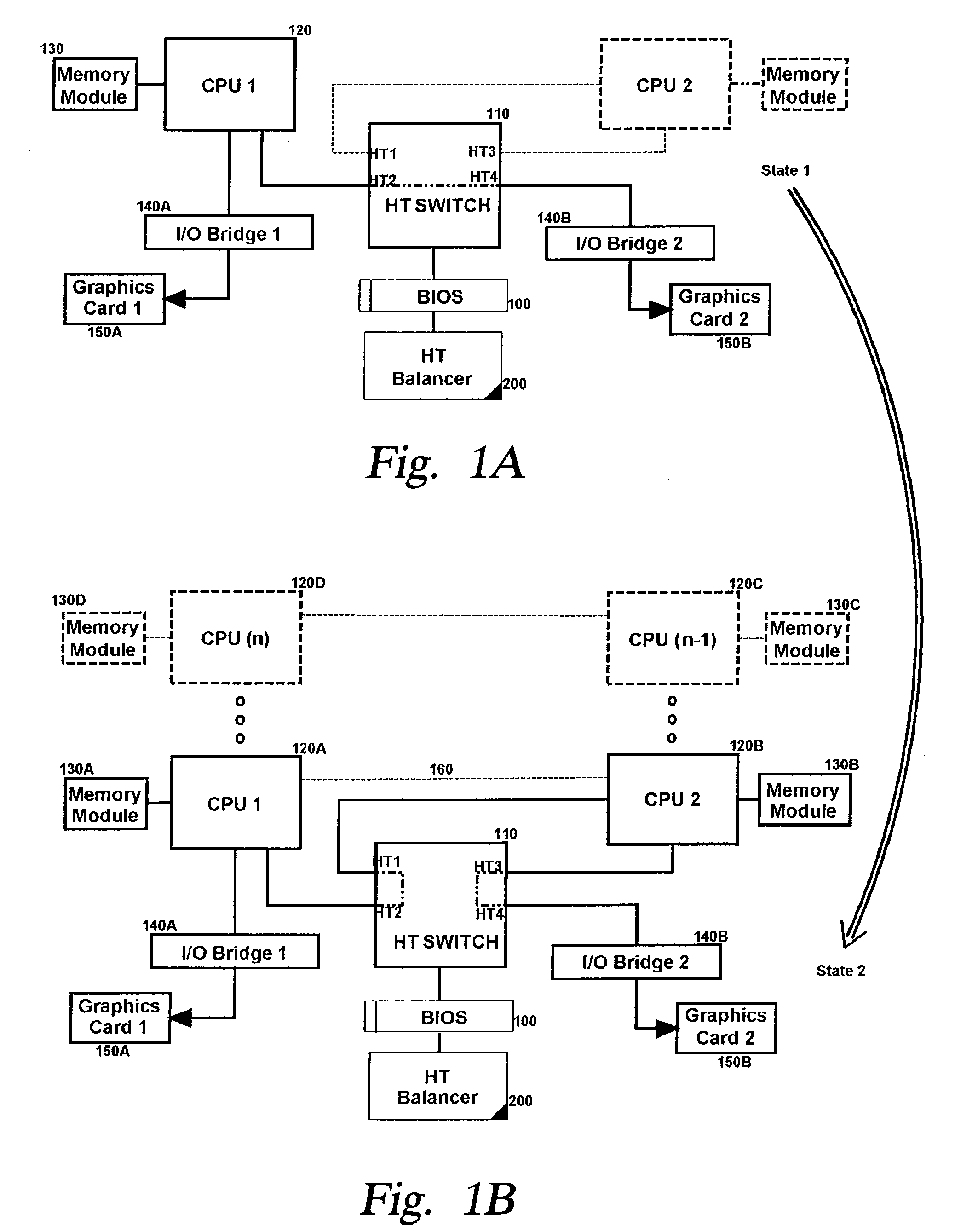

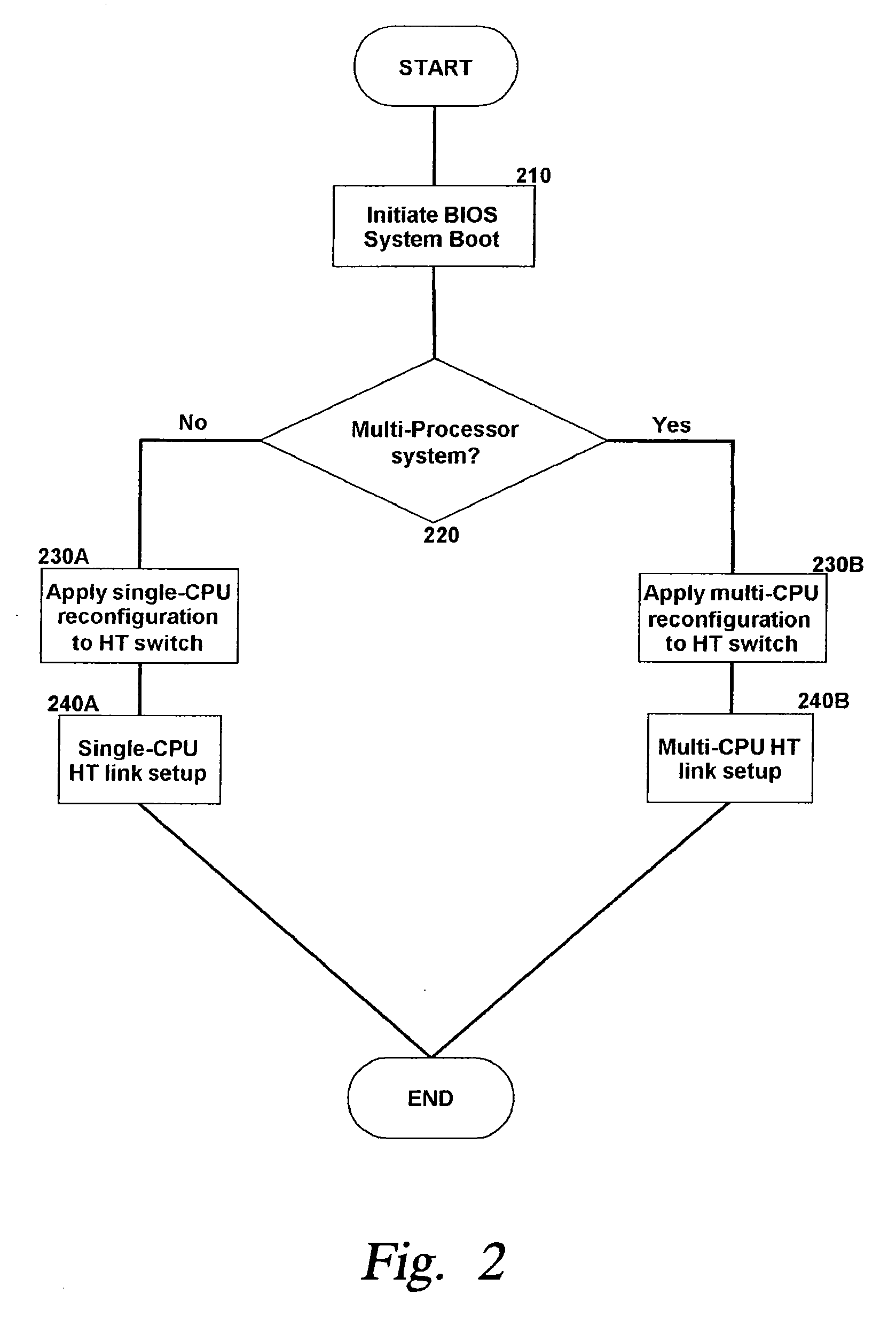

Flexibly configurable multi central processing unit (CPU) supported hypertransport switching

ActiveUS7797475B2Flexible configurationDigital computer detailsProgram controlData processing systemData-driven

Embodiments of the invention address deficiencies of the art in respect to hypertransport-based switching for multi-CPU systems and provide a method, system and computer program product for flexibly configurable multi-CPU supported hypertransport switching. In one embodiment of the invention, a hypertransport switching data processing system can be provided. The system can include a CPU and at least two I / O bridges. Each I / O bridge can provide a communications path for data driven to a corresponding peripheral device from the CPU. Notably, the system can include a flexibly configurable hypertransport switch. The switch can include a first configuration adapting the CPU to both of the I / O bridges, and a second configuration adapting the CPU to a first one of the I / O bridges and a second CPU to a second one of the I / O bridges.

Owner:IBM CORP

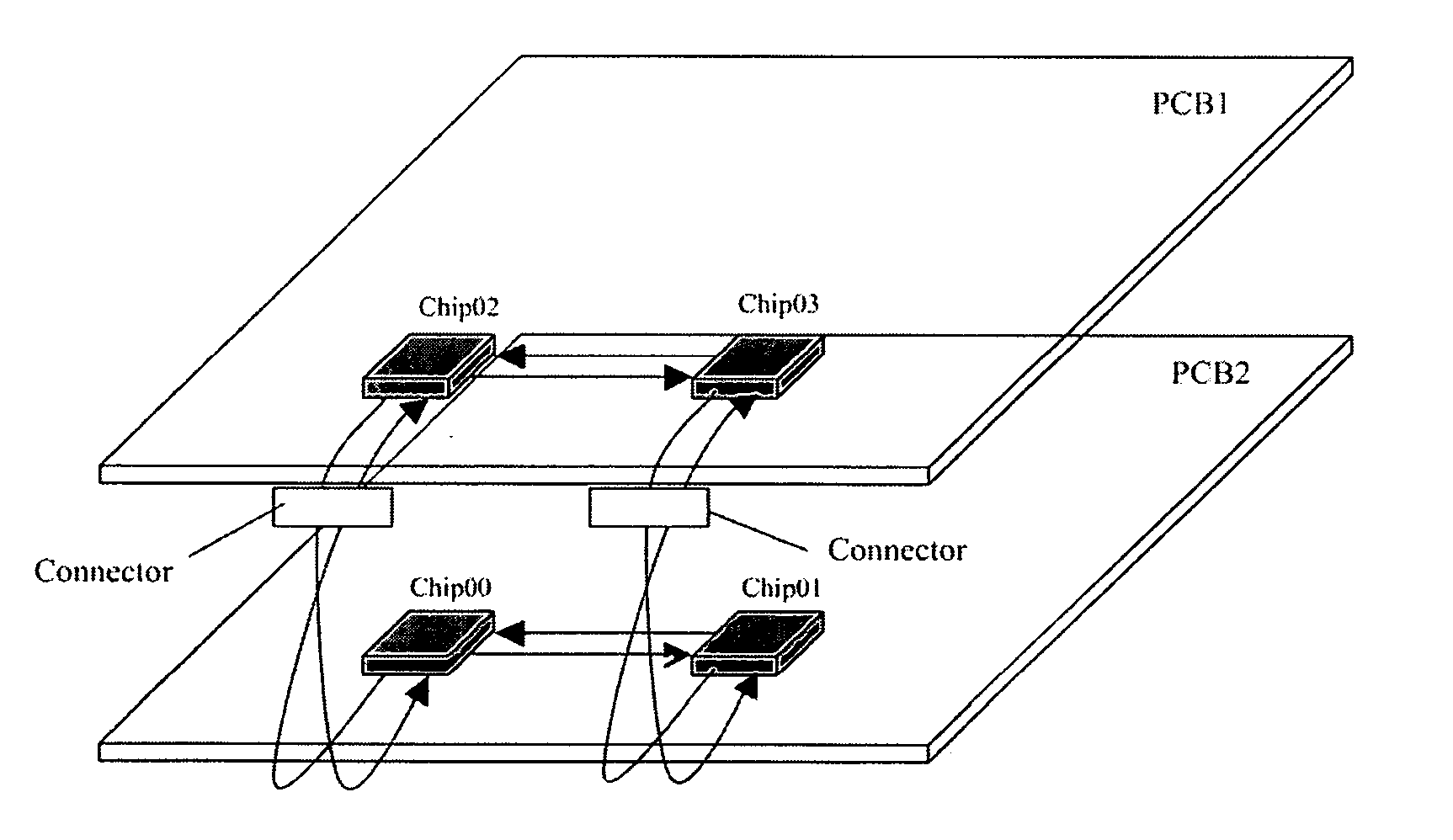

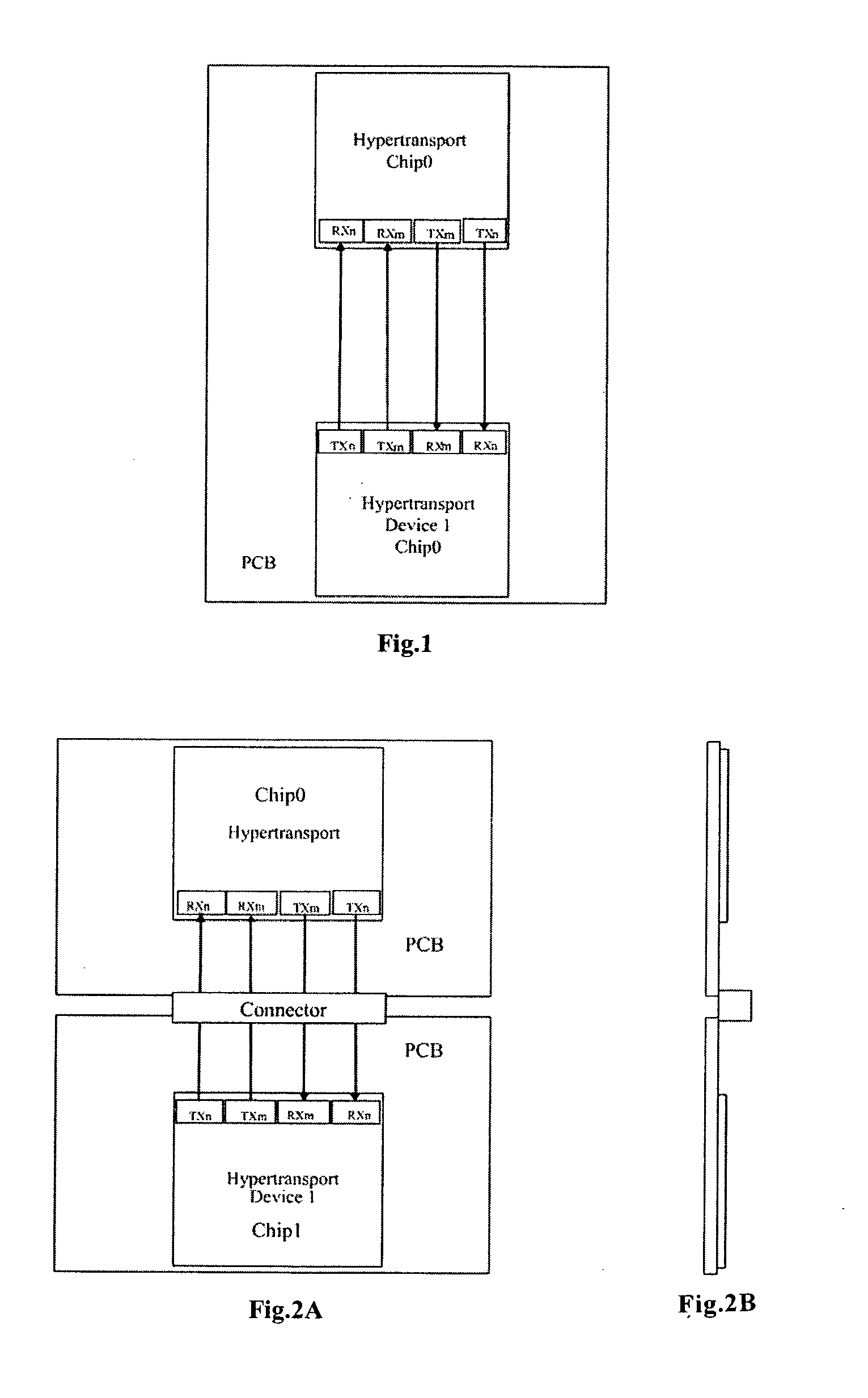

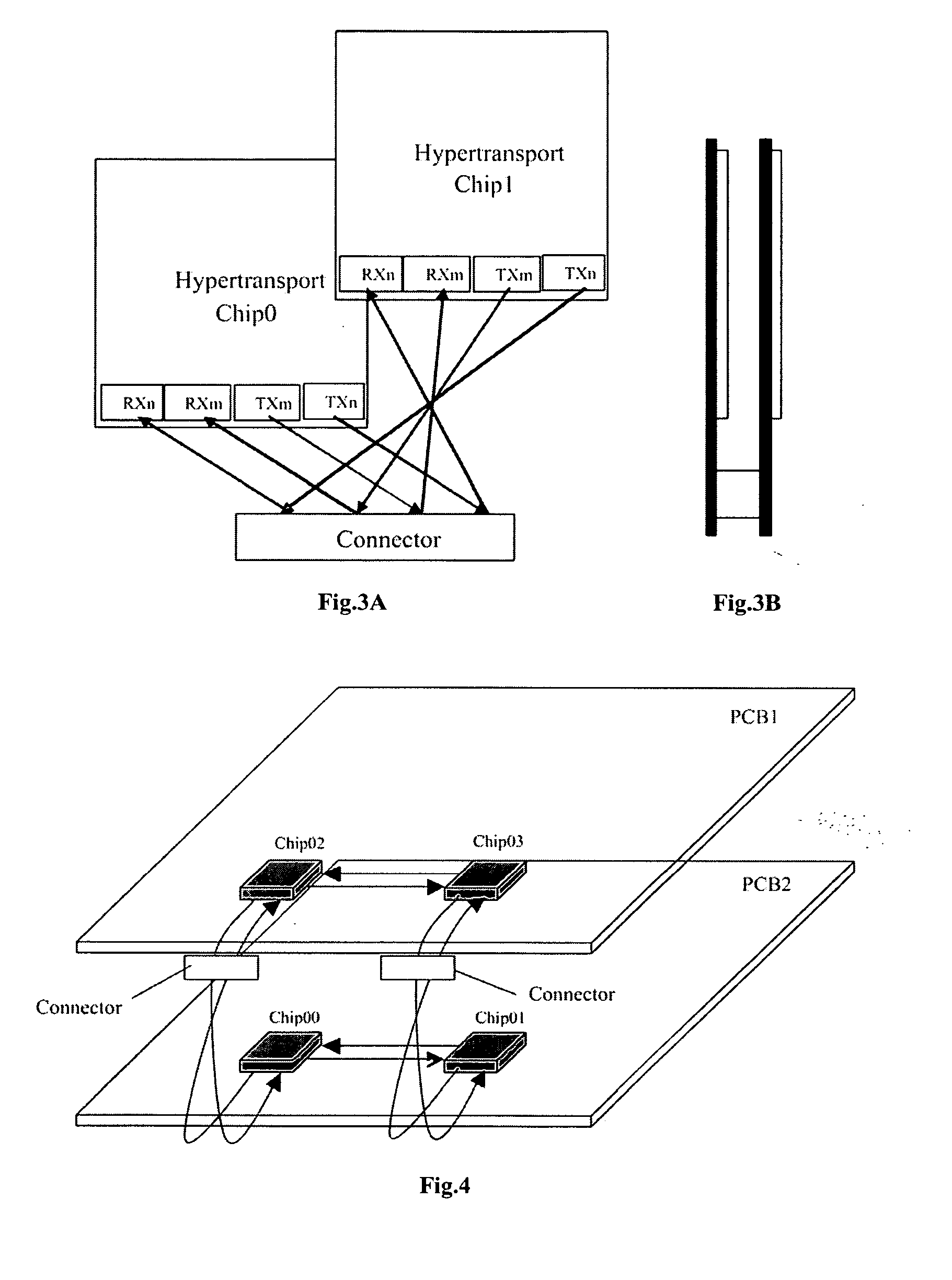

Interconnect structure between HyperTransport bus interface boards

InactiveUS20070156938A1Increase costDegrade signal qualityElectric digital data processingSignal qualitySignal on

An interconnect structure between HyperTransport bus interface boards, for interconnecting corresponding HyperTransport bus interfaces disposed on different Printed Circuit Boards (PCBs) via a connector. The connector cuts across a HyperTransport bus, and terminals of two HyperTransport bus interfaces on different PCBs connected via the connector are connected with each other correspondingly via connecting lines sequentially distributed, so as to avoid the intercross of the connecting lines. The present invention may solve the problem of intercrossing of signals on the HyperTransport bus between processors or other chips during inter-board connecting without the increase of PCB layer number or the degradation of signal quality and the additional cost.

Owner:HUAWEI TECH CO LTD

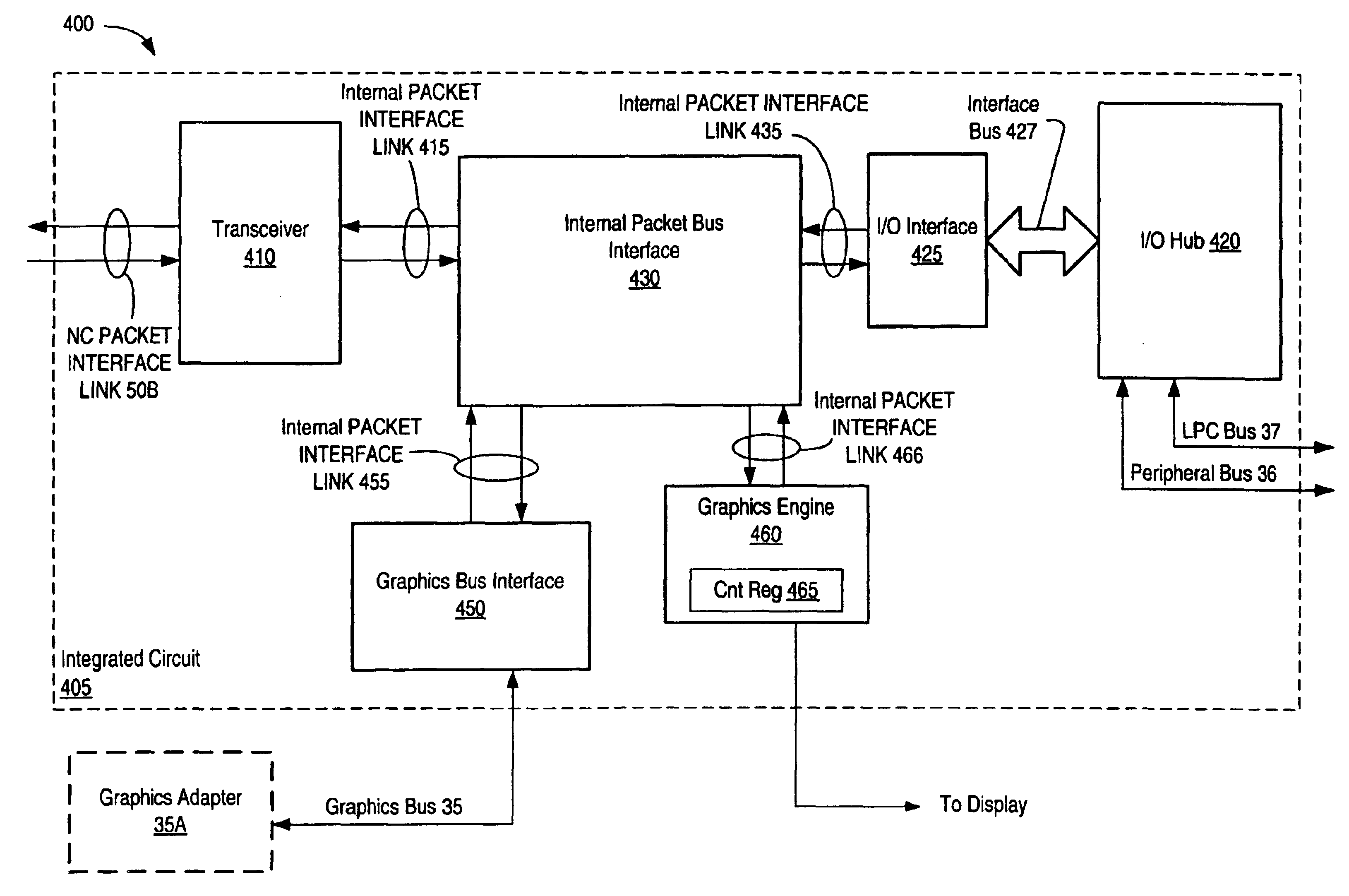

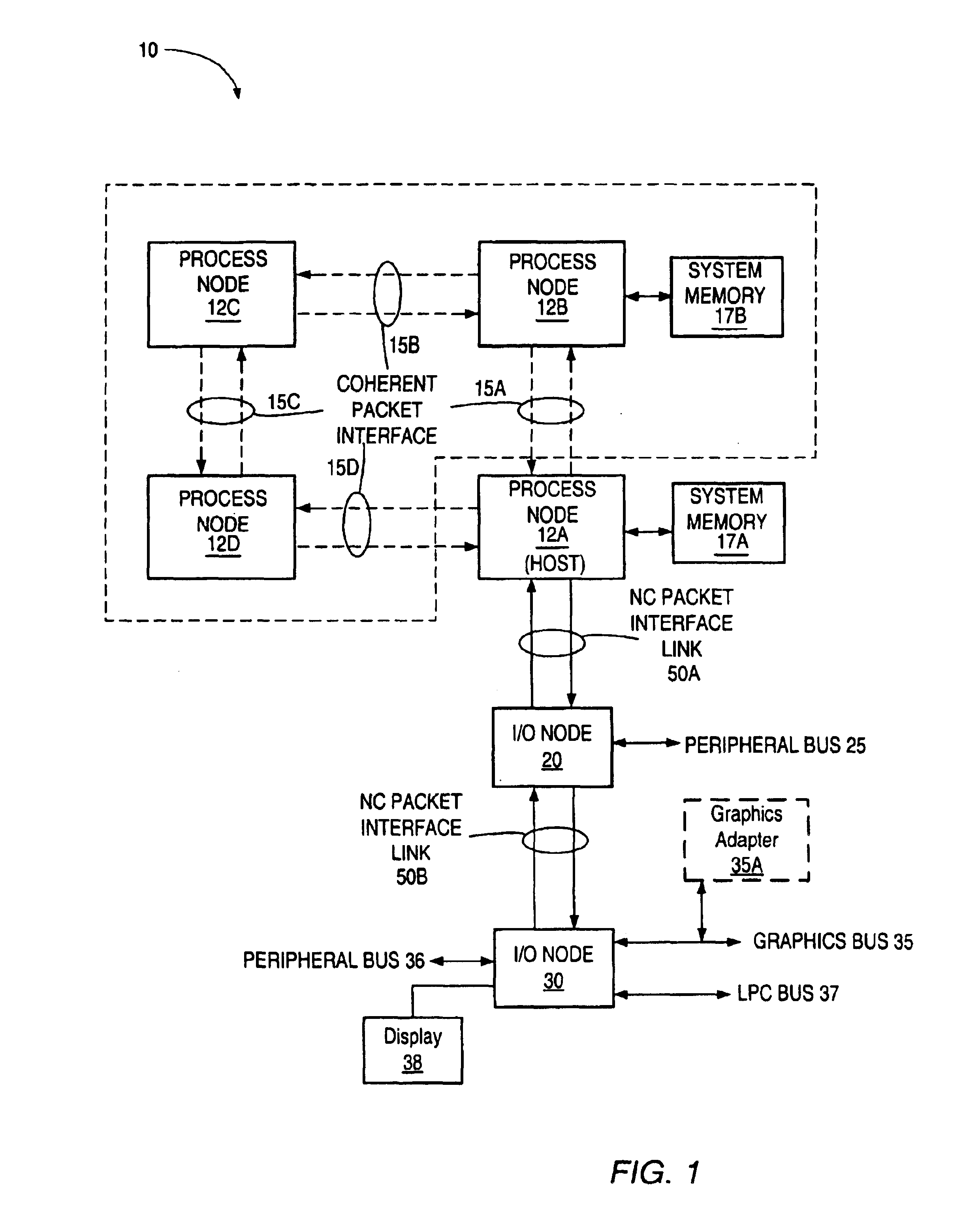

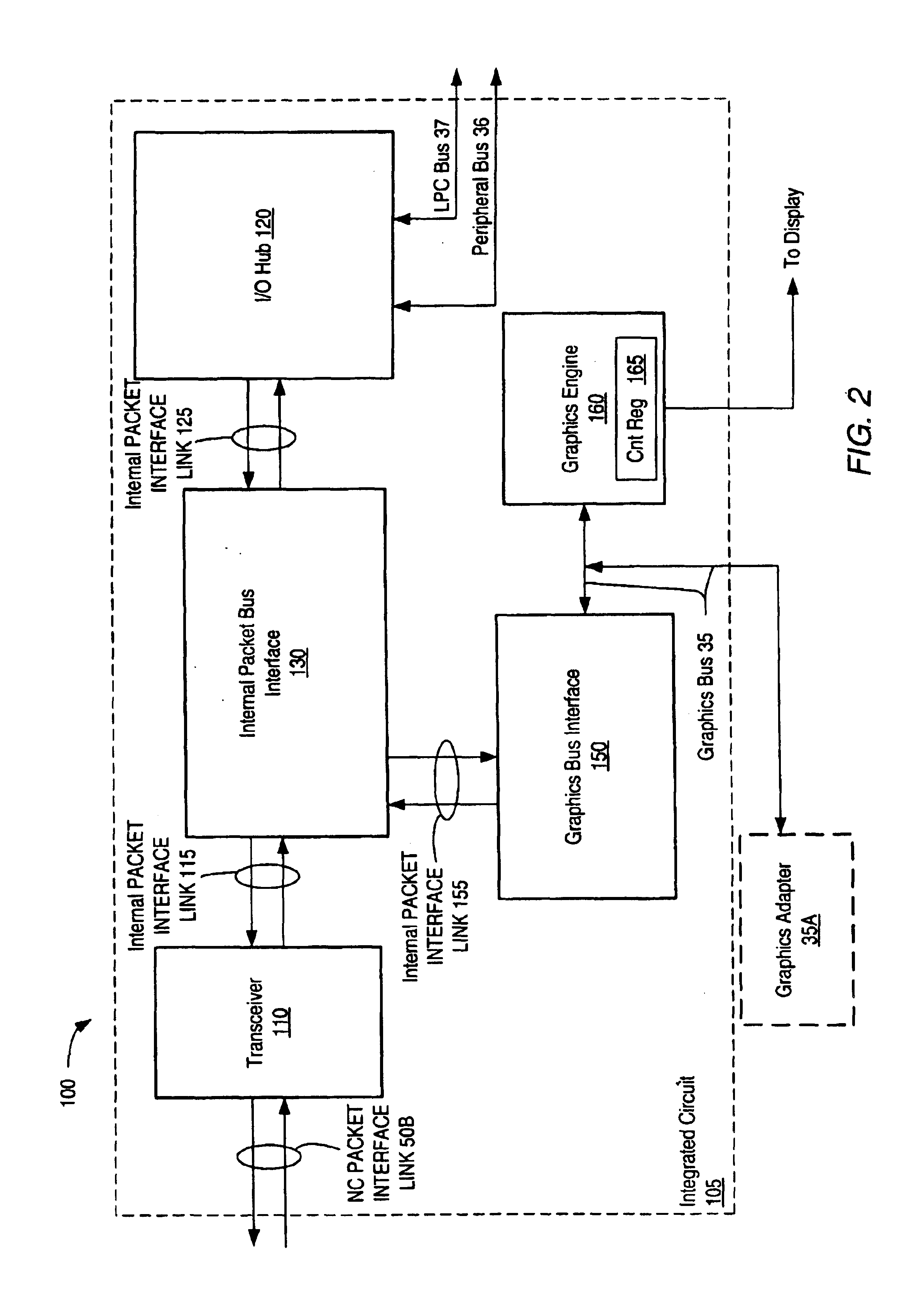

I/O node for a computer system including an integrated graphics engine and an integrated I/O hub

An I / O node for a computer system including an integrated graphics engine and integrated I / O hub. An input / output node that is implemented on an integrated circuit chip includes a transceiver unit, a graphics engine and an I / O hub. The transceiver unit may receive and transmit packets on a point-to-point link of a packet interface. The graphics engine may be coupled to receive graphics packets received by the transceiver unit and may render digital image information in response to receiving the graphics packets. The I / O hub may be coupled to receive I / O packets corresponding to packets received by the transceiver unit and may initiate bus cycles corresponding to the I / O packets upon a peripheral bus. The packet interface link may be a point-to-point HyperTransport™ link including a first and second set of uni-directional wires which may convey control and data packets over the same wires.

Owner:GLOBALFOUNDRIES US INC

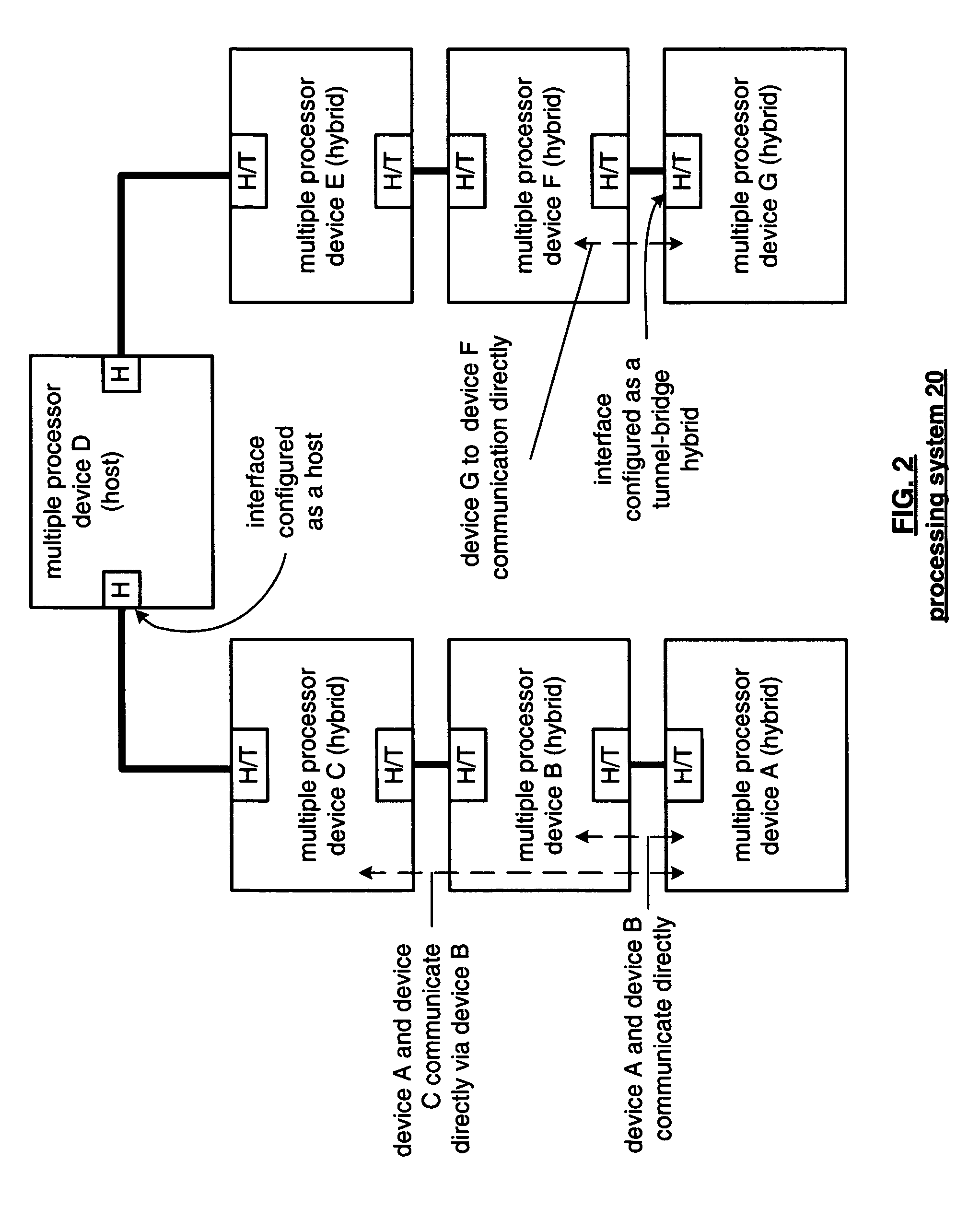

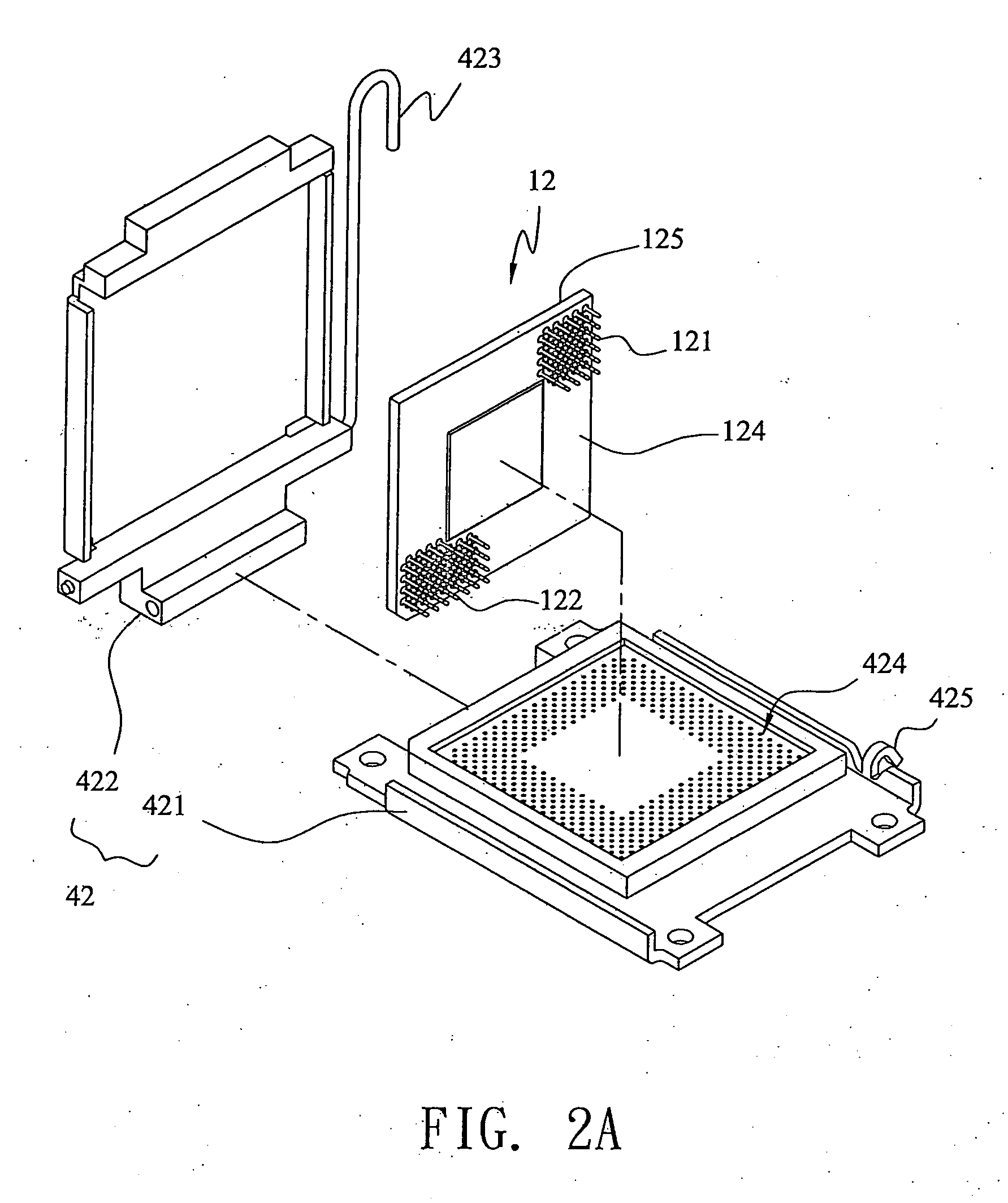

Computer system and main board equipped with hybrid hypertransport interfaces

InactiveUS20070218709A1Printed circuit aspectsPrinted circuit manufactureOn boardComputerized system

A computer system comprises a main board equipped with a HT device. The HT interface comprises a first connector and a riser card. The first connector is compatible with HT Device-Under-Test (HT-DUT) specifications and electrically connected onto the main board. The riser card, inserted onto the main board, includes a second connector compatible with HT-DUT specifications and a third connector compatible with HT expansion (HTX) specifications. The first connector and the second connector are electrically connected for data transmission. Therefore, the main board equipped with both the HT-DUT connector and the HTX connector achieves smaller on-board space and fewer on-board connection interfaces.

Owner:TYAN COMP

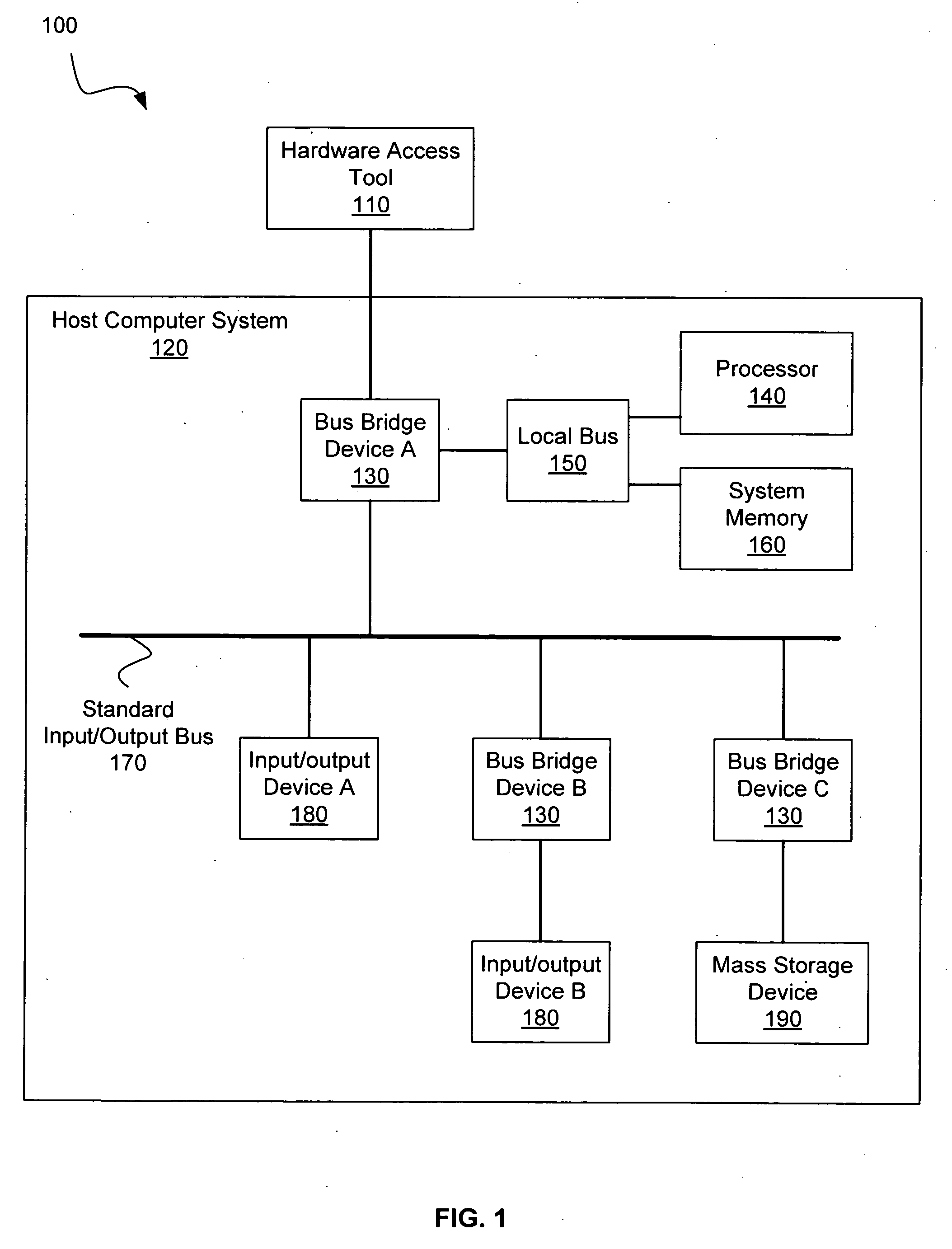

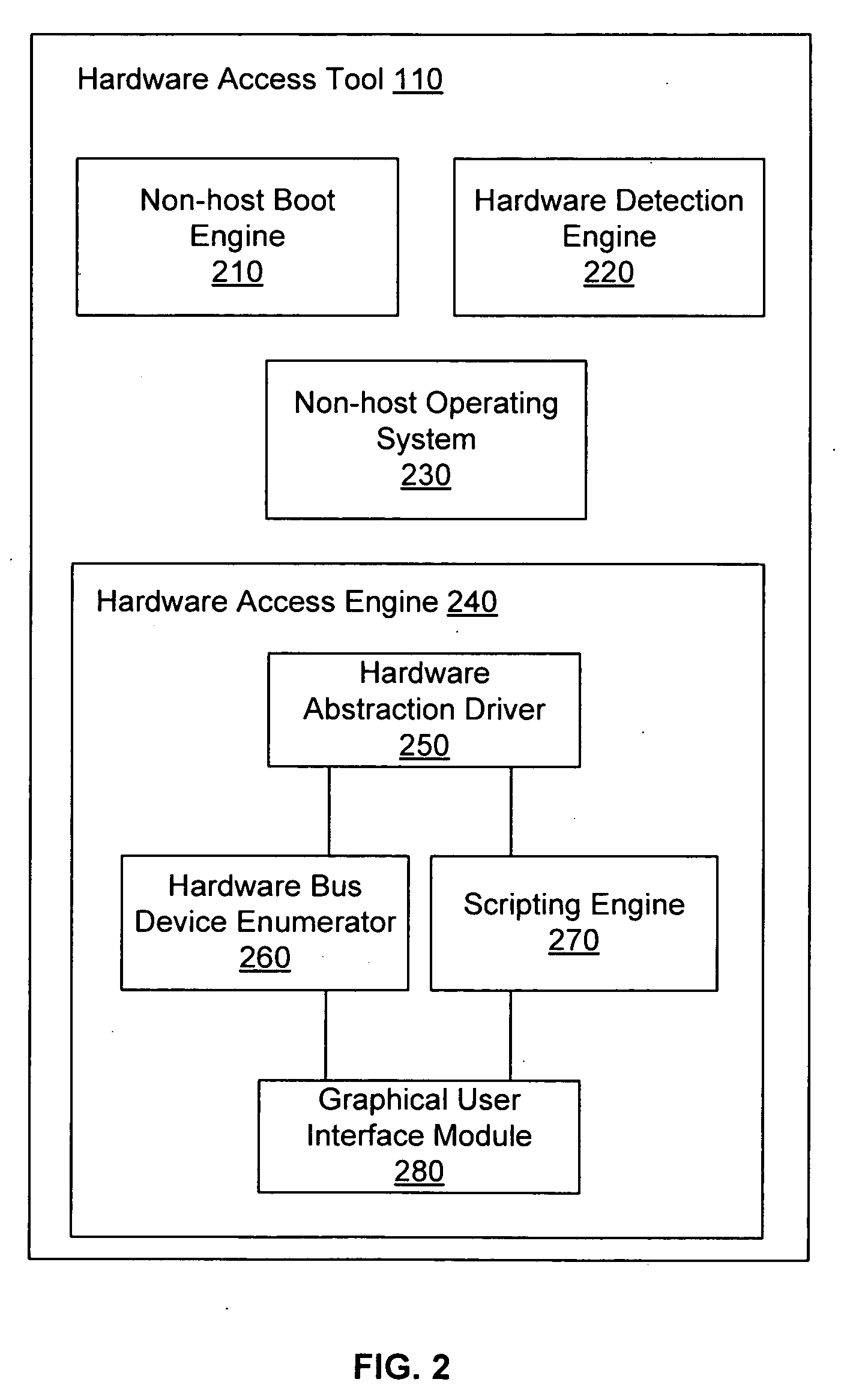

Systems and methods for accessing input/output devices

InactiveUS20070101220A1Prevent corruptionMore accessElectronic circuit testingError detection/correctionOperational systemPCI Express

Systems and methods are provided for a hardware access tool to access a computer input / output (I / O) device coupled to a standard I / O bus on a host computer system. Upon receiving a standard I / O bus command, the hardware access tool translates the bus command on-the-fly for operation on a selected I / O device. The hardware access tool includes a bootable operating system for use when operating the invention, thus avoiding possible corruption of any existing host operating system. Accessing an input / output device may be for testing, debugging, developing, programming, configuring, or any other reason for accessing an I / O device. The hardware access tool may operate with standard I / O bus architectures such as PCI, CompactPCI, PMC, PCI-X, PCI Express, InfiniBand, HyperTransport, PC CardBus, PCMCIA, AGP, USB, ExpressCard, and IEEE 1394.

Owner:SO MASSERATI H

Structure for a flexibly configurable multi central processing unit (CPU) supported hypertransport switching

ActiveUS7853638B2Multiple digital computer combinationsElectric digital data processingData processing systemEngineering

Owner:INT BUSINESS MASCH CORP

Structure for resetting a hypertransport link in a blade server

A design structure embodied in a machine readable storage medium for designing, manufacturing, and / or testing a design is described for resetting a HyperTransport link in a blade server, including reassigning, by a blade management module, a gate signal from enabling a transceiver to signaling a HyperTransport link reset; sending, by the blade management module to a reset sync module on an out-of-band bus, the gate signal; and in response to the gate signal, sending, by the reset sync module to the blade processor, HyperTransport reset signals. The HyperTransport link includes a bidirectional, serial / parallel, high-bandwidth, low-latency, point to point data communications link. The blade server includes the blade processor, the reset sync module, and the baseboard management controller. The blade server is installed in the blade center. The blade center includes the blade management module. The blade management module is coupled to the baseboard management controller by the blade communication bus.

Owner:IBM CORP

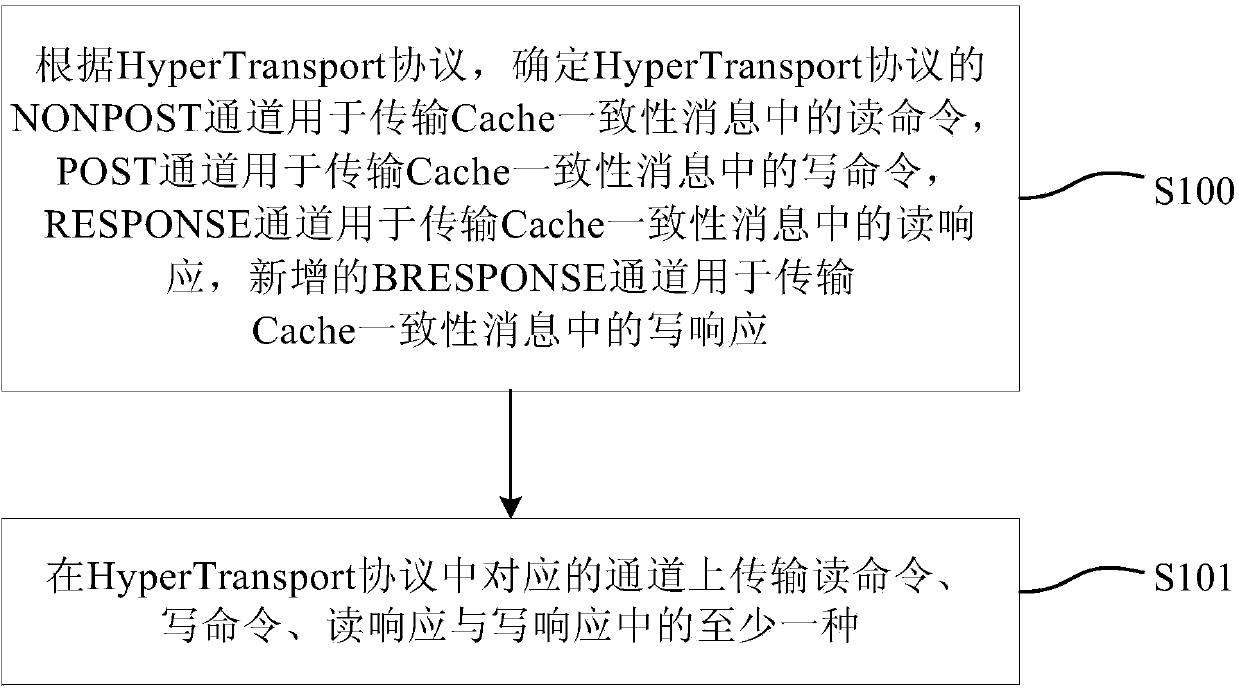

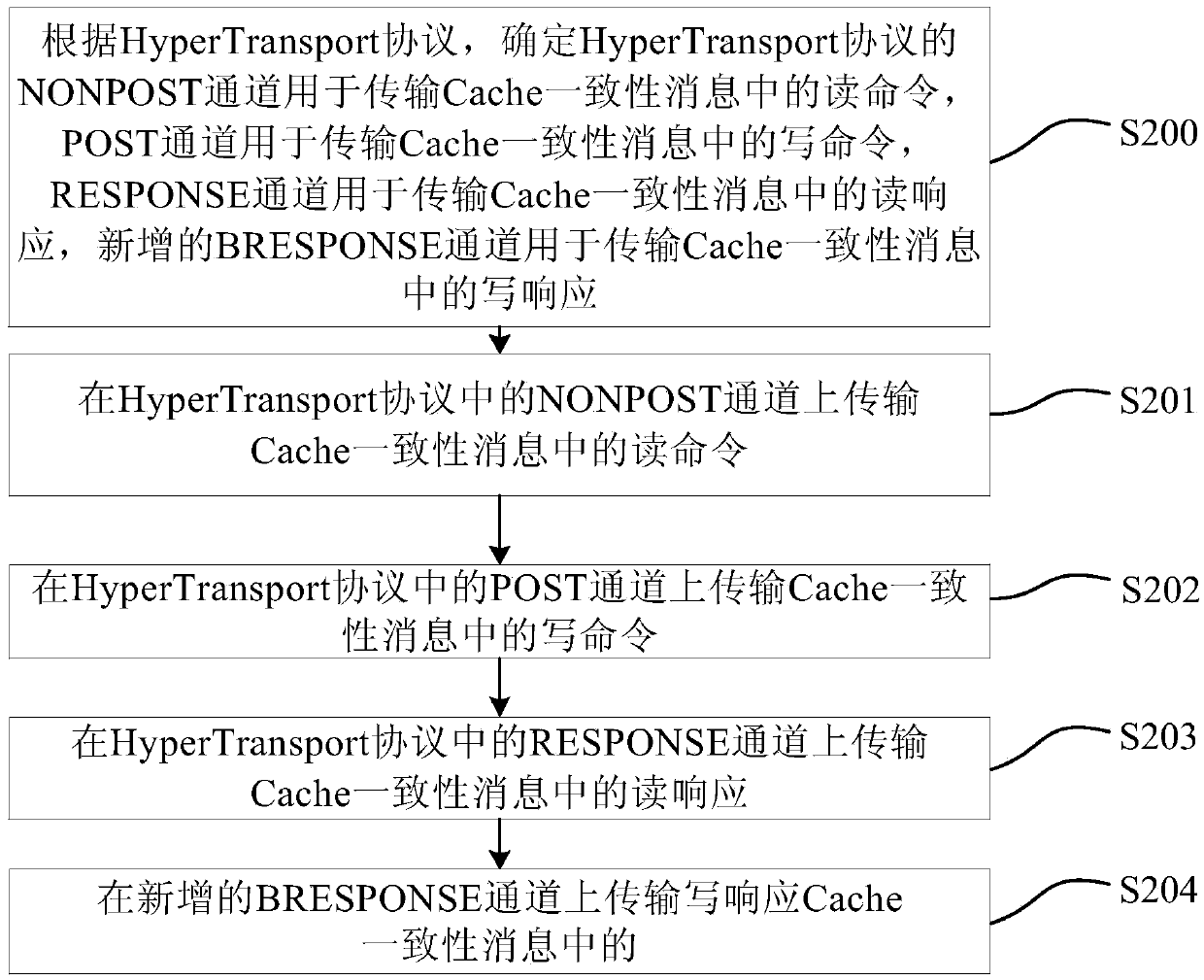

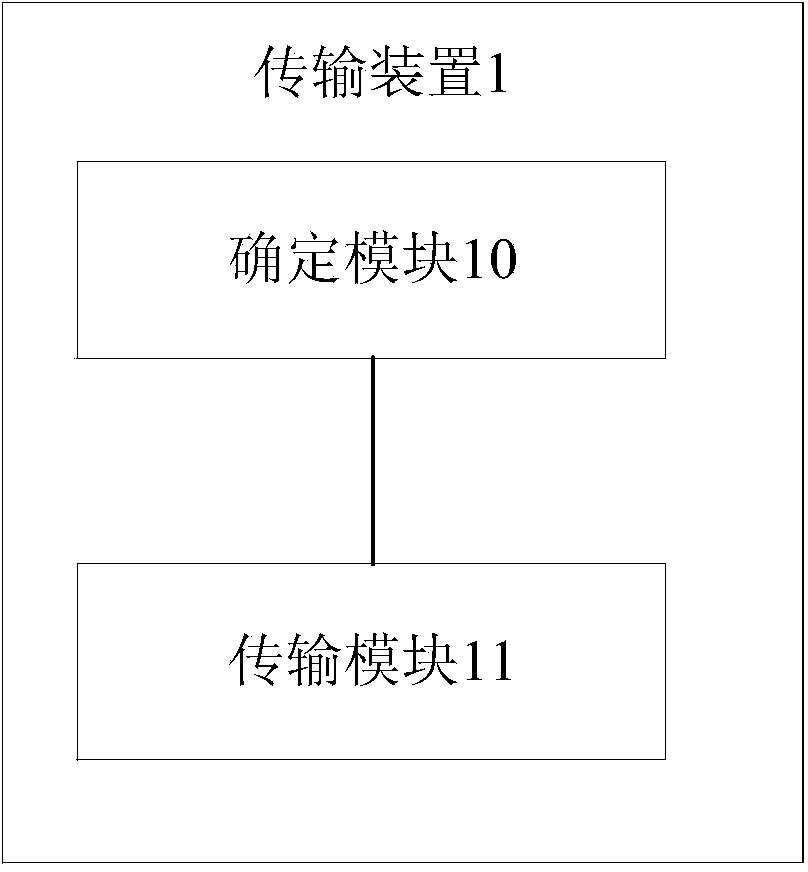

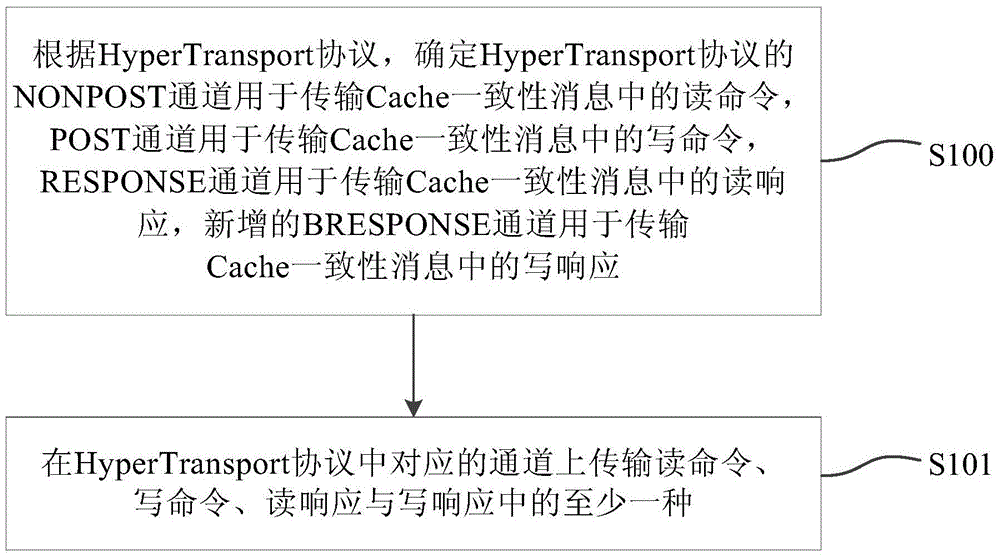

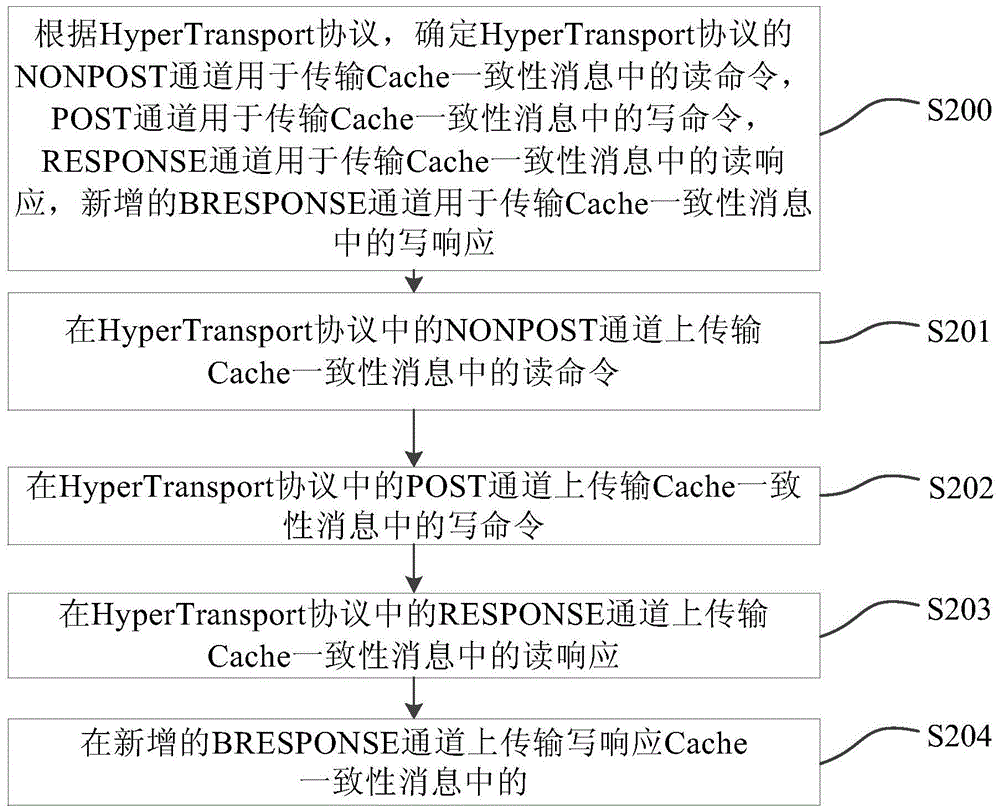

Transmission method and device of high-speed cache consistency information

ActiveCN103995786AAvoid cloggingImprove transmission efficiencyMemory adressing/allocation/relocationInformation transmissionTransmission channel

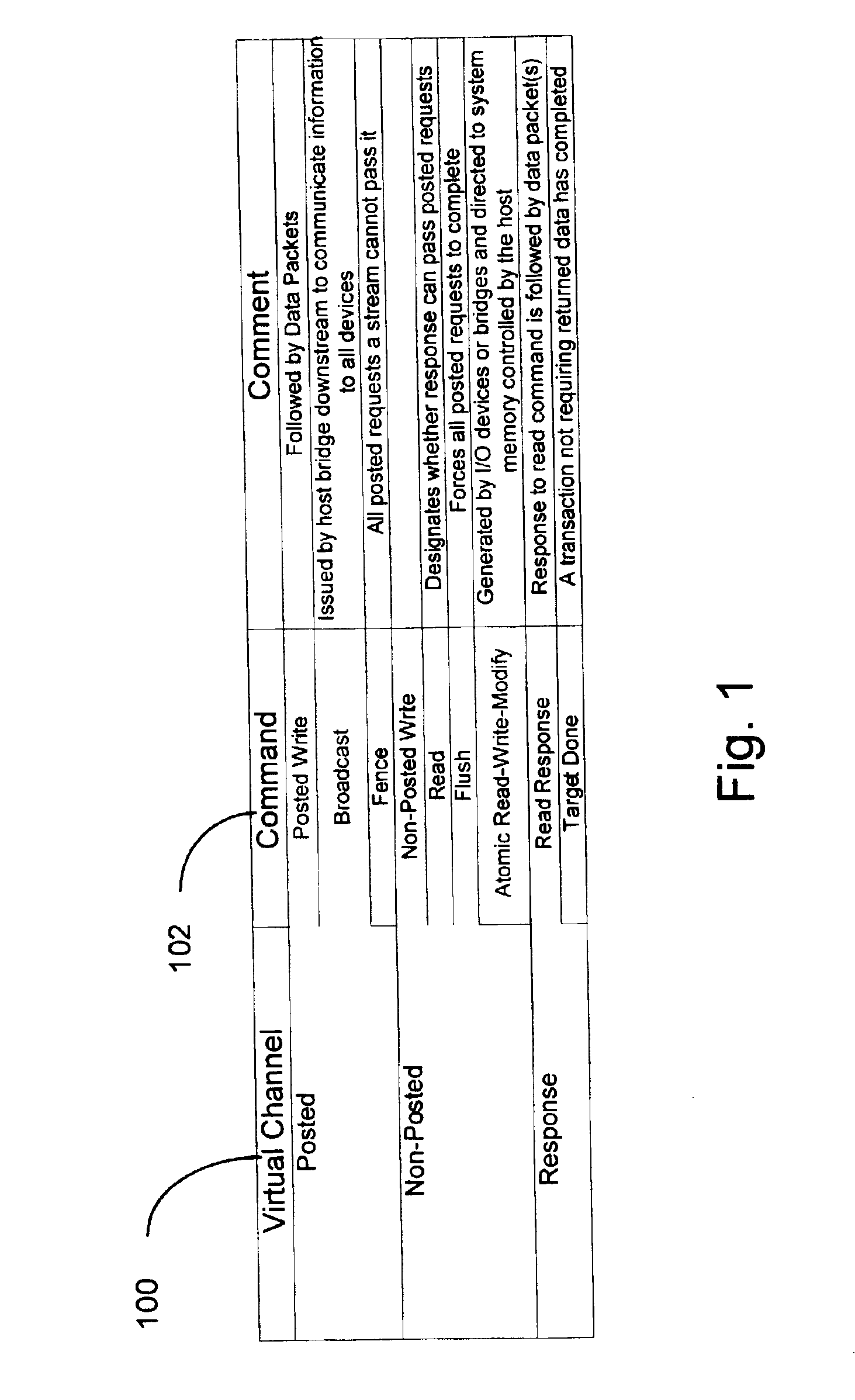

The invention provides a transmission method and device of high-speed cache consistency information. The method comprises the steps that according to a HyperTransport protocol, reading orders used in high-speed cache consistency information transmission of a NONPOST channel of the HyperTransport protocol are determined, a POST channel is used for transmitting writing orders in the high-speed cache consistency information, a RESPONSE channel is used for transmitting reading responses in the high-speed cache consistency information, and a newly-added BRESPONSE channel is used for transmitting writing responses in the high-speed cache consistency information; and at least one kind of the reading orders, the writing orders, the reading responses and the writing responses are transmitted on a corresponding channel of the HyperTransport protocol. According to the technical scheme, blocking of the reading responses and the writing responses on a transmission channel is avoided, and the transmission efficiency of the reading responses and the writing responses is improved.

Owner:LOONGSON TECH CORP

Super transmission switching data processing system and super transmission switching method

ActiveCN101231629AFlexible configurationDigital computer detailsElectric digital data processingData processing systemTransmission switching

The embodiment of the present invention overcomes the defects in the prior art in the hypertransport switching based on multi-central processing unit systems, and provides a method, system and method for hypertransport switching supported by multi-central processing units that can be flexibly configured. Computer Program Products. In one embodiment of the present invention, a hypertransport switched data processing system may be provided. The system may include a central processing unit and at least two input / output bridges. Each input / output bridge may provide a communication path for data being driven from the central processing unit to a corresponding peripheral device. In particular, the system may include a flexibly configurable HyperTransport switch. The switch may include a first configuration of adapting the central processing unit to both of the input / output bridges, and adapting the central processing unit to a first of the input / output bridges and adapting the second central processing unit to in the second configuration of the second one of the I / O bridges.

Owner:INT BUSINESS MASCH CORP

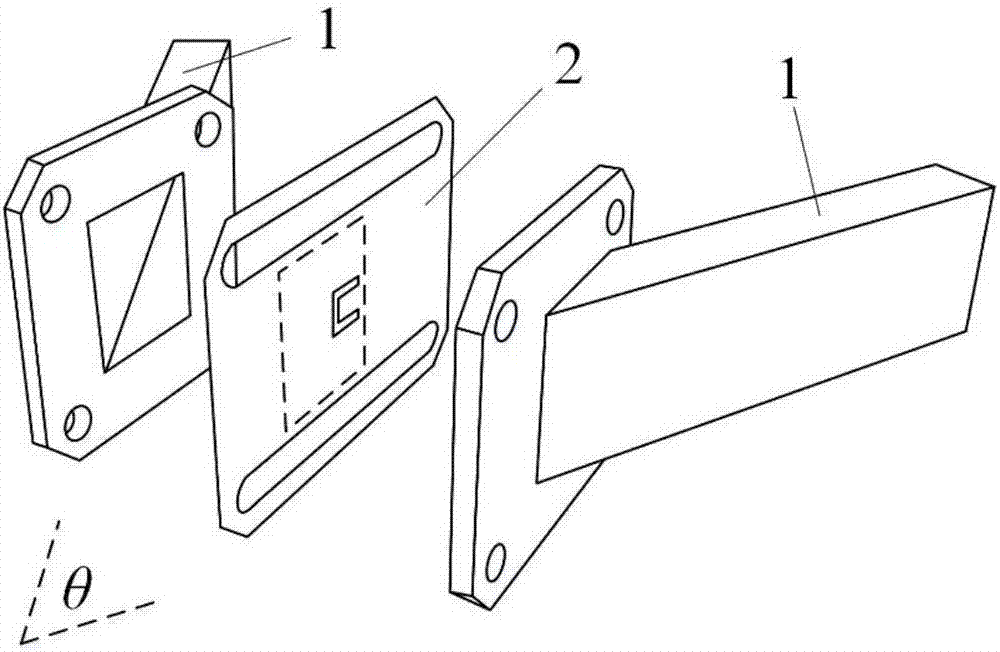

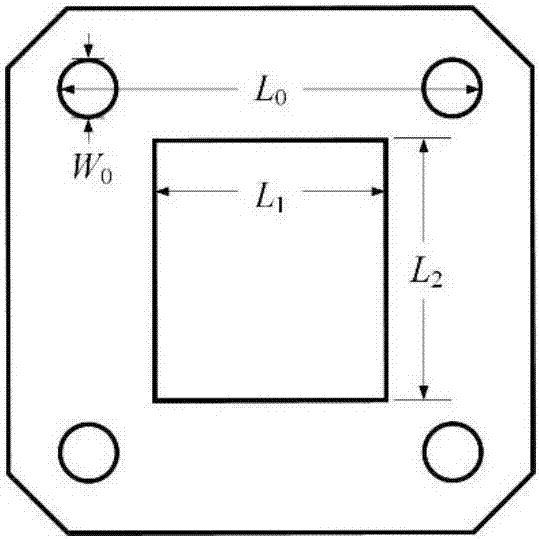

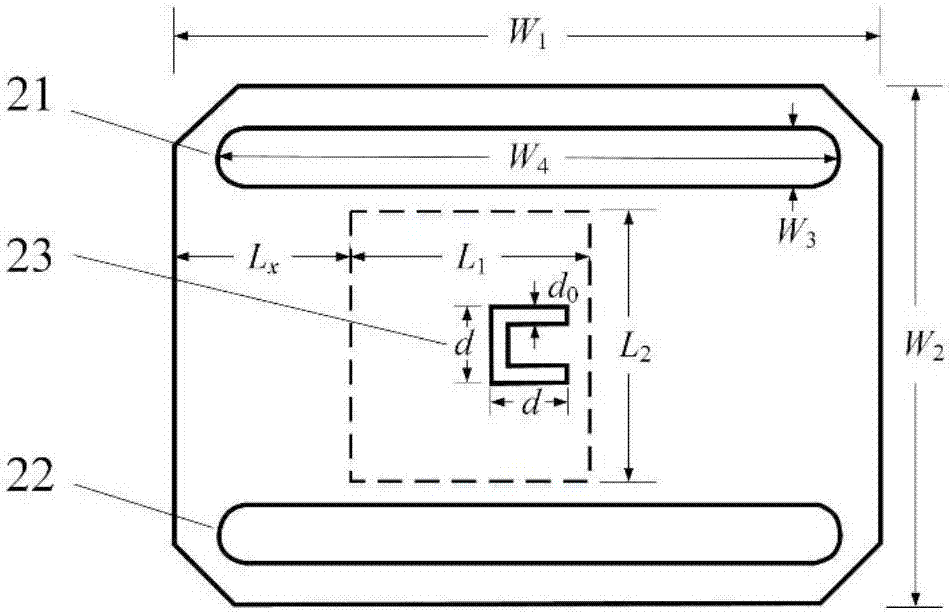

E-plane bending rectangular waveguide adjustable filter based on hypertransport membrane

The invention discloses an E-plane bending rectangular waveguide adjustable filter based on a hypertransport membrane. The adjustable filter mainly solves the problem of small adjustment quantity of passband bandwidth of the existing waveguide adjustable filter. The adjustable filter comprises rectangular waveguides (1) and the hypertransport membrane (2), wherein the rectangular waveguides (1) are in E-plane bending structures; two rectangular flange plates are arranged at bending parts; two strip-type through holes (21) and (22) which are parallel are formed in upper and lower positions of the hypertransport membrane (2); a C-shaped gap (23) is arranged in the middle of the hypertransport membrane (2); an opening of the C-shaped gap (23) faces towards inner bending sides of the waveguides; and the hypertransport membrane (2) is fixed between the two rectangular flange plates of the rectangular waveguides (1), and slides along inner and outer bending sides of the waveguides in the two strip-type through holes (21) and (22) to adjust a position of the C-shaped gap (23) and realize continuous adjustment of passband bandwidth. The adjustable filter has the advantages of large adjustment quantity of the passband bandwidth and simple structure, and can be used in the field of microwave communication.

Owner:XIDIAN UNIV

Structure for a flexibly configurable multi central processing unit (CPU) supported hypertransport switching

ActiveUS20080256222A1Digital computer detailsElectric digital data processingData processing systemTest design

A design structure embodied in a machine readable storage medium for designing, manufacturing, and / or testing a design for addressing deficiencies of the art in respect to hypertransport-based switching for multi-CPU systems and for flexibly configurable multi-CPU supported hypertransport switching is provided. The design structure can include a hypertransport switching data processing system. The system can include a CPU and at least two I / O bridges. Each I / O bridge can provide a communications path for data driven to a corresponding peripheral device from the CPU. Notably, the system can include a flexibly configurable hypertransport switch. The switch can include a first configuration adapting the CPU to both of the I / O bridges, and a second configuration adapting the CPU to a first one of the I / O bridges and a second CPU to a second one of the I / O bridges.

Owner:IBM CORP

Hypertransport exception detection and processing

In accordance with the present invention a system for detecting transaction errors in a system comprising a plurality of data processing devices using a common system interconnect bus, comprises a node controller operably connected to said system interconnect bus and a plurality of interface agents communicatively coupled to said node controller. Error corresponding to transactions between said interface agents and other processing modules in said system are directed to said node controller; and wherein transaction errors that would not normally be communicated to said system interconnect bus are communicated by said node controller to said system interconnect bus to be available for detection. In an embodiment of the present invention, the interface agents operate in accordance with the hypertransport protocol. A system control and debug unit and a trace cache operably connected to the system bus can be used to diagnose and store errors conditions.

Owner:AVAGO TECH INT SALES PTE LTD

Resetting A Hypertransport Link In A Blade Server

Methods, apparatus, and computer program products are described for resetting a HyperTransport link in a blade server, including reassigning, by a blade management module, a gate signal from enabling a transceiver to signaling a HyperTransport link reset; sending, by the blade management module to a reset sync module on an out-of-band bus, the gate signal; and in response to the gate signal, sending, by the reset sync module to the blade processor, HyperTransport reset signals. The HyperTransport link includes a bidirectional, serial / parallel, high-bandwidth, low-latency, point to point data communications link. The blade server includes the blade processor, the reset sync module, and the baseboard management controller. The blade server is installed in the blade center. The blade center includes the blade management module. The blade management module is coupled to the baseboard management controller by the blade communication bus.

Owner:LENOVO GLOBAL TECH INT LTD

Transmission method and device for cache consistency message

ActiveCN103995786BAvoid cloggingImprove transmission efficiencyMemory systemsInformation transmissionTransmission channel

Owner:LOONGSON TECH CORP