High-speed encryption and decryption system and method for realizing MSI interrupt processing based on multi-algorithm IP core

An encryption and decryption, multi-algorithm technology, applied in the direction of electrical digital data processing, multi-programming devices, instruments, etc., to achieve the effect of improving efficiency, improving operation processing efficiency, and improving performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

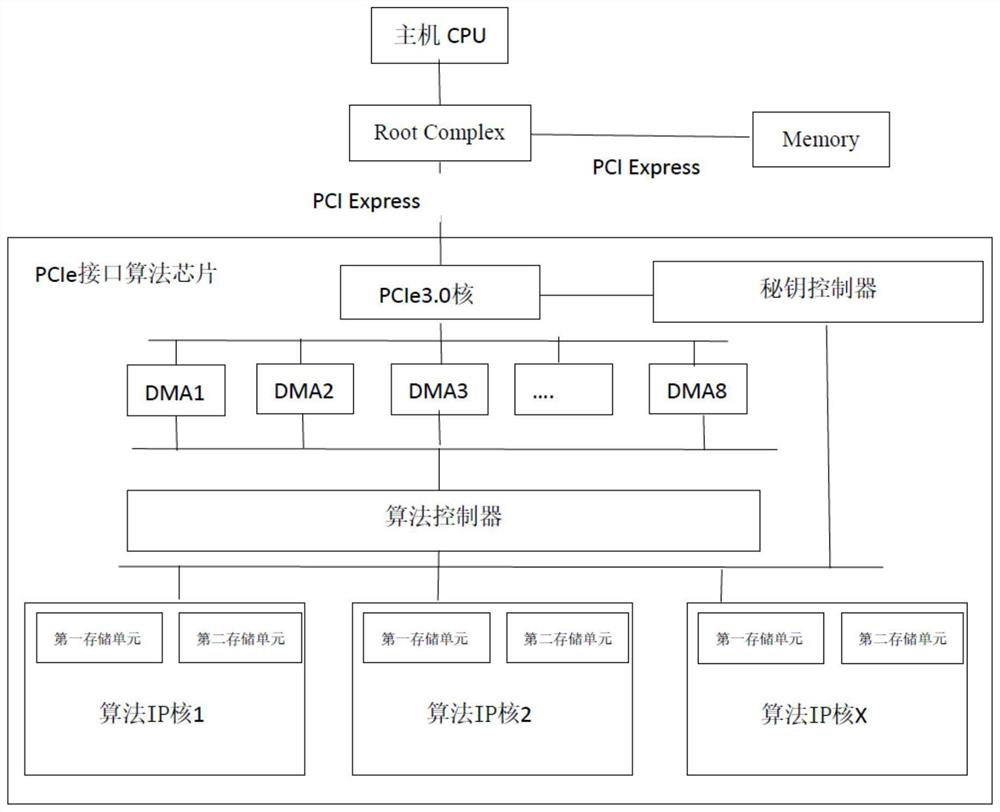

[0059] The present embodiment provides a high-speed encryption and decryption system based on a multi-algorithm IP core to realize MSI interrupt processing, as shown in the figure, including a host computer and an encryption algorithm chip connected through a PCIe3.0 channel, and the encryption algorithm chip includes PCIe3.0. 0 core, DMA module, key controller, algorithm controller, multiple algorithm IP cores and their internal first storage units and second storage units, the DMA module provides multiple channels for encryption and decryption data transfer, the The algorithm controller receives the encryption and decryption commands issued by the host computer, and uses the algorithm IP core in the encryption and decryption commands to perform the encryption and decryption process operations. The first storage unit and the second storage unit inside the algorithm IP core cache the encryption and decryption source data. , the algorithm IP core performs encryption and decrypti...

Embodiment 2

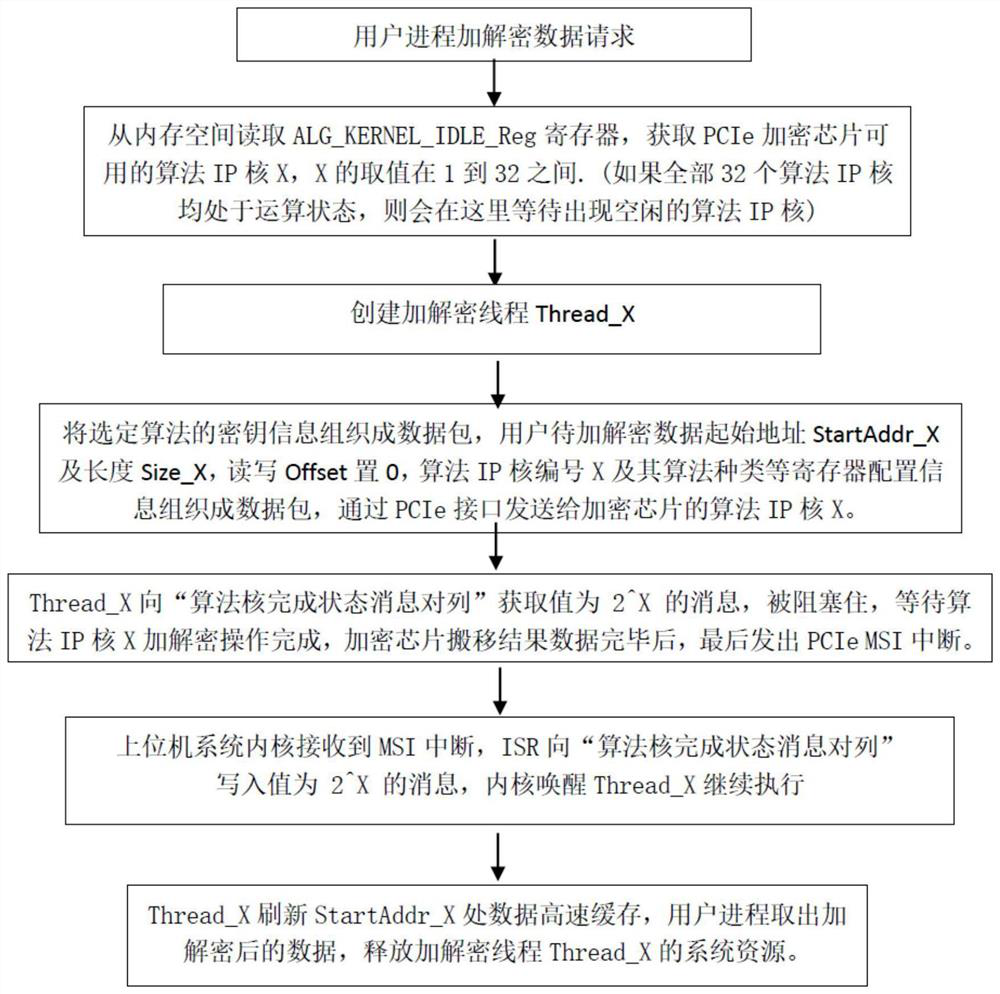

[0071] This embodiment provides a high-speed encryption and decryption method for implementing MSI interrupt processing based on a multi-algorithm IP core, which is implemented based on the high-speed encryption and decryption system for implementing MSI interrupt processing based on a multi-algorithm IP core described in Embodiment 1, including: The following steps:

[0072] S1, configure the host computer, initialize the host computer, at this time all algorithm IP cores are in an idle state;

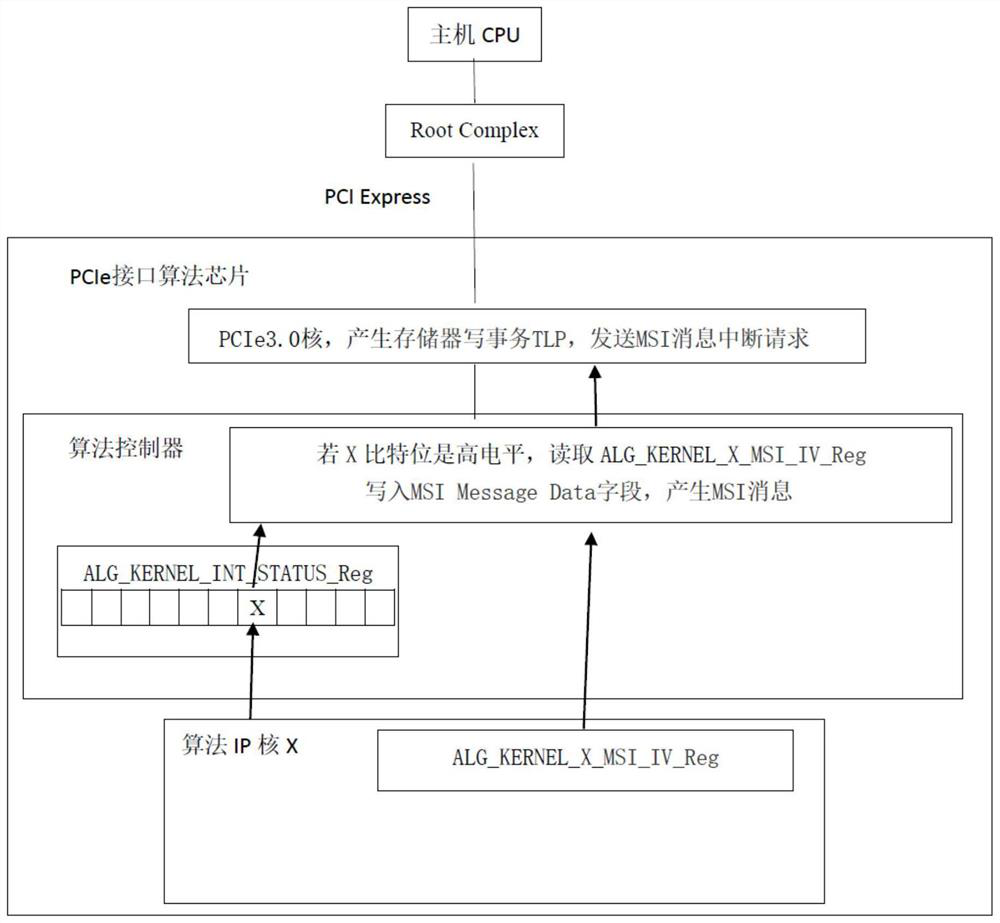

[0073] When the host computer completes the initialization, the driver software of the PCIe encryption and decryption chip in this design will read the Multiple Message Enable field in the MSI Message Control register of the PCIe3.0 core of the PCIe encryption and decryption chip from the MSI related registers of the PCIe configuration space, and obtain the The number of consecutive interrupts that can be used by the PCIe encryption and decryption chip is n, reads the MSI Message Data...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com