System and method for improving I2C communication performance

A technology for communication performance and memory access, applied in the field of microelectronic communication control, can solve problems such as the inability to dynamically improve filtering performance, and achieve the effects of improving anti-interference performance, improving processing efficiency, and reducing the number of interruptions

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

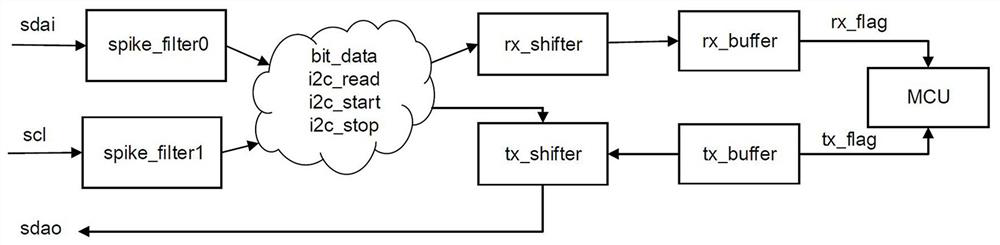

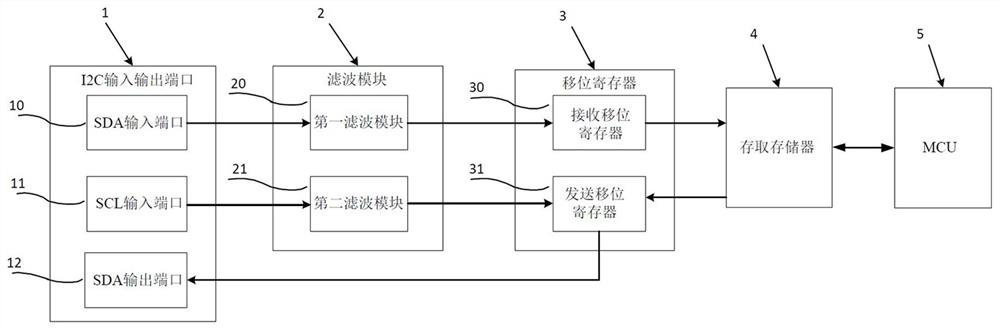

[0044] Such as figure 2 As shown, the present invention provides a system for improving I2C communication performance, including an I2C input and output port 1 , a filtering module 2 , a shift register 3 , an access memory 4 and an MCU 5 connected in sequence. Specifically, the number of filter clock cycles of the filter module 2 is n, and its calculation formula is:

[0045] n=f clk / (2×f scl )-1 ; (1)

[0046] where f clk is the sampling clock frequency, f scl is the I2C clock frequency.

[0047] It should be noted that the I2C bus in this embodiment is composed of a data line SDA and a clock line SCL, and the I2C bus is connected to IC pins through PCB traces. In the traditional I2C slave system, the value of the number of filter clock cycles is fixed, that is, the filtering performance is fixed, and the filtering performance cannot be dynamically improved when the I2C frequency changes. Therefore, the present invention proposes a method for dynamically adjusting th...

Embodiment 2

[0058] Such as Figure 5-6 As shown, the present invention also provides a method for improving I2C communication performance, including the system for improving I2C communication performance described in Embodiment 1, the I2C slave operation module connected to MCU 5, and writing to access memory 4 as follows data steps;

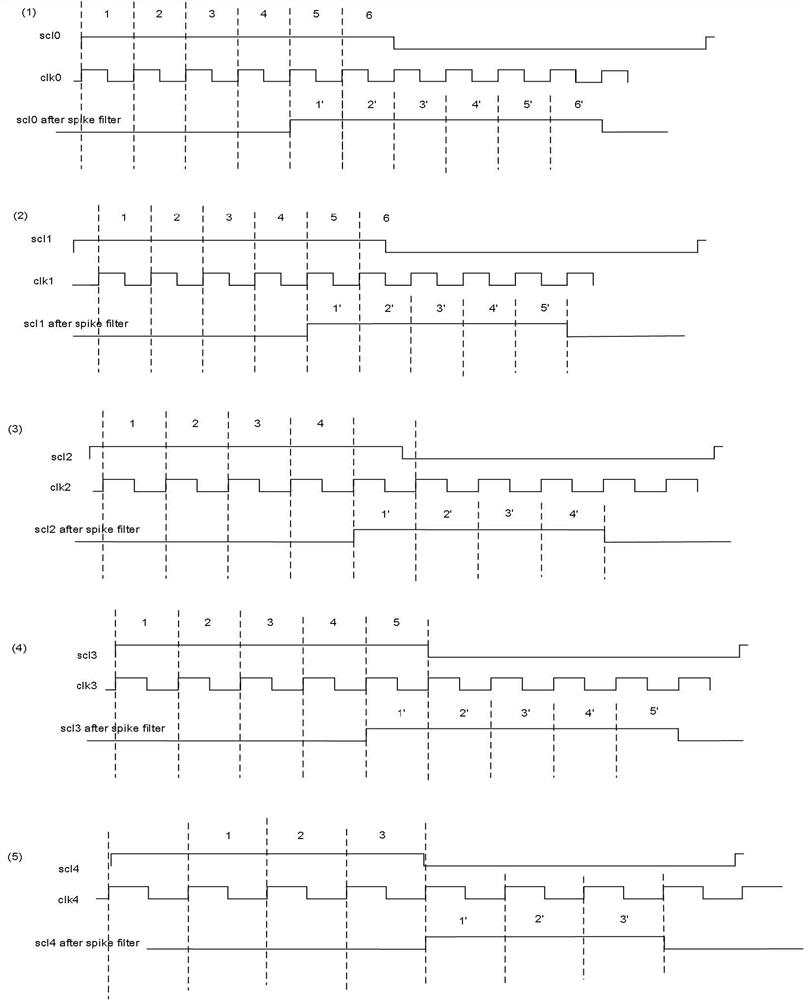

[0059] S10. The I2C slave operation module initiates data transmission. Before performing this step, MCU 5 also needs to calculate the number of filter clock cycles of the filter module 2 according to the above-mentioned sampling clock frequency and I2C clock frequency according to the formula (1), and finally adjust the number of filter clock cycles dynamically according to Table 1 . Specifically, if the calculated number of filter clock cycles is greater than or equal to 8, it is adjusted to 8; if it is less than 8 and greater than or equal to 7, it is adjusted to 7; if it is less than 7 and greater than or equal to 6, it is adjusted to 6; less than 6 a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More