Fragment scheduling method based on WRR algorithm in graphics processor

A graphics processor and scheduling method technology, applied in the direction of processor architecture/configuration, image memory management, etc., can solve the problem of not having enough fragments, etc., and achieve the effect of balanced and reliable scheduling

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018] It is easy to understand that, according to the technical solutions of the present invention, without changing the essential spirit of the present invention, those of ordinary skill in the art can propose various alternative structures and implementations. Therefore, the following specific embodiments and accompanying drawings are only exemplary descriptions of the technical solutions of the present invention, and should not be regarded as all of the present invention or as limitations or restrictions on the technical solutions of the present invention.

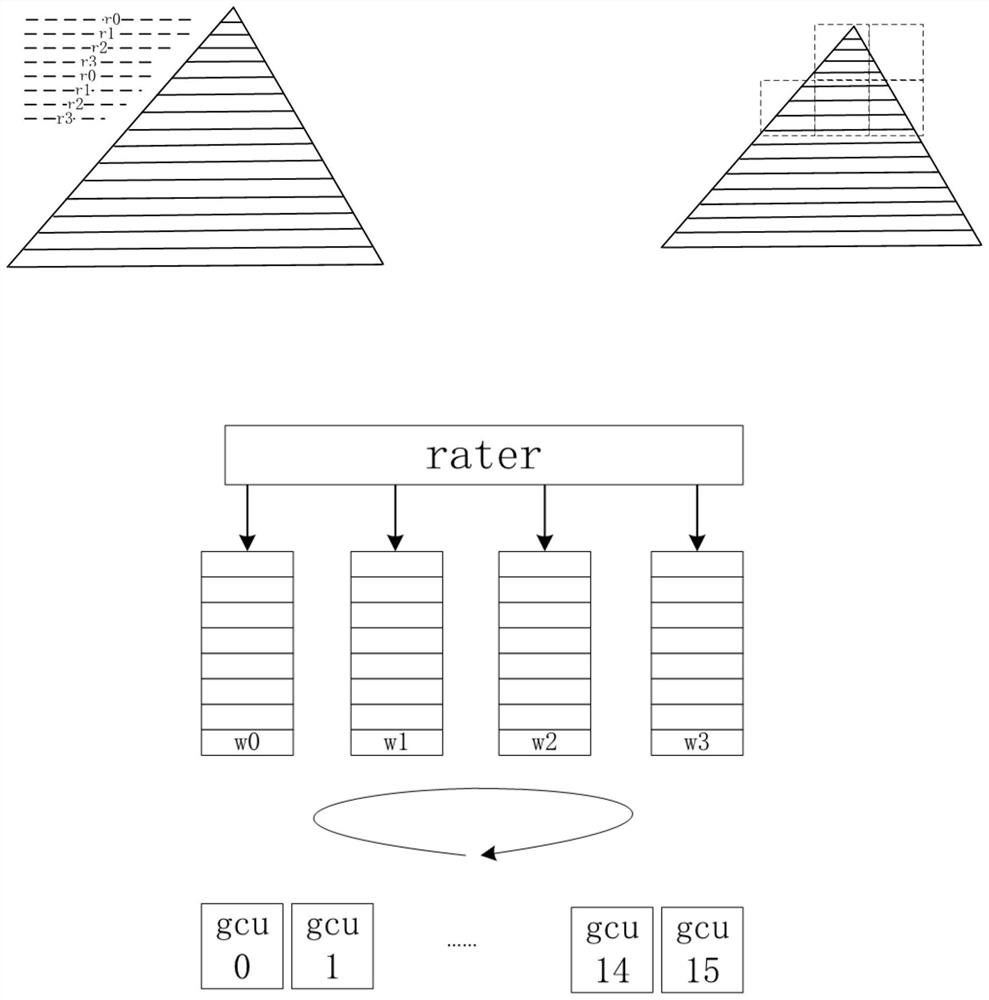

[0019] According to an embodiment of the present invention combined figure 1 A fragment scheduling method based on the WRR algorithm in a graphics processor is shown, including the following steps:

[0020] S1. Use the WRR algorithm to perform weight allocation ratios for multiple channels in the pixel scanning module;

[0021] S2. The scheduling module schedules the plurality of data fragments scanned by the pixel sc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More