Method for forming metal wires in semiconductor device

A semiconductor and metal wire technology, applied in the field of metal wires forming semiconductor devices, can solve problems such as uneven buried characteristics

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

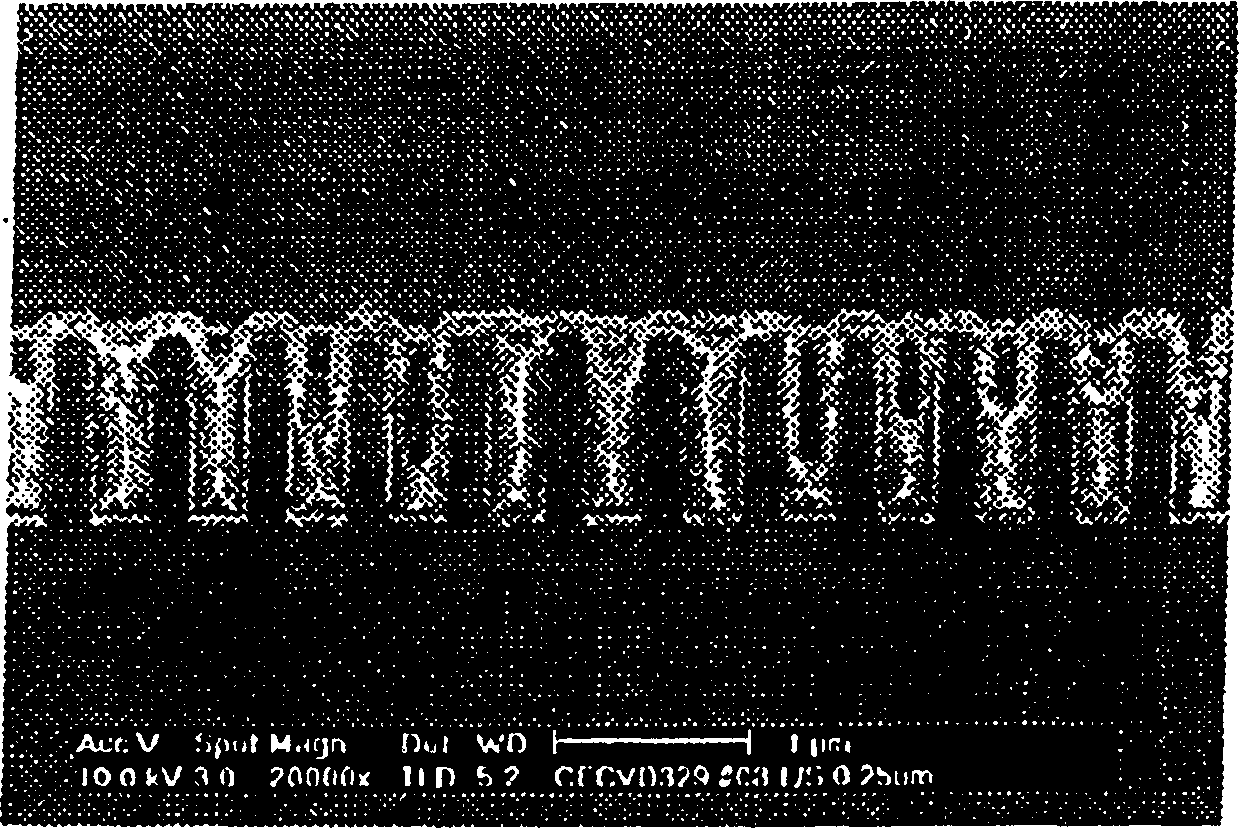

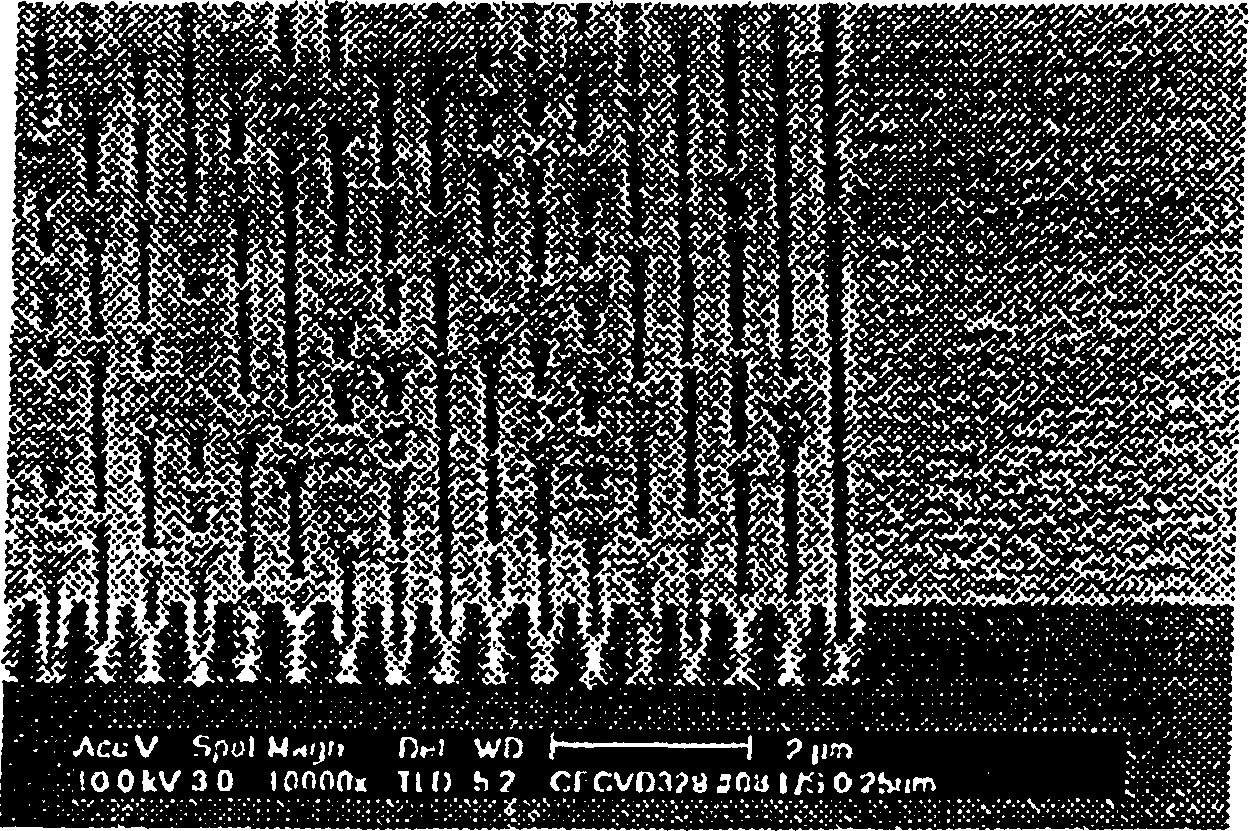

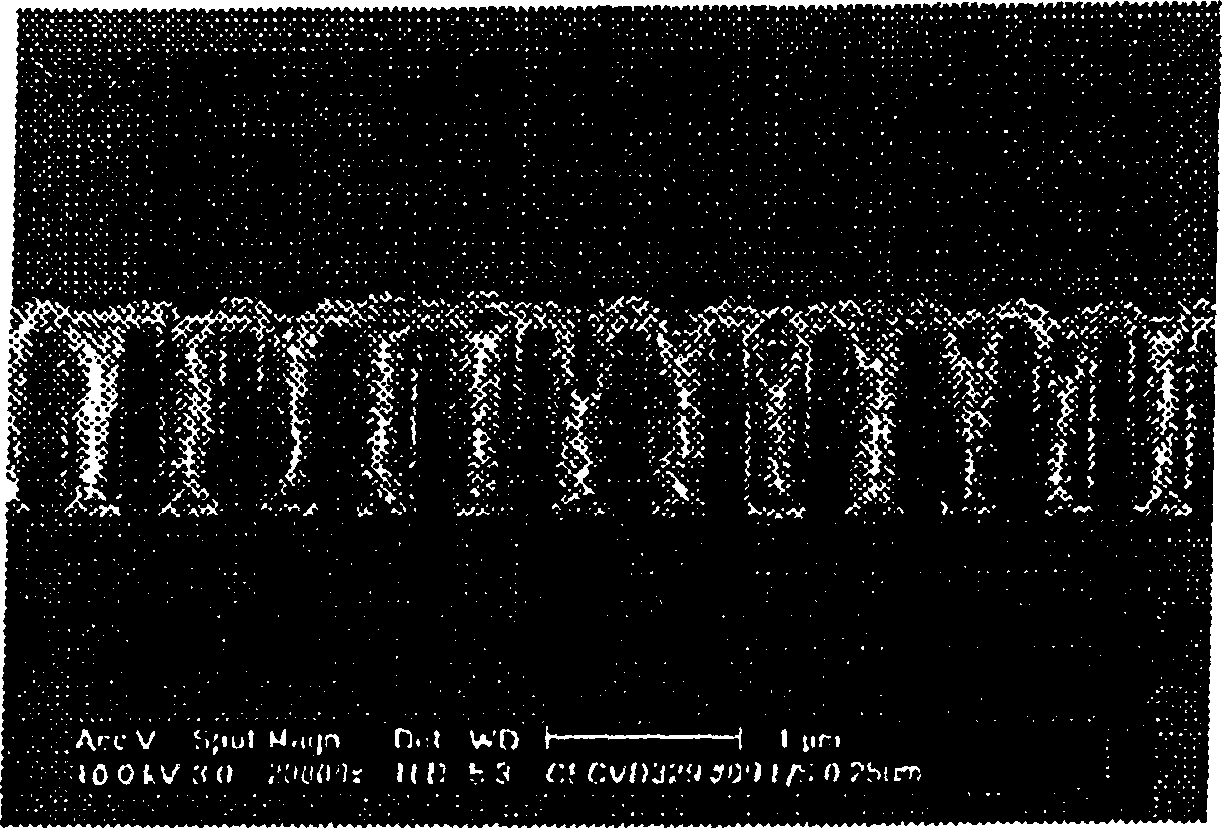

[0018] Reference will now be made in detail to the preferred embodiments of the invention, examples of which are illustrated in the accompanying drawings.

[0019] 3a to 3e are sectional views of a semiconductor device for explaining a method of forming a metal line of a semiconductor device according to the present invention.

[0020] Referring to FIG. 3a, an interlayer insulating layer 12 is formed on a semiconductor substrate 11 having a predetermined structure by using an insulating film of low dielectric constant. A pattern is formed in the interlayer insulating layer 12 by a single damascene method or a dual damascene method to form a damascene pattern. After the rinsing process is performed, on the intermediate insulating layer 12 in which the mosaic pattern is formed, the diffusion barrier layer 13 is formed. When the low-level structures are tungsten (W) and aluminum (Al) structures, the rinsing process is performed with RF plasma. And when the low-order structure i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More