Storage circuit with redundant structure

A memory circuit and redundant memory technology, applied in the field of memory circuits, can solve problems such as selection start timing delay and the like

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 2 example

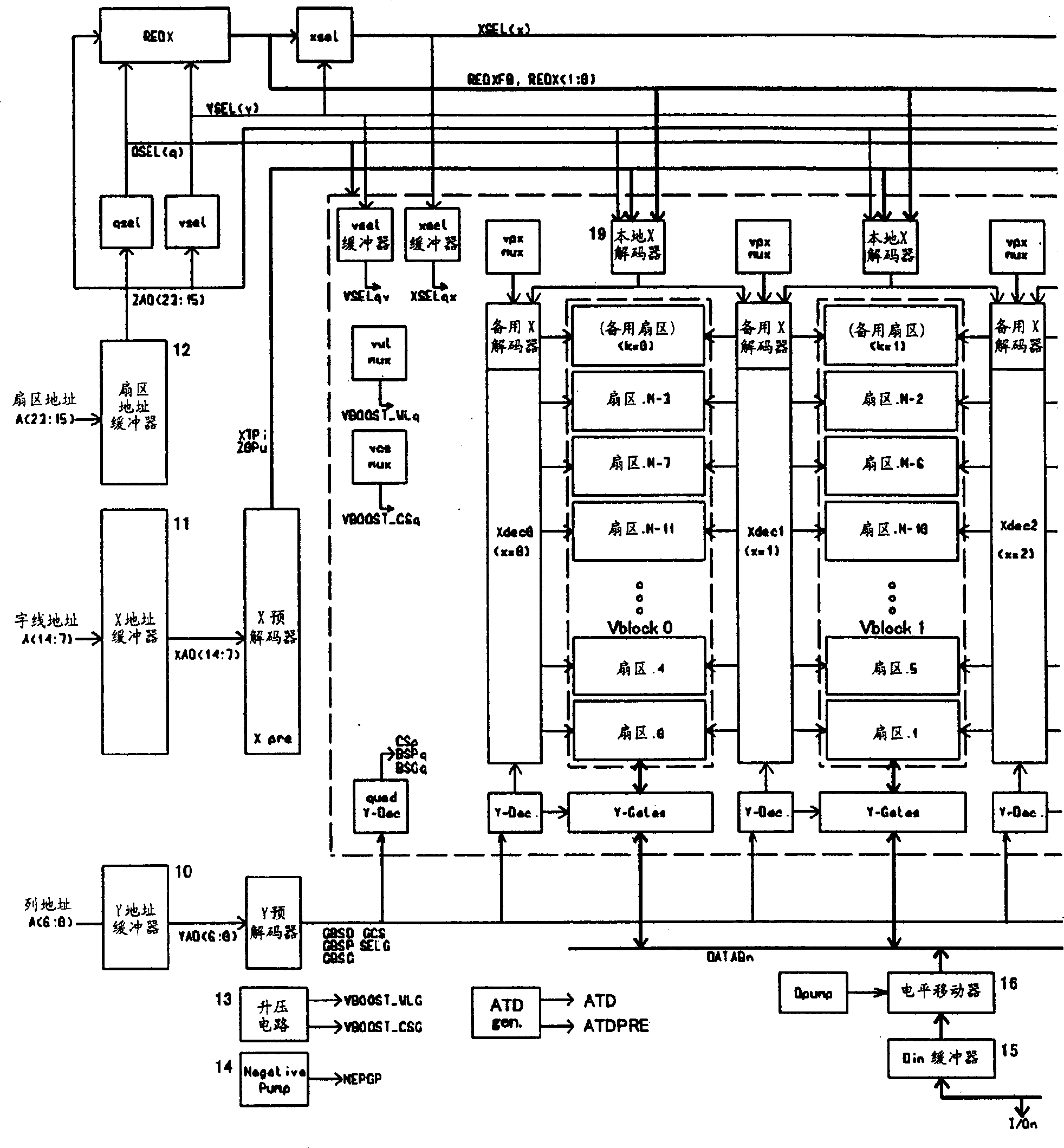

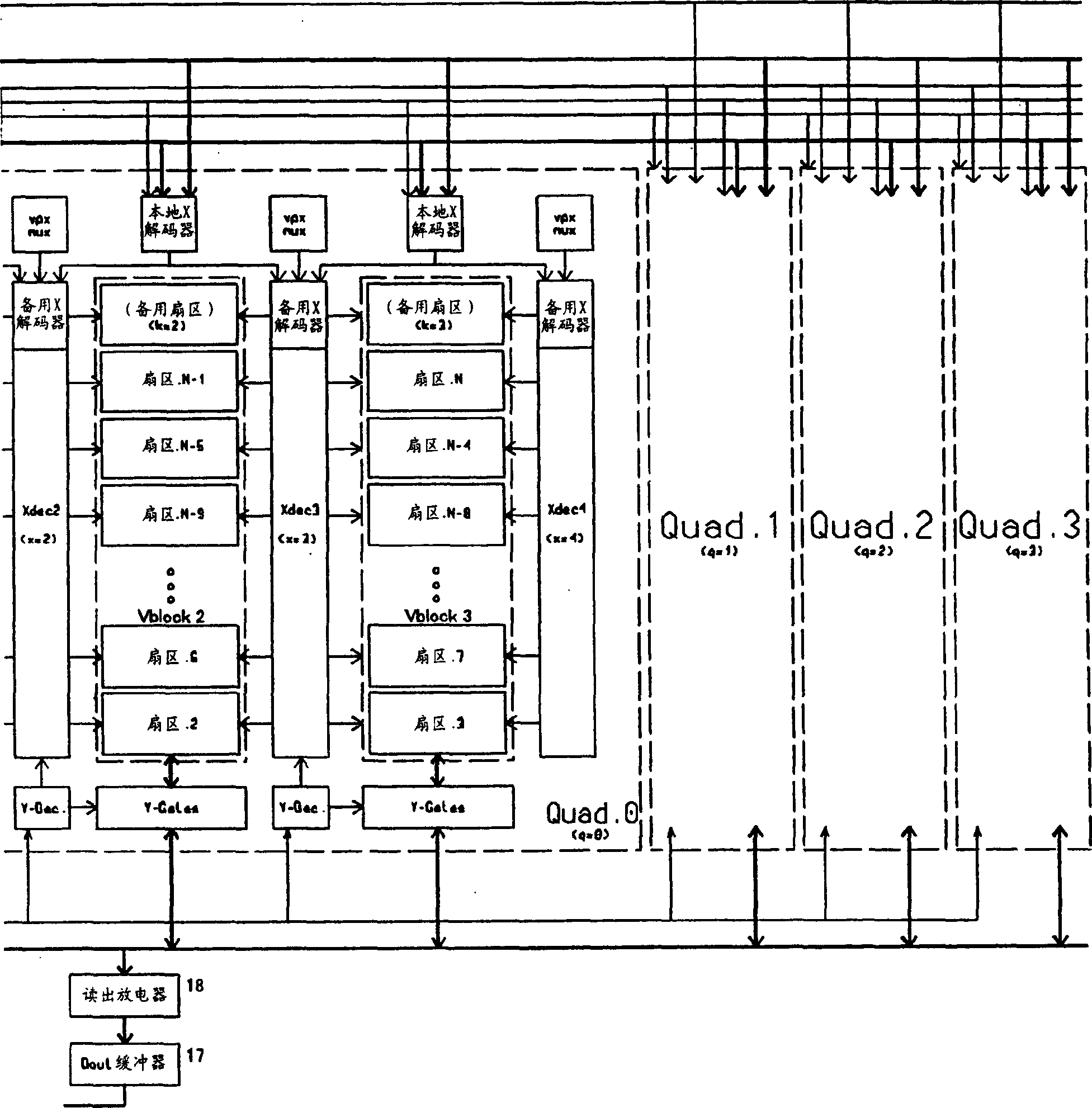

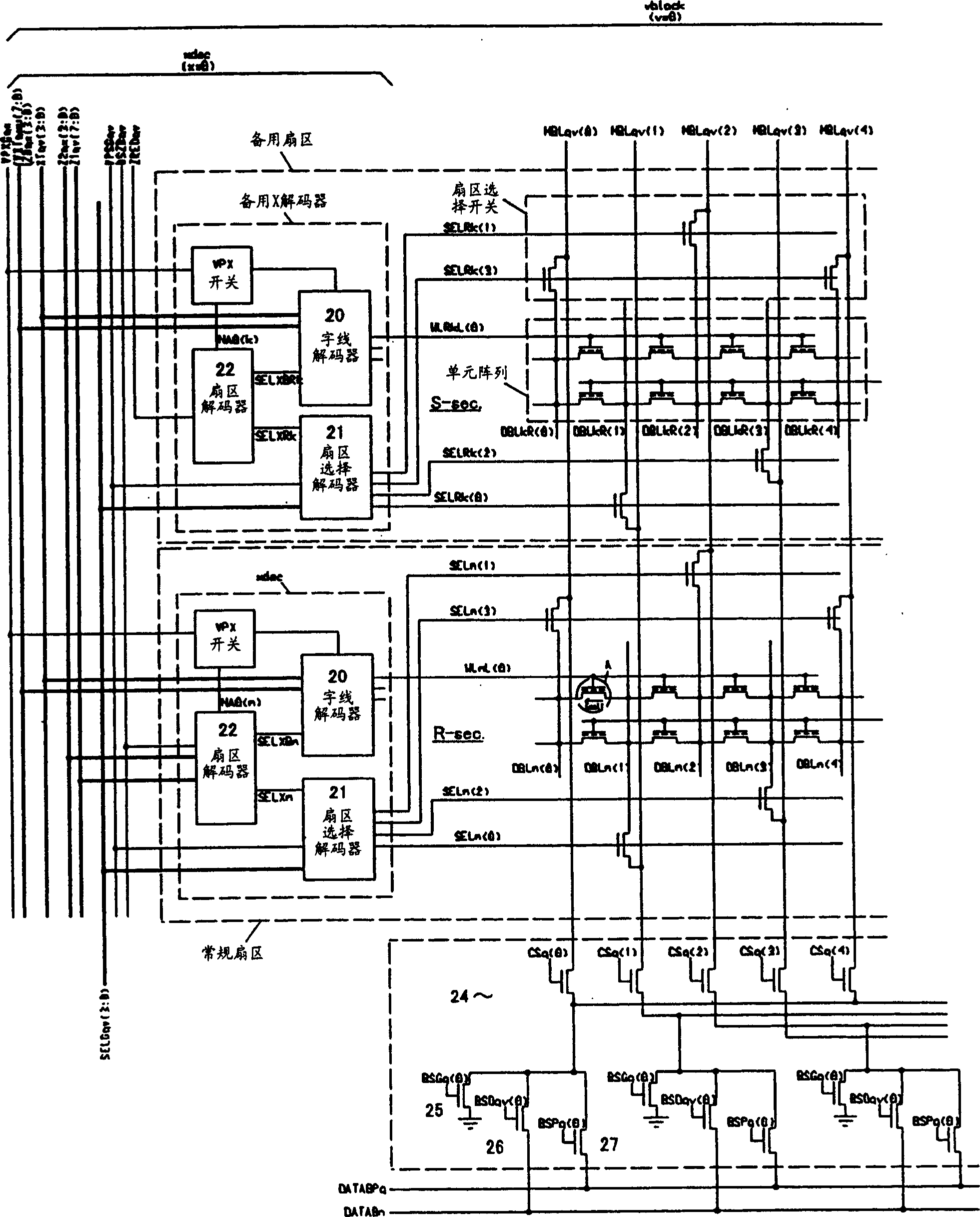

[0100] Next, a second embodiment will be described. The memory circuit of this embodiment also includes a plurality of conventional sectors and spare sectors, as shown in Figures 1, 2 and 3, and further includes a redundancy judgment circuit REDX, as Figure 9 shown in . In response to the test signal TEST (first signal), the redundancy judgment circuit REDX sets the redundancy judgment signal REDXFB to a matching state and enables access to the spare sector regardless of the address in the redundancy memory. For this purpose, AND gates 34, 36 and 38 are provided. Therefore, the other determination signals REDX ( 0 ), ( 1 ) are also forced to be in the matching state, and the simultaneous erase mode disable signal DISFCERB is also forcibly in the matching state (disabled state).

[0101] In addition, in response to the redundancy disable signal DISRED (second signal), the redundancy judgment circuit REDX sets the redundancy judgment signal REDXFB to a mismatch state regardle...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More